|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

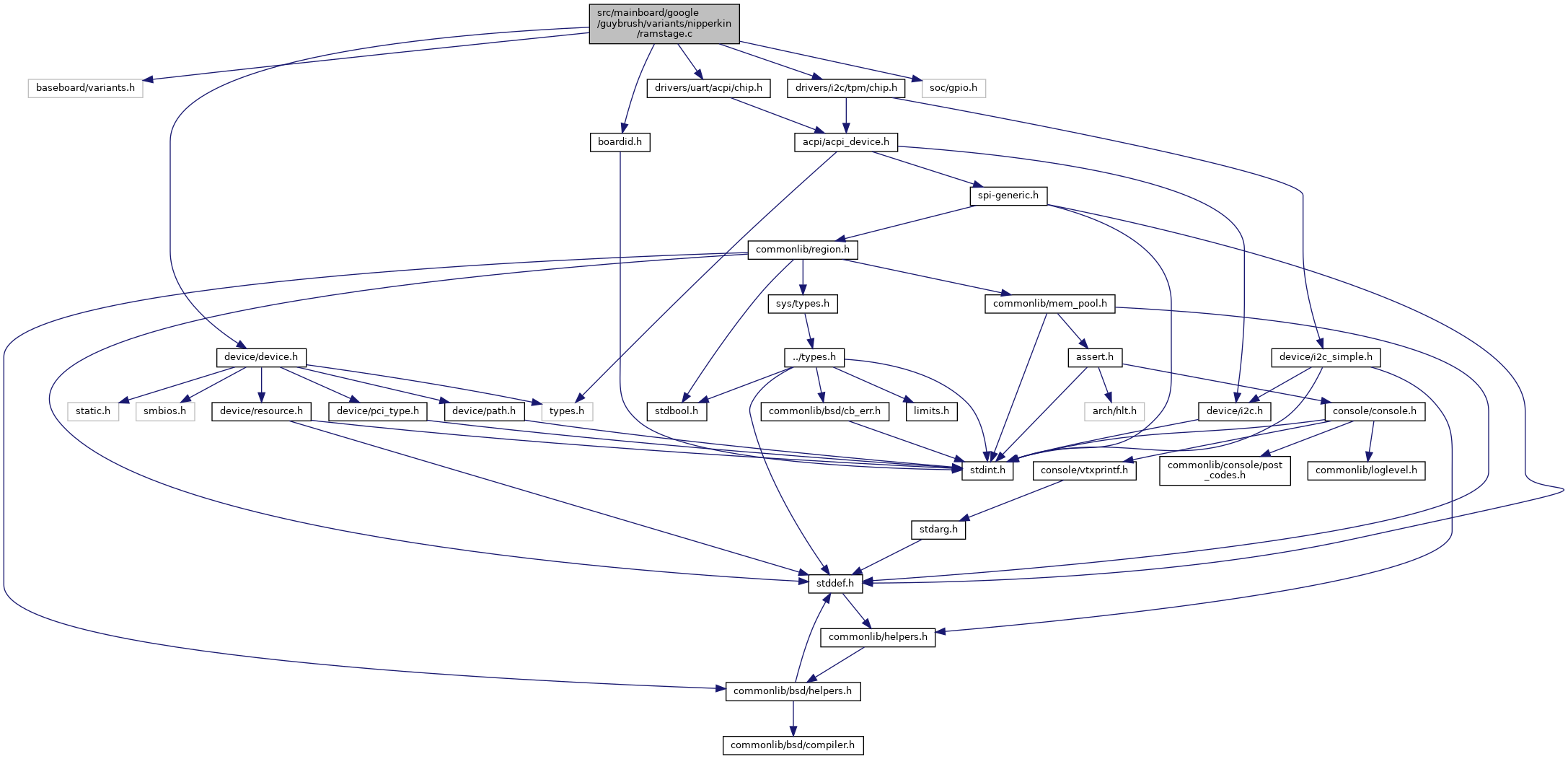

#include <baseboard/variants.h>#include <boardid.h>#include <device/device.h>#include <drivers/i2c/tpm/chip.h>#include <drivers/uart/acpi/chip.h>#include <soc/gpio.h>

Go to the source code of this file.

Functions | |

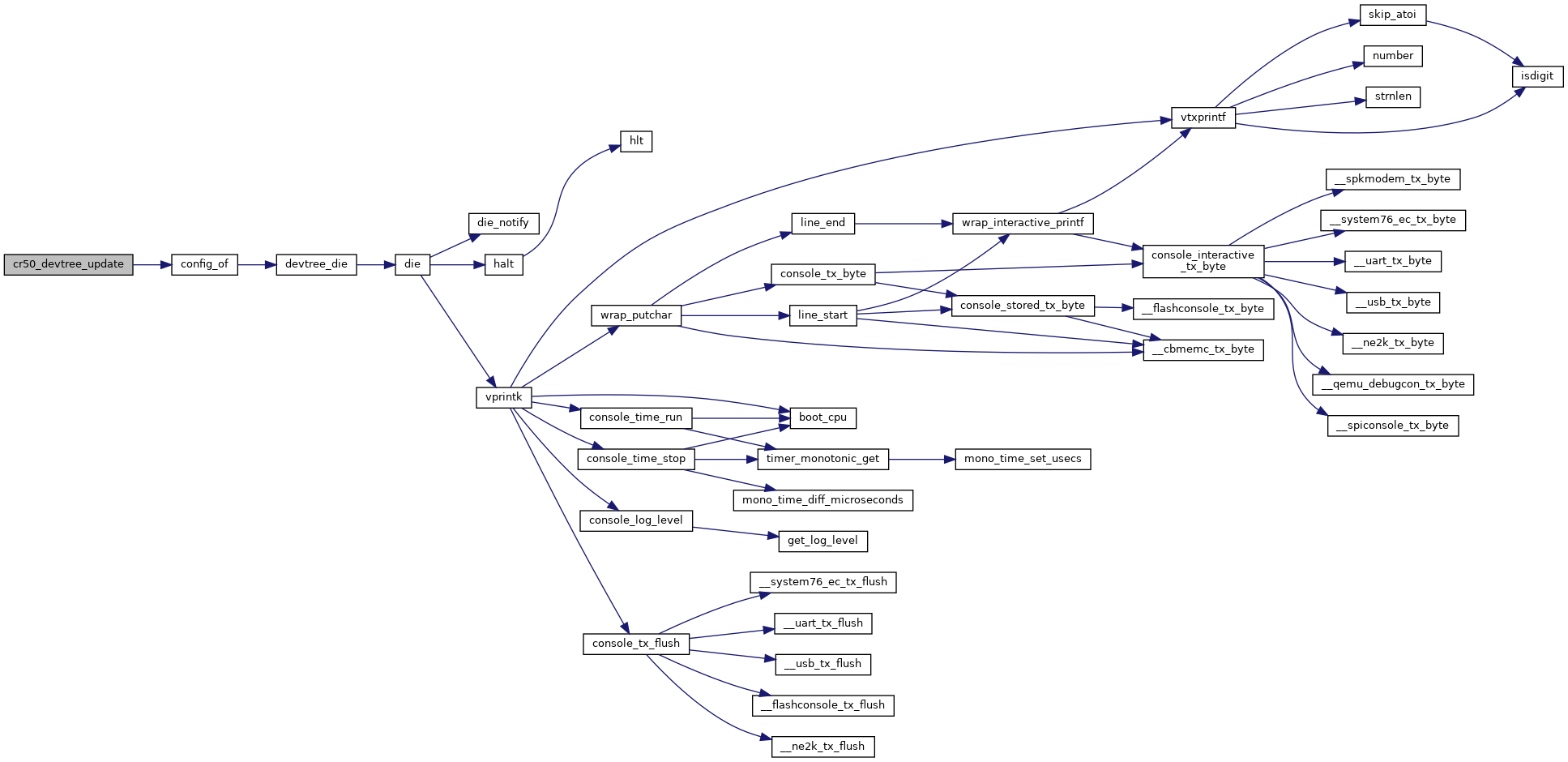

| static void | cr50_devtree_update (void) |

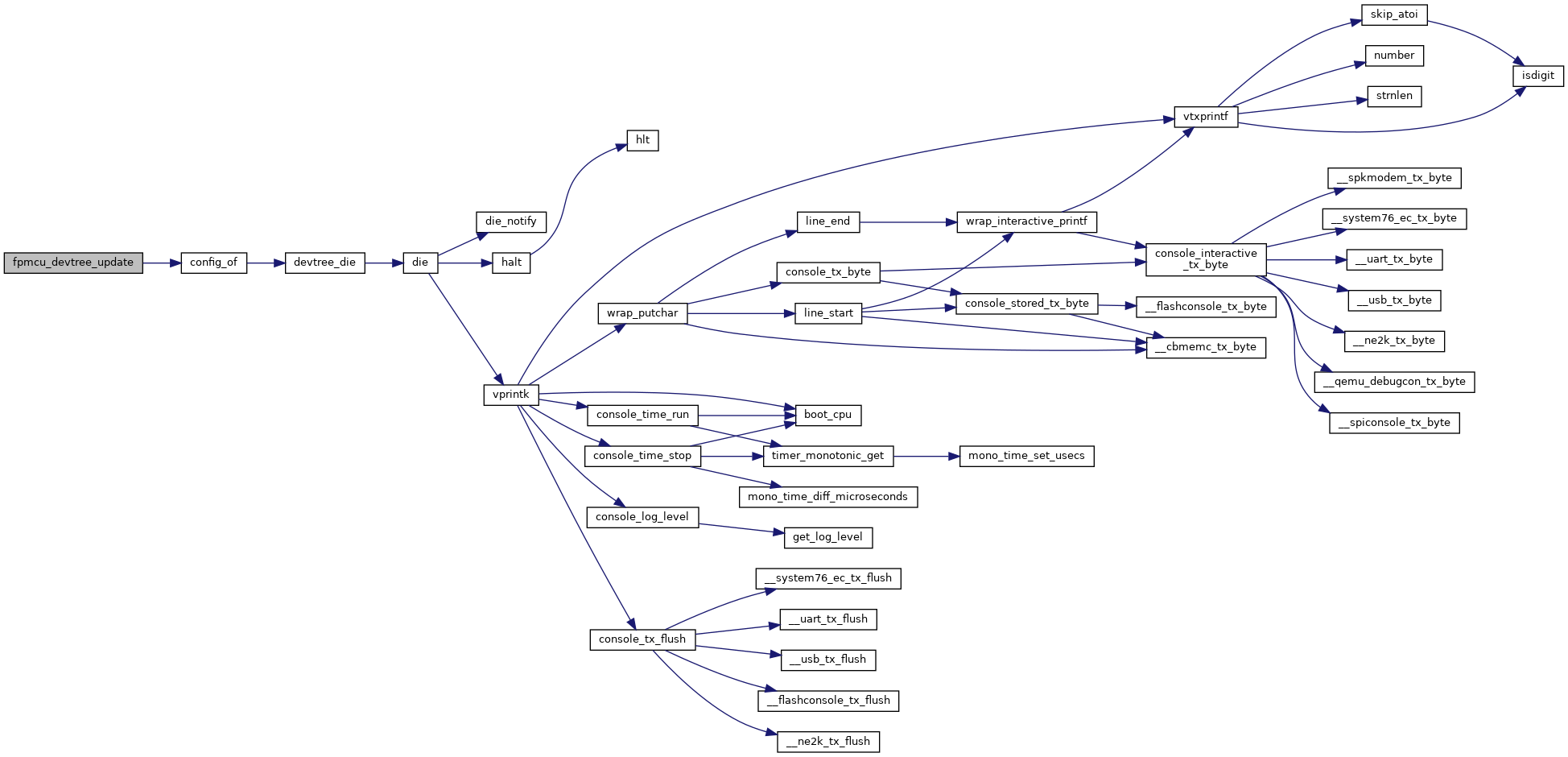

| static void | fpmcu_devtree_update (void) |

| void | variant_devtree_update (void) |

Definition at line 10 of file ramstage.c.

References ACPI_GPIO_IRQ_EDGE_LOW, config_of(), DEV_PTR, GPIO_3, and drivers_i2c_tpm_config::irq_gpio.

Referenced by variant_devtree_update().

Definition at line 20 of file ramstage.c.

References ACPI_GPIO_OUTPUT_ACTIVE_HIGH, config_of(), DEV_PTR, drivers_uart_acpi_config::enable_gpio, and GPIO_32.

Referenced by variant_devtree_update().

Definition at line 30 of file ramstage.c.

References board_id(), cr50_devtree_update(), and fpmcu_devtree_update().