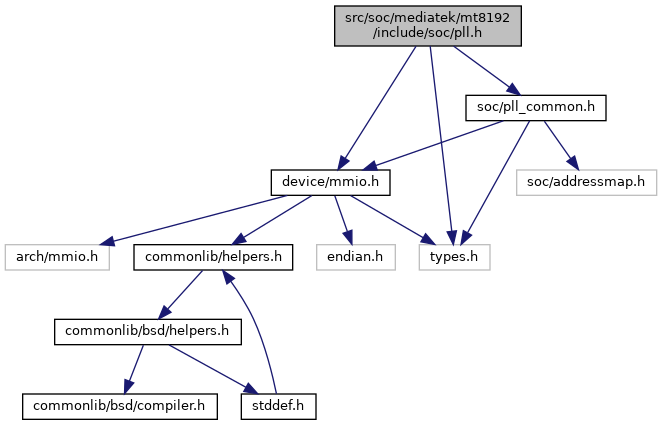

#include <device/mmio.h>

#include <types.h>

#include <soc/pll_common.h>

Go to the source code of this file.

|

| enum | { USBPLL_EN = 0x1 << 2

, PLL_DIV_EN = 0xff << 24

} |

| |

| enum | {

MCU_DIV_MASK = 0x1f << 17

, MCU_DIV_1 = 0x8 << 17

, MCU_MUX_MASK = 0x3 << 9

, MCU_MUX_SRC_PLL = 0x1 << 9

,

MCU_MUX_SRC_DIV_PLL1 = 0x2 << 9

} |

| |

| enum | { PLL_PWR_ON_DELAY = 30

, PLL_ISO_DELAY = 1

, PLL_EN_DELAY = 20

} |

| |

| enum | { PCW_INTEGER_BITS = 8

} |

| |

| enum | {

ARMPLL_LL_HZ = 1075 * MHz

, ARMPLL_BL_HZ = 774 * MHz

, CCIPLL_HZ = 730 * MHz

, MAINPLL_HZ = 2184UL * MHz

,

UNIVPLL_HZ = 2496UL * MHz

, USBPLL_HZ = 192UL * 13 * MHz

, MSDCPLL_HZ = 384 * MHz

, MMPLL_HZ = 2750UL * MHz

,

ADSPPLL_HZ = 750 * MHz

, MFGPLL_HZ = 358 * MHz

, TVDPLL_HZ = 594 * MHz

, APLL1_HZ = 180633600

,

APLL2_HZ = 196608 * KHz

} |

| |

| enum | { CLK26M_HZ = 26 * MHz

, MAINPLL_D5_HZ = MAINPLL_HZ / 5

, MAINPLL_D5_D4_HZ = MAINPLL_D5_HZ / 4

} |

| |

| enum | { SPI_HZ = MAINPLL_D5_D4_HZ

, UART_HZ = CLK26M_HZ

} |

| |

| enum | {

INFRACFG_AO_AXIMEM_BUS_DCM_REG0_MASK = (0x1f << 12) | (0x1 << 17) | (0x1 << 18)

, INFRACFG_AO_AXIMEM_BUS_DCM_REG0_ON = (0x10 << 12) | (0x1 << 17) | (0x0 << 18)

, INFRACFG_AO_INFRA_BUS_DCM_REG0_MASK

, INFRACFG_AO_INFRA_BUS_DCM_REG0_ON

,

INFRACFG_AO_INFRA_CONN_BUS_DCM_REG0_MASK = (0x1 << 8)

, INFRACFG_AO_INFRA_CONN_BUS_DCM_REG0_ON = (0x1 << 8)

, INFRACFG_AO_INFRA_CONN_BUS_DCM_REG1_MASK = (0x1 << 8)

, INFRACFG_AO_INFRA_CONN_BUS_DCM_REG1_ON = (0x0 << 8)

,

INFRACFG_AO_INFRA_RX_P2P_DCM_REG0_MASK = (0xf << 0)

, INFRACFG_AO_INFRA_RX_P2P_DCM_REG0_ON = (0x0 << 0)

, INFRACFG_AO_PERI_BUS_DCM_REG0_MASK

, INFRACFG_AO_PERI_BUS_DCM_REG0_ON

,

INFRACFG_AO_PERI_MODULE_DCM_REG0_MASK = (0x1 << 29) | (0x1 << 31)

, INFRACFG_AO_PERI_MODULE_DCM_REG0_ON = (0x1 << 29) | (0x1 << 31)

} |

| |

|

| | check_member (mtk_topckgen_regs, clk_misc_cfg_0, 0x0140) |

| |

| | check_member (mtk_topckgen_regs, clk_misc_cfg_1, 0x0150) |

| |

| | check_member (mtk_topckgen_regs, clk_dbg_cfg, 0x017c) |

| |

| | check_member (mtk_topckgen_regs, clk_scp_cfg_0, 0x0200) |

| |

| | check_member (mtk_topckgen_regs, clk_scp_cfg_1, 0x0210) |

| |

| | check_member (mtk_topckgen_regs, clk26cali_0, 0x0220) |

| |

| | check_member (mtk_topckgen_regs, cksta_reg, 0x0230) |

| |

| | check_member (mtk_topckgen_regs, clkmon_clk_sel_reg, 0x0300) |

| |

| | check_member (mtk_topckgen_regs, clk_auddiv_0, 0x0320) |

| |

| | check_member (mtk_topckgen_regs, clk_extck_reg, 0x0500) |

| |

| | check_member (mtk_apmixed_regs, ap_pllgp1_con0, 0x0200) |

| |

| | check_member (mtk_apmixed_regs, ap_pllgp2_con0, 0x0300) |

| |

| | check_member (mtk_apmixed_regs, usbpll_con2, 0x03cc) |

| |

◆ MPLL_CON1_FREQ

| #define MPLL_CON1_FREQ 0x84200000 |

◆ anonymous enum

| Enumerator |

|---|

| USBPLL_EN | |

| PLL_DIV_EN | |

Definition at line 246 of file pll.h.

◆ anonymous enum

| Enumerator |

|---|

| MCU_DIV_MASK | |

| MCU_DIV_1 | |

| MCU_MUX_MASK | |

| MCU_MUX_SRC_PLL | |

| MCU_MUX_SRC_DIV_PLL1 | |

Definition at line 252 of file pll.h.

◆ anonymous enum

| Enumerator |

|---|

| PLL_PWR_ON_DELAY | |

| PLL_ISO_DELAY | |

| PLL_EN_DELAY | |

Definition at line 261 of file pll.h.

◆ anonymous enum

| Enumerator |

|---|

| PCW_INTEGER_BITS | |

Definition at line 267 of file pll.h.

◆ anonymous enum

| Enumerator |

|---|

| ARMPLL_LL_HZ | |

| ARMPLL_BL_HZ | |

| CCIPLL_HZ | |

| MAINPLL_HZ | |

| UNIVPLL_HZ | |

| USBPLL_HZ | |

| MSDCPLL_HZ | |

| MMPLL_HZ | |

| ADSPPLL_HZ | |

| MFGPLL_HZ | |

| TVDPLL_HZ | |

| APLL1_HZ | |

| APLL2_HZ | |

Definition at line 272 of file pll.h.

◆ anonymous enum

| Enumerator |

|---|

| CLK26M_HZ | |

| MAINPLL_D5_HZ | |

| MAINPLL_D5_D4_HZ | |

Definition at line 289 of file pll.h.

◆ anonymous enum

◆ anonymous enum

| Enumerator |

|---|

| INFRACFG_AO_AXIMEM_BUS_DCM_REG0_MASK | |

| INFRACFG_AO_AXIMEM_BUS_DCM_REG0_ON | |

| INFRACFG_AO_INFRA_BUS_DCM_REG0_MASK | |

| INFRACFG_AO_INFRA_BUS_DCM_REG0_ON | |

| INFRACFG_AO_INFRA_CONN_BUS_DCM_REG0_MASK | |

| INFRACFG_AO_INFRA_CONN_BUS_DCM_REG0_ON | |

| INFRACFG_AO_INFRA_CONN_BUS_DCM_REG1_MASK | |

| INFRACFG_AO_INFRA_CONN_BUS_DCM_REG1_ON | |

| INFRACFG_AO_INFRA_RX_P2P_DCM_REG0_MASK | |

| INFRACFG_AO_INFRA_RX_P2P_DCM_REG0_ON | |

| INFRACFG_AO_PERI_BUS_DCM_REG0_MASK | |

| INFRACFG_AO_PERI_BUS_DCM_REG0_ON | |

| INFRACFG_AO_PERI_MODULE_DCM_REG0_MASK | |

| INFRACFG_AO_PERI_MODULE_DCM_REG0_ON | |

Definition at line 320 of file pll.h.

◆ check_member() [1/13]

◆ check_member() [2/13]

◆ check_member() [3/13]

◆ check_member() [4/13]

◆ check_member() [5/13]

◆ check_member() [6/13]

◆ check_member() [7/13]

◆ check_member() [8/13]

◆ check_member() [9/13]

◆ check_member() [10/13]

◆ check_member() [11/13]

◆ check_member() [12/13]

◆ check_member() [13/13]