|

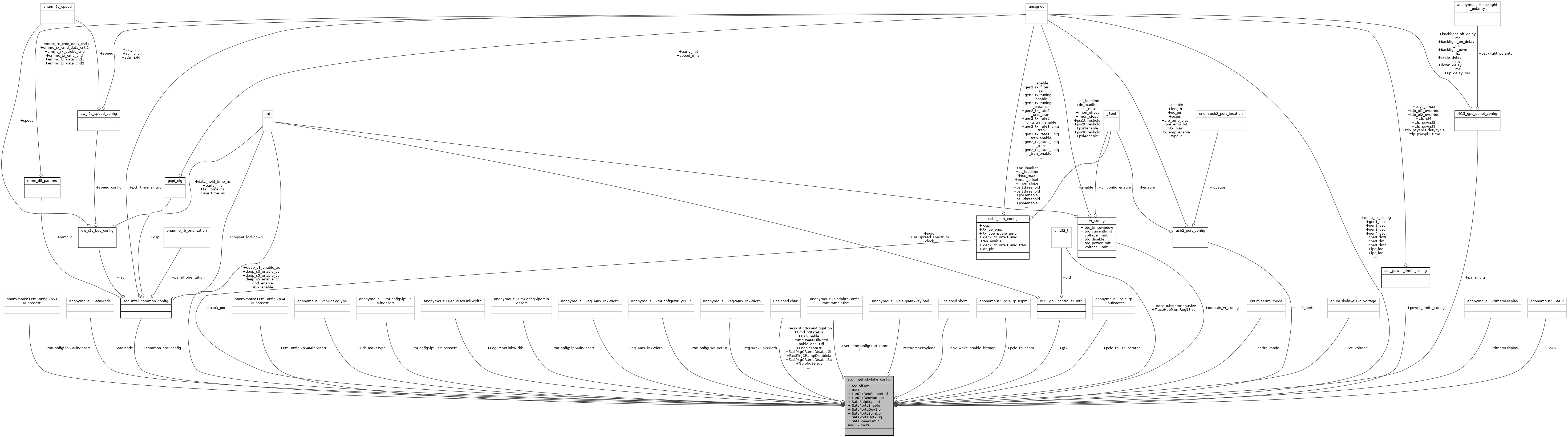

| enum | { SaGv_Disabled

, SaGv_FixedLow

, SaGv_FixedHigh

, SaGv_Enabled

} |

| |

| enum | { SATA_AHCI = 0

, SATA_RAID = 1

} |

| |

| enum | { Vc0

, Vc1

} |

| |

| enum | {

Peg0_x16

, Peg0_x1

, Peg0_x2

, Peg0_x4

,

Peg0_x8

} |

| |

| enum | { Peg1_x8

, Peg1_x1

, Peg1_x2

, Peg1_x4

} |

| |

| enum | { Peg2_x4

, Peg2_x1

, Peg2_x2

} |

| |

| enum | { RpMaxPayload_128

, RpMaxPayload_256

} |

| |

| enum | {

AspmDefault

, AspmDisabled

, AspmL0s

, AspmL1

,

AspmL0sL1

, AspmAutoConfig

} |

| |

| enum | { L1SS_Default

, L1SS_Disabled

, L1SS_L1_1

, L1SS_L1_2

} |

| |

| enum | {

Display_iGFX

, Display_PEG

, Display_PCH_PCIe

, Display_Auto

,

Display_Switchable

} |

| |

| enum | { SLP_S3_MIN_ASSERT_60US = 0

, SLP_S3_MIN_ASSERT_1MS = 1

, SLP_S3_MIN_ASSERT_50MS = 2

, SLP_S3_MIN_ASSERT_2S = 3

} |

| |

| enum | {

SLP_S4_MIN_ASSERT_PCH = 0

, SLP_S4_MIN_ASSERT_1S = 1

, SLP_S4_MIN_ASSERT_2S = 2

, SLP_S4_MIN_ASSERT_3S = 3

,

SLP_S4_MIN_ASSERT_4S = 4

} |

| |

| enum | { SLP_SUS_MIN_ASSERT_0MS = 0

, SLP_SUS_MIN_ASSERT_500MS = 1

, SLP_SUS_MIN_ASSERT_1S = 2

, SLP_SUS_MIN_ASSERT_4S = 3

} |

| |

| enum | { SLP_A_MIN_ASSERT_0MS = 0

, SLP_A_MIN_ASSERT_4S = 1

, SLP_A_MIN_ASSERT_98MS = 2

, SLP_A_MIN_ASSERT_2S = 3

} |

| |

| enum | {

RESET_POWER_CYCLE_DEFAULT = 0

, RESET_POWER_CYCLE_1S = 1

, RESET_POWER_CYCLE_2S = 2

, RESET_POWER_CYCLE_3S = 3

,

RESET_POWER_CYCLE_4S = 4

} |

| |

| enum | { SERIAL_IRQ_FRAME_PULSE_4CLK = 0

, SERIAL_IRQ_FRAME_PULSE_6CLK = 1

, SERIAL_IRQ_FRAME_PULSE_8CLK = 2

} |

| |

Definition at line 31 of file chip.h.