|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

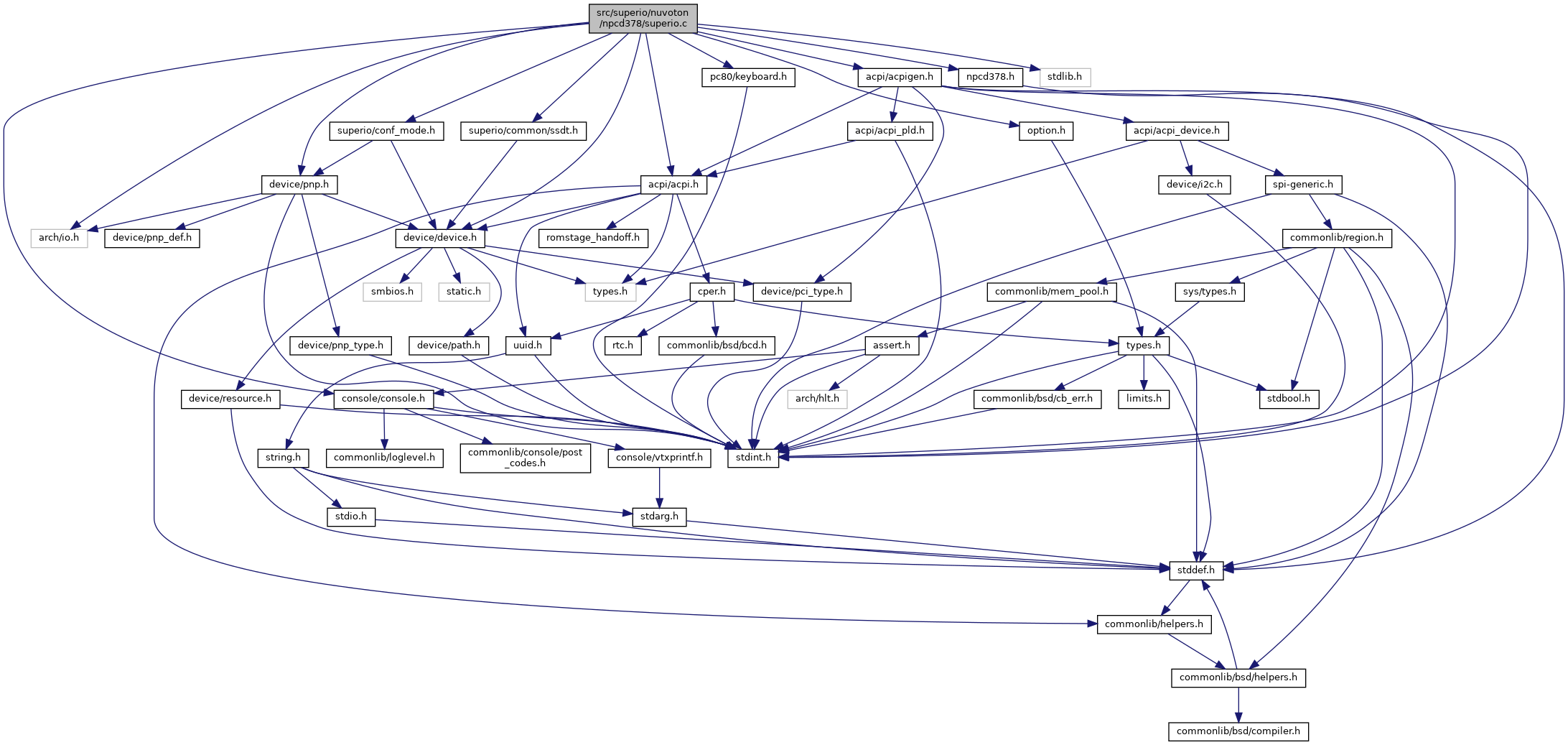

#include <arch/io.h>#include <console/console.h>#include <device/device.h>#include <device/pnp.h>#include <option.h>#include <pc80/keyboard.h>#include <superio/conf_mode.h>#include <acpi/acpi.h>#include <acpi/acpigen.h>#include <superio/common/ssdt.h>#include <stdlib.h>#include "npcd378.h"

Go to the source code of this file.

Functions | |

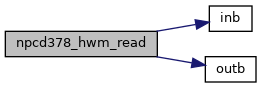

| uint8_t | npcd378_hwm_read (const uint16_t iobase, const uint16_t reg) |

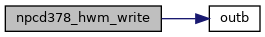

| void | npcd378_hwm_write (const uint16_t iobase, const uint16_t reg, const uint8_t val) |

| void | npcd378_hwm_write_start (const uint16_t iobase) |

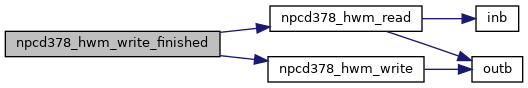

| void | npcd378_hwm_write_finished (const uint16_t iobase) |

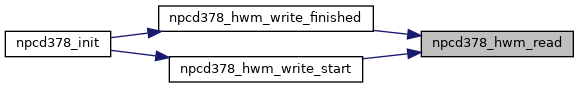

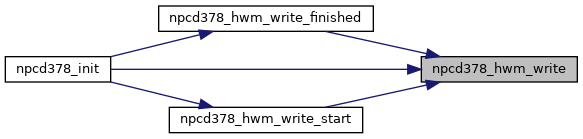

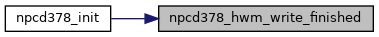

| static void | npcd378_init (struct device *dev) |

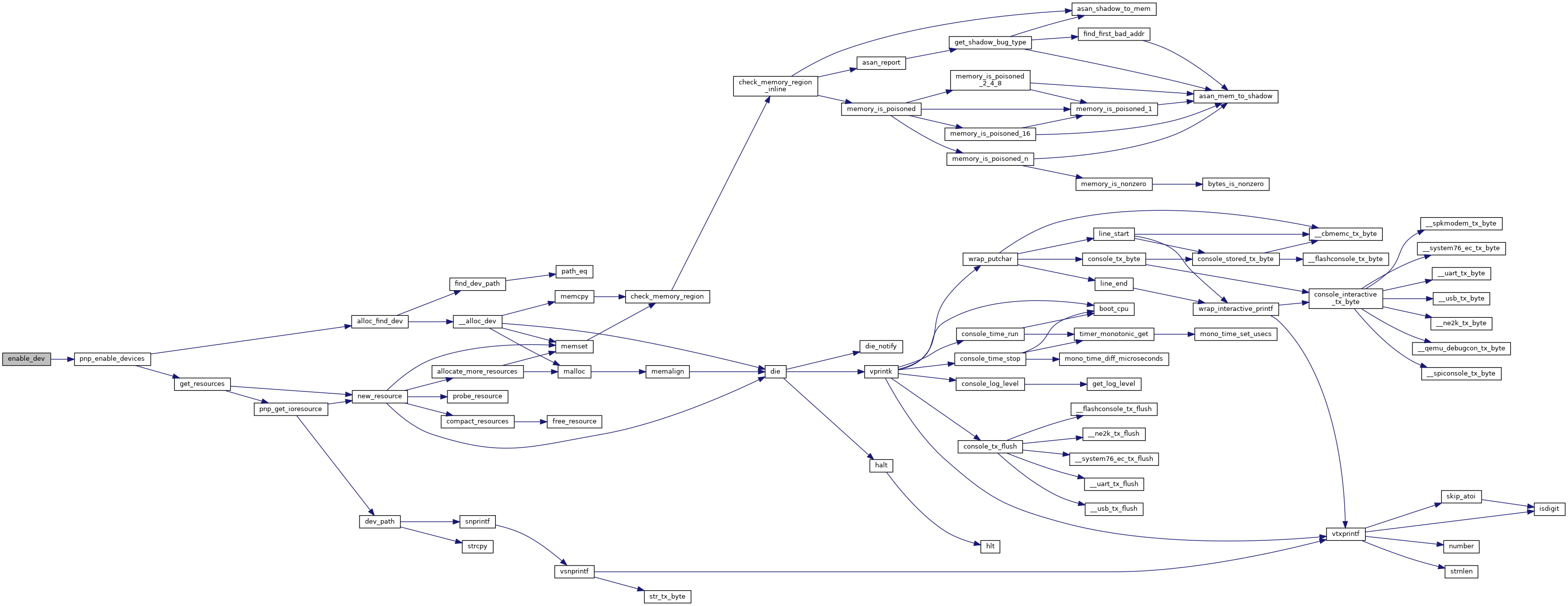

| static void | enable_dev (struct device *dev) |

Variables | |

| static struct device_operations | ops |

| static struct pnp_info | pnp_dev_info [] |

| struct chip_operations | superio_nuvoton_npcd378_ops |

Definition at line 470 of file superio.c.

References ARRAY_SIZE, ops, pnp_dev_info, and pnp_enable_devices().

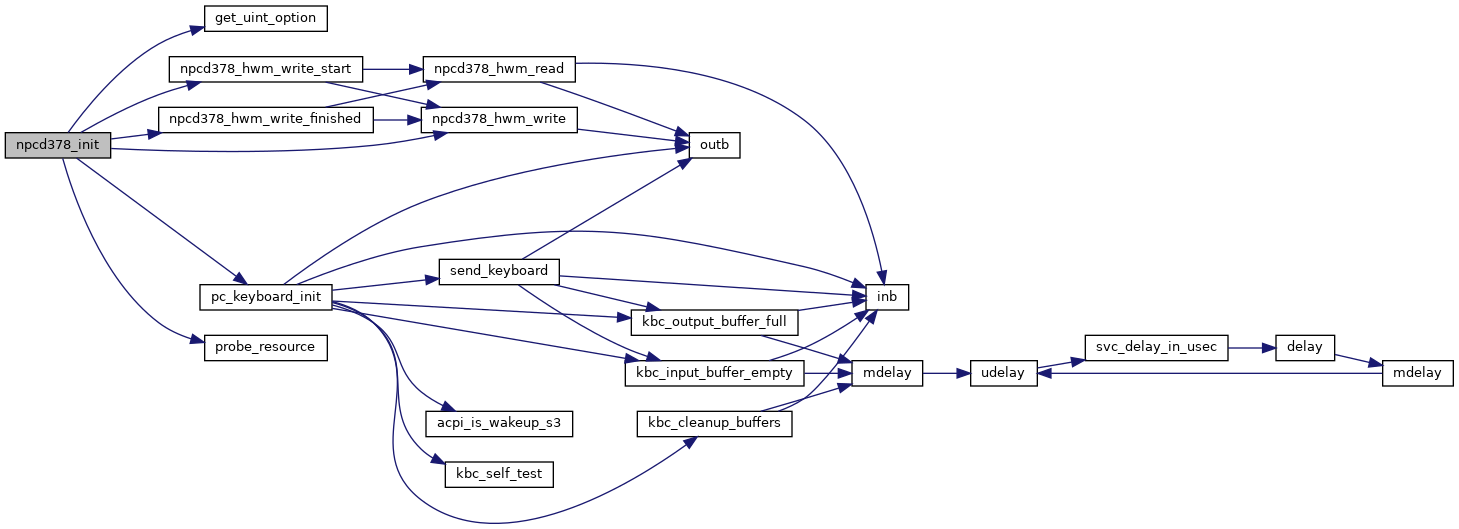

Definition at line 17 of file superio.c.

Referenced by npcd378_hwm_write_finished(), and npcd378_hwm_write_start().

Definition at line 28 of file superio.c.

Referenced by npcd378_hwm_write_finished(), npcd378_hwm_write_start(), and npcd378_init().

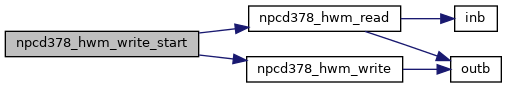

Definition at line 43 of file superio.c.

References npcd378_hwm_read(), npcd378_hwm_write(), NPCD837_HWM_WRITE_LOCK_BIT, and NPCD837_HWM_WRITE_LOCK_CTRL.

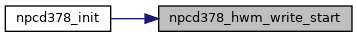

Referenced by npcd378_init().

Definition at line 36 of file superio.c.

References npcd378_hwm_read(), npcd378_hwm_write(), NPCD837_HWM_WRITE_LOCK_BIT, and NPCD837_HWM_WRITE_LOCK_CTRL.

Referenced by npcd378_init().

Definition at line 50 of file superio.c.

References resource::base, BIOS_ERR, BIOS_INFO, pnp_path::device, device::enabled, get_uint_option(), NPCD378_HWM, NPCD378_HWM_PSU_FAN_MAX, NPCD378_HWM_PSU_FAN_MIN, NPCD378_HWM_PSU_FAN_PWM_CTRL, npcd378_hwm_write(), npcd378_hwm_write_finished(), npcd378_hwm_write_start(), NPCD378_KBC, device::path, pc_keyboard_init(), device_path::pnp, PNP_IDX_IO0, printk, PROBE_AUX_DEVICE, and probe_resource().

|

static |

Definition at line 50 of file superio.c.

Referenced by enable_dev().

|

static |

Definition at line 50 of file superio.c.

Referenced by enable_dev().

| struct chip_operations superio_nuvoton_npcd378_ops |