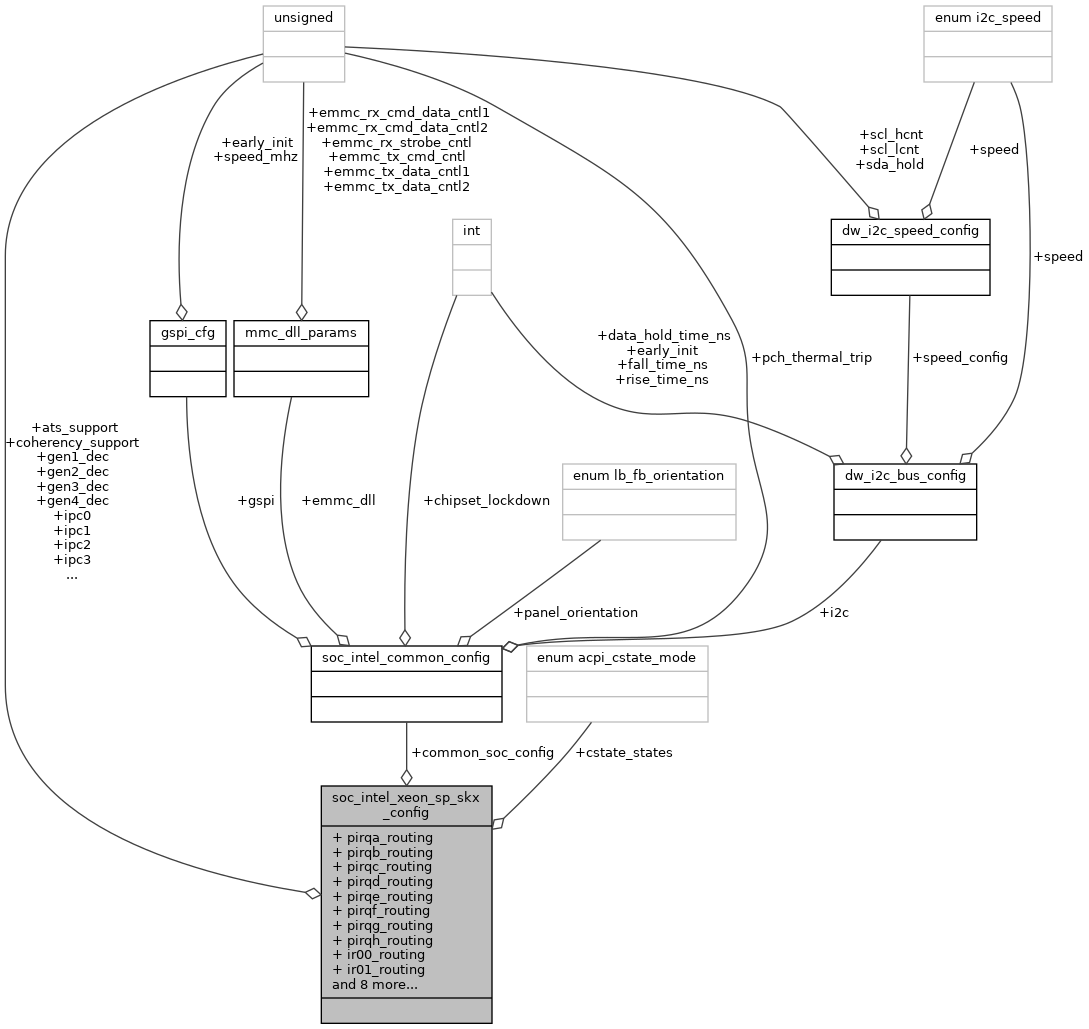

#include <chip.h>

Definition at line 12 of file chip.h.

◆ ats_support

| uint32_t soc_intel_xeon_sp_skx_config::ats_support |

◆ coherency_support

| uint32_t soc_intel_xeon_sp_skx_config::coherency_support |

◆ common_soc_config

Definition at line 1 of file chip.h.

◆ cstate_states

◆ gen1_dec

| uint32_t soc_intel_xeon_sp_skx_config::gen1_dec |

◆ gen2_dec

| uint32_t soc_intel_xeon_sp_skx_config::gen2_dec |

◆ gen3_dec

| uint32_t soc_intel_xeon_sp_skx_config::gen3_dec |

◆ gen4_dec

| uint32_t soc_intel_xeon_sp_skx_config::gen4_dec |

◆ ipc0

| uint32_t soc_intel_xeon_sp_skx_config::ipc0 |

Device Interrupt Polarity Control ipc0 - IRQ-00-31 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc1 - IRQ-32-63 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc2 - IRQ-64-95 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc3 - IRQ-96-119 - 1: Active low to IOAPIC, 0: Active high to IOAPIC.

Definition at line 55 of file chip.h.

◆ ipc1

| uint32_t soc_intel_xeon_sp_skx_config::ipc1 |

◆ ipc2

| uint32_t soc_intel_xeon_sp_skx_config::ipc2 |

◆ ipc3

| uint32_t soc_intel_xeon_sp_skx_config::ipc3 |

◆ ir00_routing

| uint16_t soc_intel_xeon_sp_skx_config::ir00_routing |

Device Interrupt Routing configuration Interrupt Pin x Route.

0h = PIRQA# 1h = PIRQB# 2h = PIRQC# 3h = PIRQD# 4h = PIRQE# 5h = PIRQF# 6h = PIRQG# 7h = PIRQH#

Definition at line 42 of file chip.h.

◆ ir01_routing

| uint16_t soc_intel_xeon_sp_skx_config::ir01_routing |

◆ ir02_routing

| uint16_t soc_intel_xeon_sp_skx_config::ir02_routing |

◆ ir03_routing

| uint16_t soc_intel_xeon_sp_skx_config::ir03_routing |

◆ ir04_routing

| uint16_t soc_intel_xeon_sp_skx_config::ir04_routing |

◆ pirqa_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqa_routing |

Interrupt Routing configuration If bit7 is 1, the interrupt is disabled.

Definition at line 20 of file chip.h.

◆ pirqb_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqb_routing |

◆ pirqc_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqc_routing |

◆ pirqd_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqd_routing |

◆ pirqe_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqe_routing |

◆ pirqf_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqf_routing |

◆ pirqg_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqg_routing |

◆ pirqh_routing

| uint8_t soc_intel_xeon_sp_skx_config::pirqh_routing |

◆ pstate_req_ratio

| uint32_t soc_intel_xeon_sp_skx_config::pstate_req_ratio |

◆ tcc_offset

| uint32_t soc_intel_xeon_sp_skx_config::tcc_offset |

◆ turbo_ratio_limit

| uint64_t soc_intel_xeon_sp_skx_config::turbo_ratio_limit |

◆ turbo_ratio_limit_cores

| uint64_t soc_intel_xeon_sp_skx_config::turbo_ratio_limit_cores |

◆ vtd_support

| uint32_t soc_intel_xeon_sp_skx_config::vtd_support |

The documentation for this struct was generated from the following file:

- src/soc/intel/xeon_sp/skx/chip.h