|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

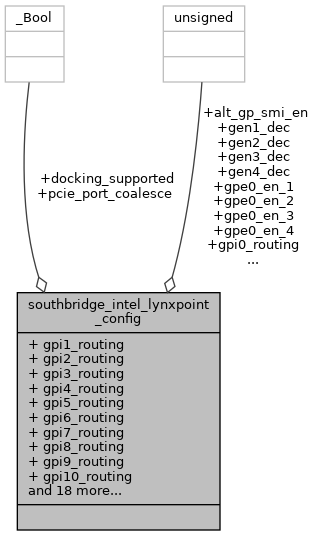

#include <chip.h>

| bool southbridge_intel_lynxpoint_config::docking_supported |

Definition at line 91 of file chip.h.

Referenced by acpi_fill_fadt().

| uint8_t southbridge_intel_lynxpoint_config::gpi0_routing |

| uint32_t southbridge_intel_lynxpoint_config::icc_clock_disable |

| uint8_t southbridge_intel_lynxpoint_config::pcie_port_force_aspm |

| uint8_t southbridge_intel_lynxpoint_config::sata_devslp_disable |

| uint32_t southbridge_intel_lynxpoint_config::sata_port0_gen3_dtle |

| uint32_t southbridge_intel_lynxpoint_config::sata_port0_gen3_tx |

| uint32_t southbridge_intel_lynxpoint_config::sata_port1_gen3_dtle |

| uint32_t southbridge_intel_lynxpoint_config::sata_port1_gen3_tx |