|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

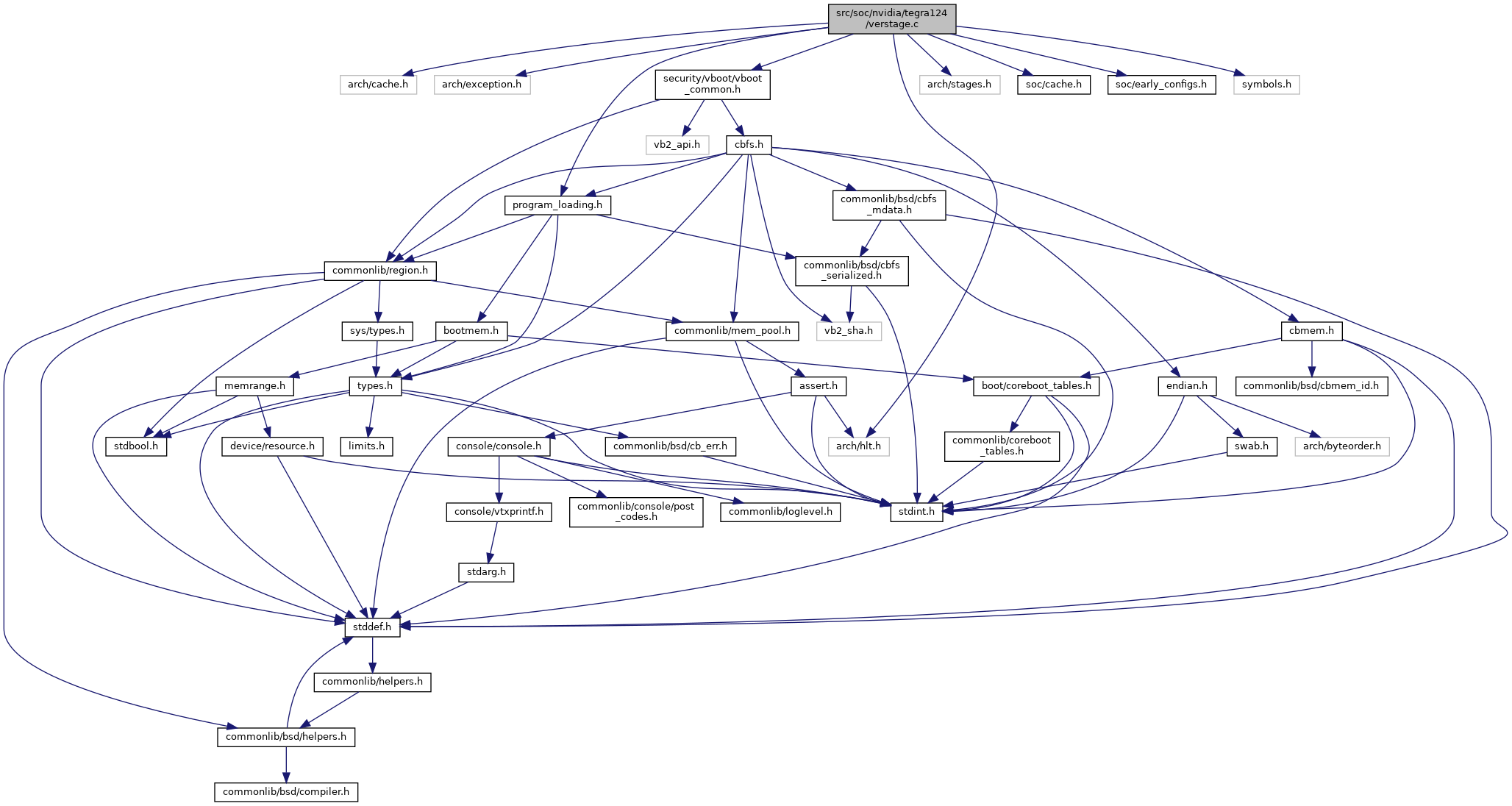

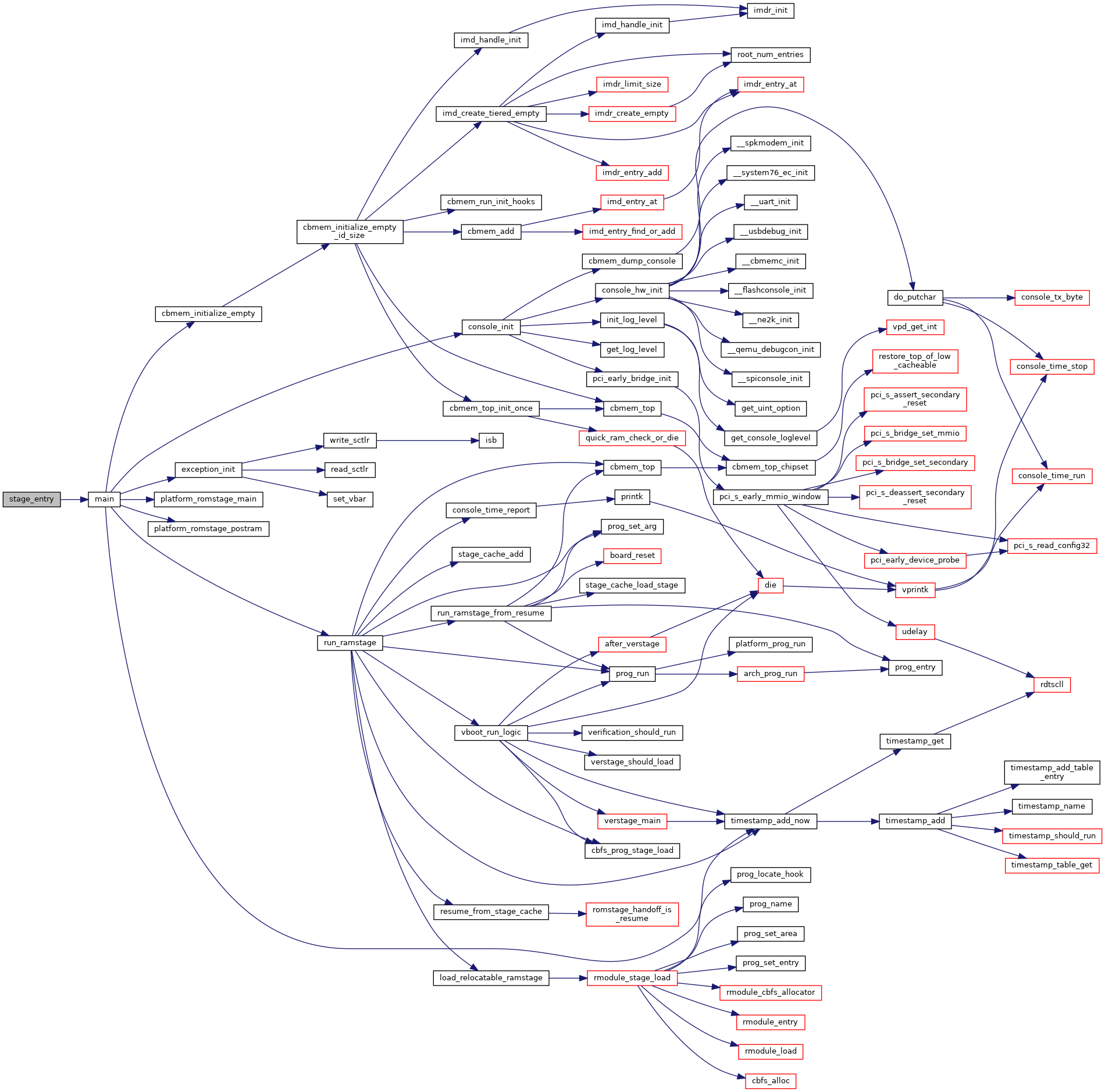

#include <arch/cache.h>#include <arch/exception.h>#include <arch/hlt.h>#include <arch/stages.h>#include <program_loading.h>#include <security/vboot/vboot_common.h>#include <soc/cache.h>#include <soc/early_configs.h>#include <symbols.h>

Go to the source code of this file.

Functions | |

| static void | enable_cache (void) |

| void | verstage_mainboard_init (void) |

| void | stage_entry (uintptr_t unused) |

| generic stage entry point. More... | |

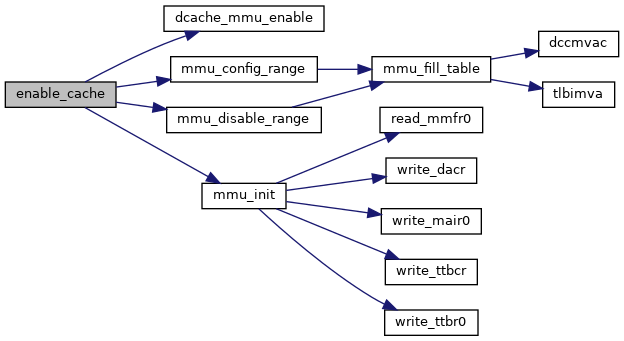

Definition at line 13 of file verstage.c.

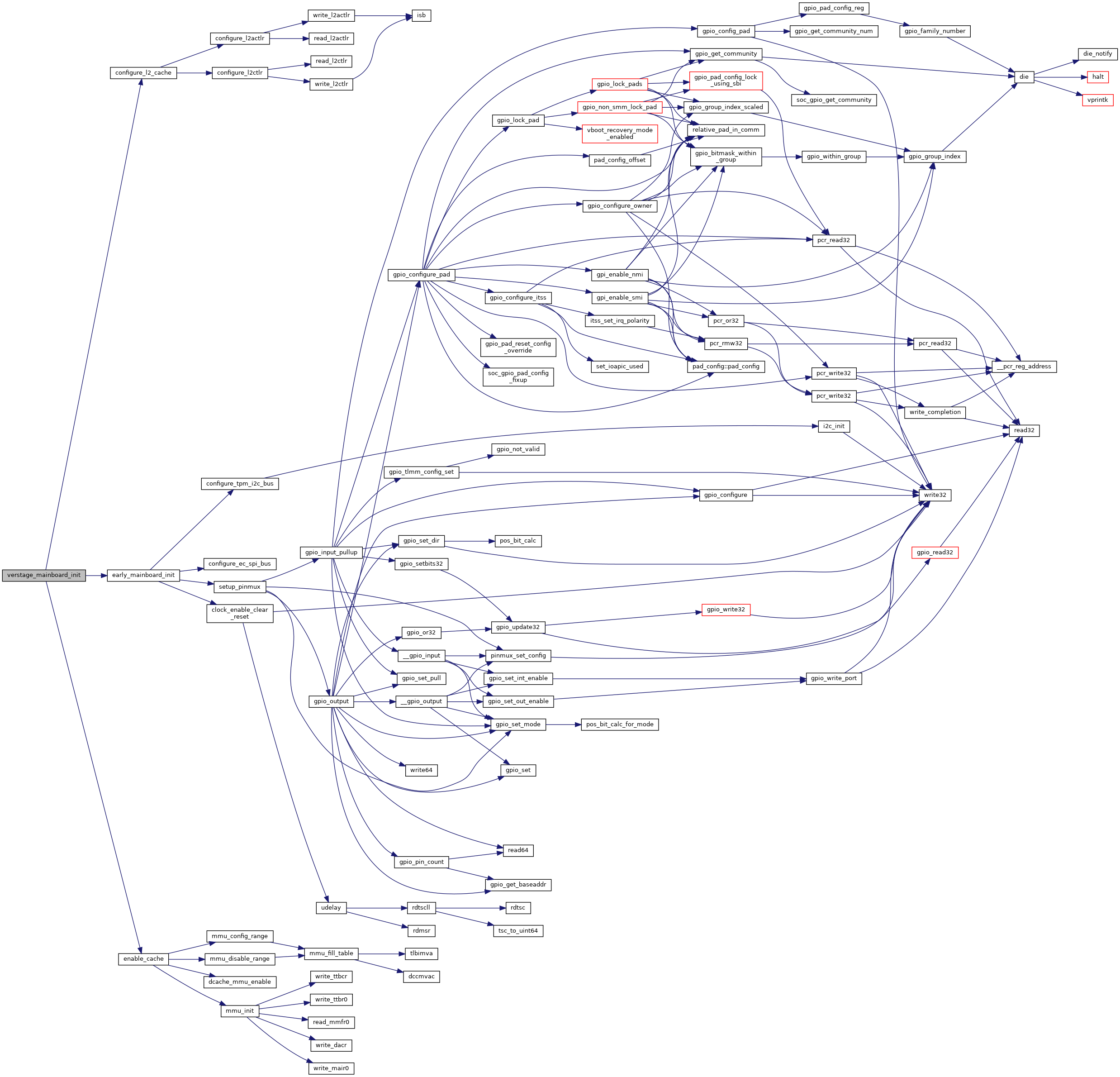

References dcache_mmu_enable(), DCACHE_OFF, DCACHE_WRITEBACK, DIV_ROUND_UP, MiB, mmu_config_range(), mmu_disable_range(), mmu_init(), and REGION_SIZE.

Referenced by verstage_mainboard_init().

generic stage entry point.

override this if board specific code is needed.

Definition at line 34 of file verstage.c.

References _cbmem_top_ptr, ENV_ROMSTAGE_OR_BEFORE, and main().

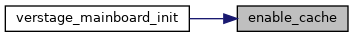

Definition at line 26 of file verstage.c.

References configure_l2_cache(), early_mainboard_init(), and enable_cache().