|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

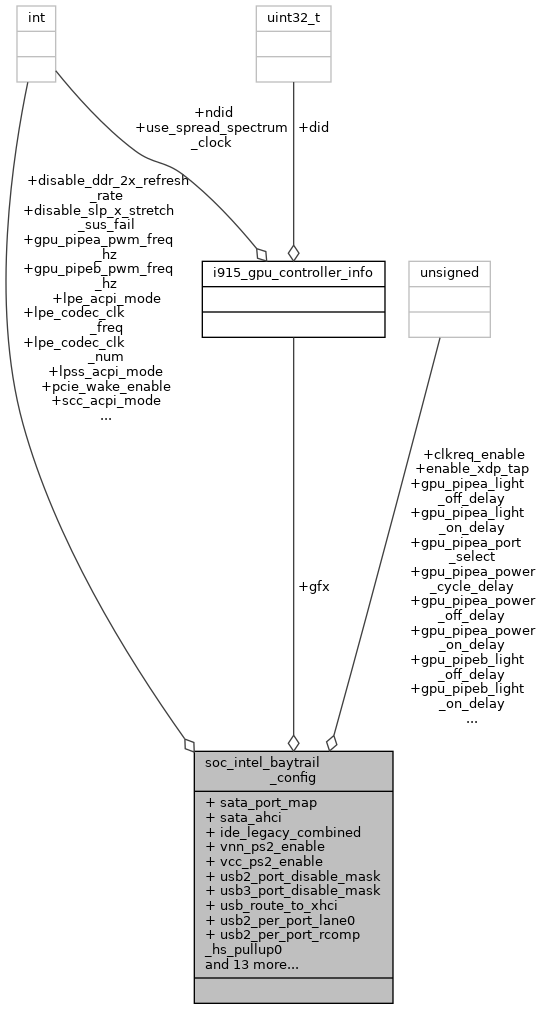

#include <chip.h>

| struct i915_gpu_controller_info soc_intel_baytrail_config::gfx |

| uint16_t soc_intel_baytrail_config::gpu_pipea_power_cycle_delay |

| uint16_t soc_intel_baytrail_config::gpu_pipeb_power_cycle_delay |

| uint32_t soc_intel_baytrail_config::usb2_comp_bg |

Definition at line 42 of file chip.h.

Referenced by usb2_phy_init().

| uint32_t soc_intel_baytrail_config::usb2_per_port_rcomp_hs_pullup0 |

| uint32_t soc_intel_baytrail_config::usb2_per_port_rcomp_hs_pullup1 |

| uint32_t soc_intel_baytrail_config::usb2_per_port_rcomp_hs_pullup2 |

| uint32_t soc_intel_baytrail_config::usb2_per_port_rcomp_hs_pullup3 |

| int soc_intel_baytrail_config::vcc_ps2_enable |

Definition at line 21 of file chip.h.

Referenced by punit_init().

| int soc_intel_baytrail_config::vnn_ps2_enable |

Definition at line 20 of file chip.h.

Referenced by punit_init().