|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

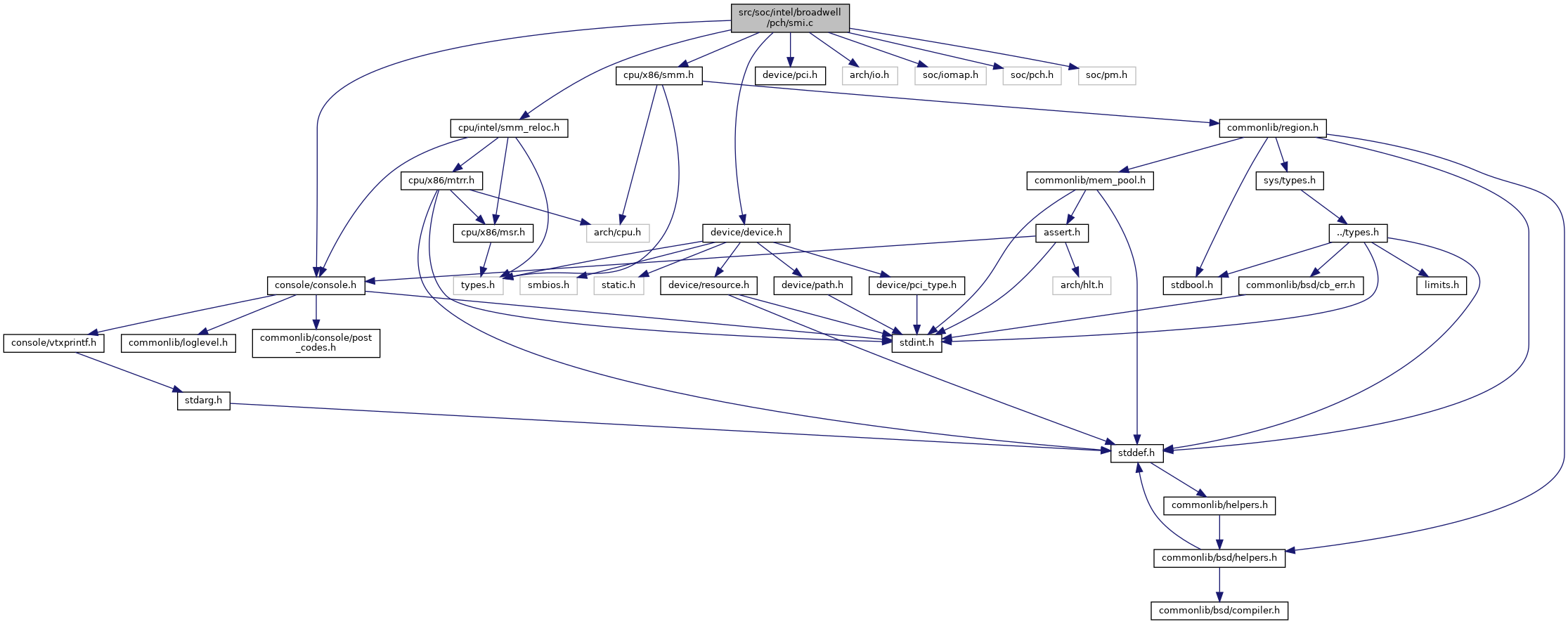

#include <device/device.h>#include <device/pci.h>#include <console/console.h>#include <arch/io.h>#include <cpu/x86/smm.h>#include <cpu/intel/smm_reloc.h>#include <soc/iomap.h>#include <soc/pch.h>#include <soc/pm.h>

Go to the source code of this file.

Functions | |

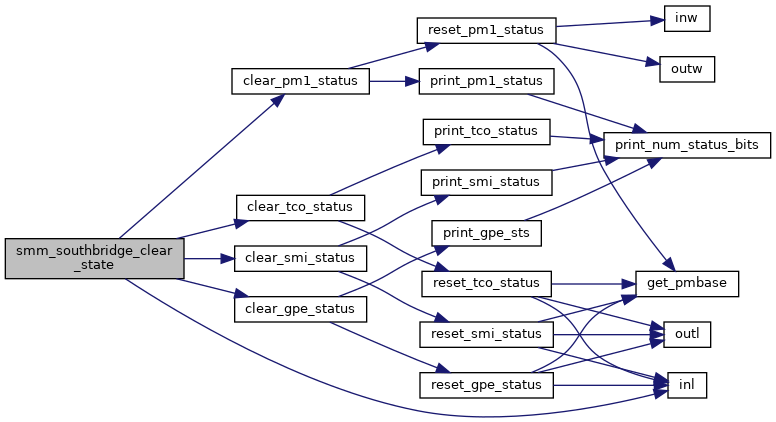

| void | smm_southbridge_clear_state (void) |

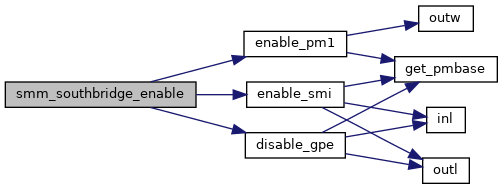

| static void | smm_southbridge_enable (uint16_t pm1_events) |

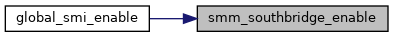

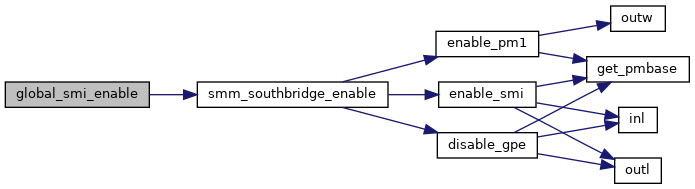

| void | global_smi_enable (void) |

| Set the EOS bit and enable SMI generation from southbridge. More... | |

Set the EOS bit and enable SMI generation from southbridge.

Definition at line 53 of file smi.c.

References GBL_EN, PWRBTN_EN, and smm_southbridge_enable().

Definition at line 13 of file smi.c.

References ACPI_BASE_ADDRESS, APMC_EN, BIOS_DEBUG, BIOS_INFO, BIOS_SPEW, clear_gpe_status(), clear_pm1_status(), clear_smi_status(), clear_tco_status(), inl(), printk, and SMI_EN.

Definition at line 35 of file smi.c.

References APMC_EN, BIOS_DEBUG, disable_gpe(), enable_pm1(), enable_smi(), EOS, GBL_SMI_EN, PME_B0_EN, printk, and SLP_SMI_EN.

Referenced by global_smi_enable().