|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

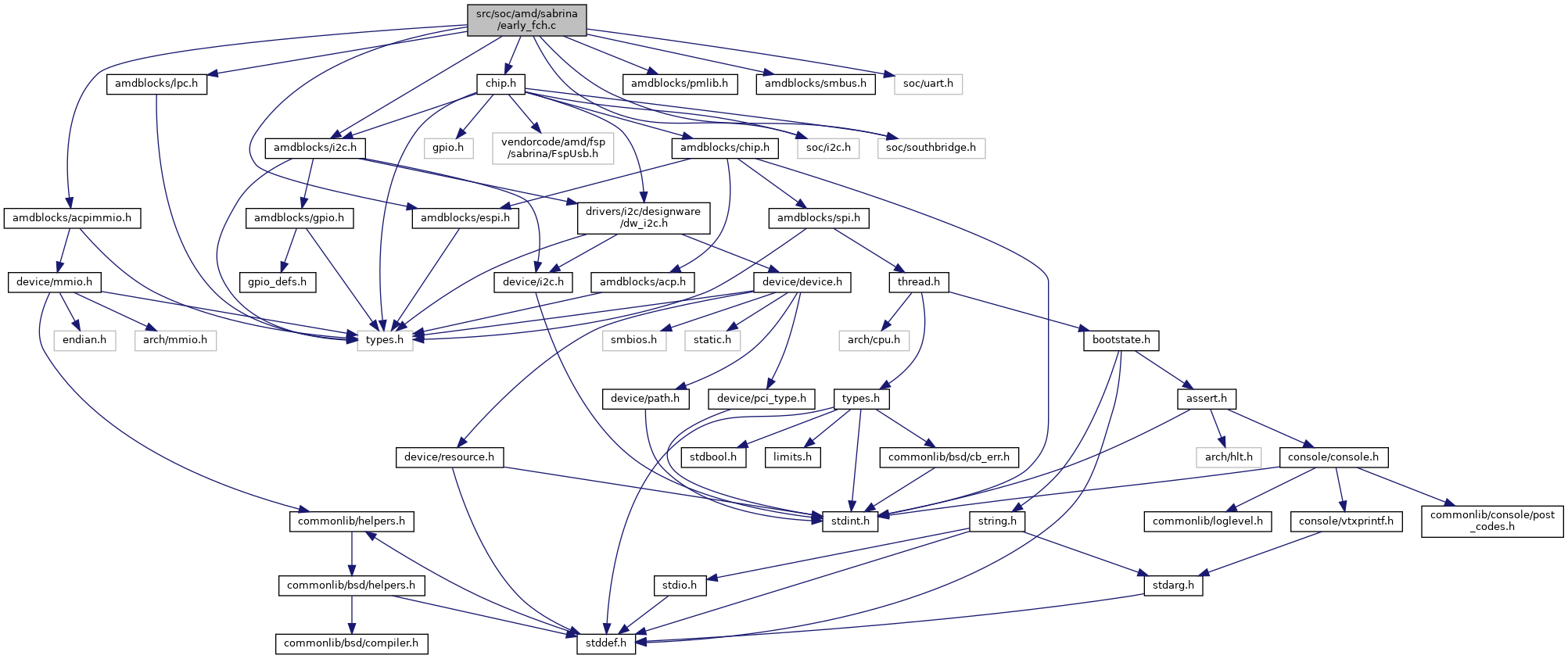

#include <amdblocks/acpimmio.h>#include <amdblocks/espi.h>#include <amdblocks/i2c.h>#include <amdblocks/lpc.h>#include <amdblocks/pmlib.h>#include <amdblocks/smbus.h>#include <soc/i2c.h>#include <soc/southbridge.h>#include <soc/uart.h>#include "chip.h"

Go to the source code of this file.

Functions | |

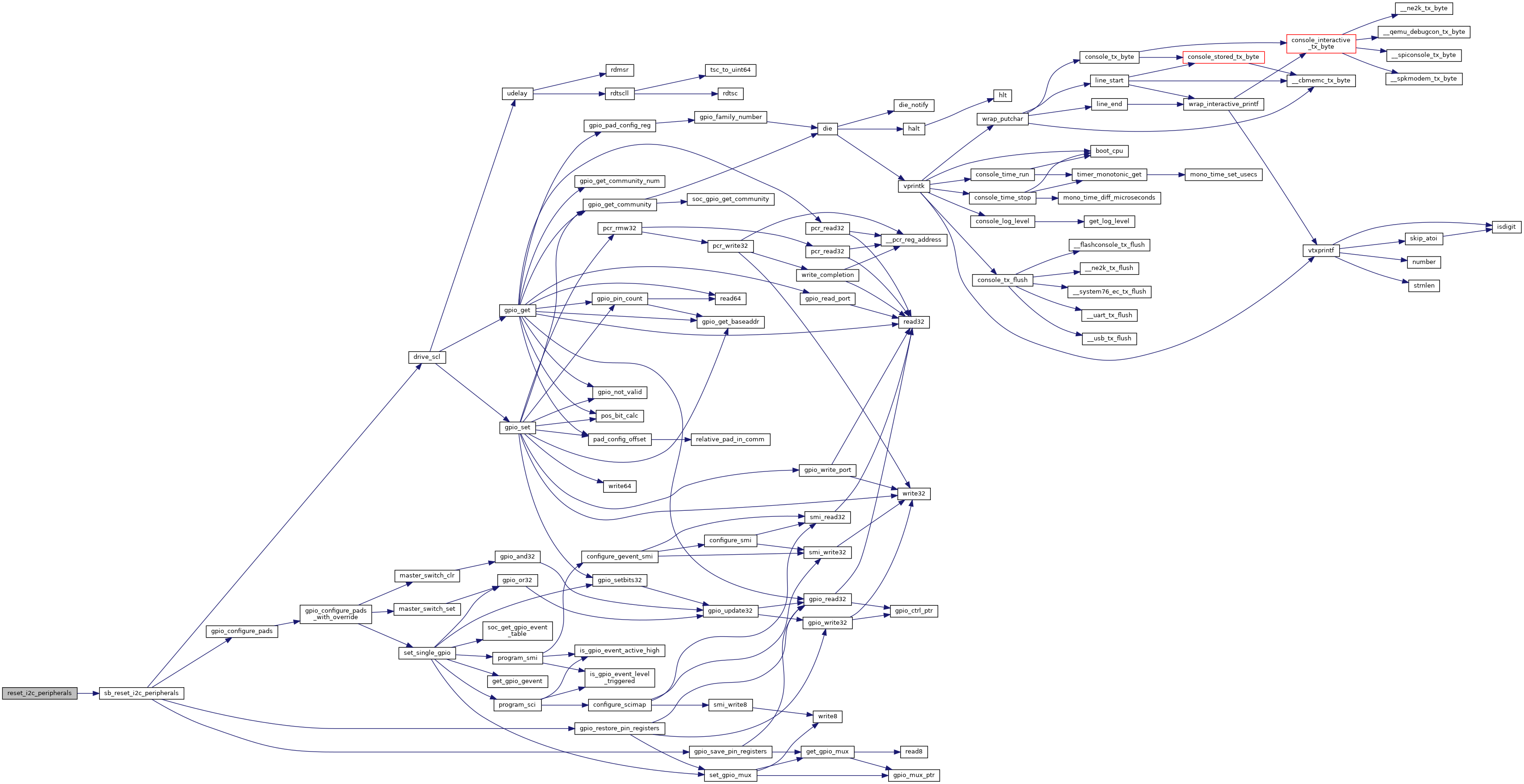

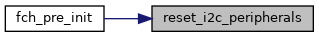

| static void | reset_i2c_peripherals (void) |

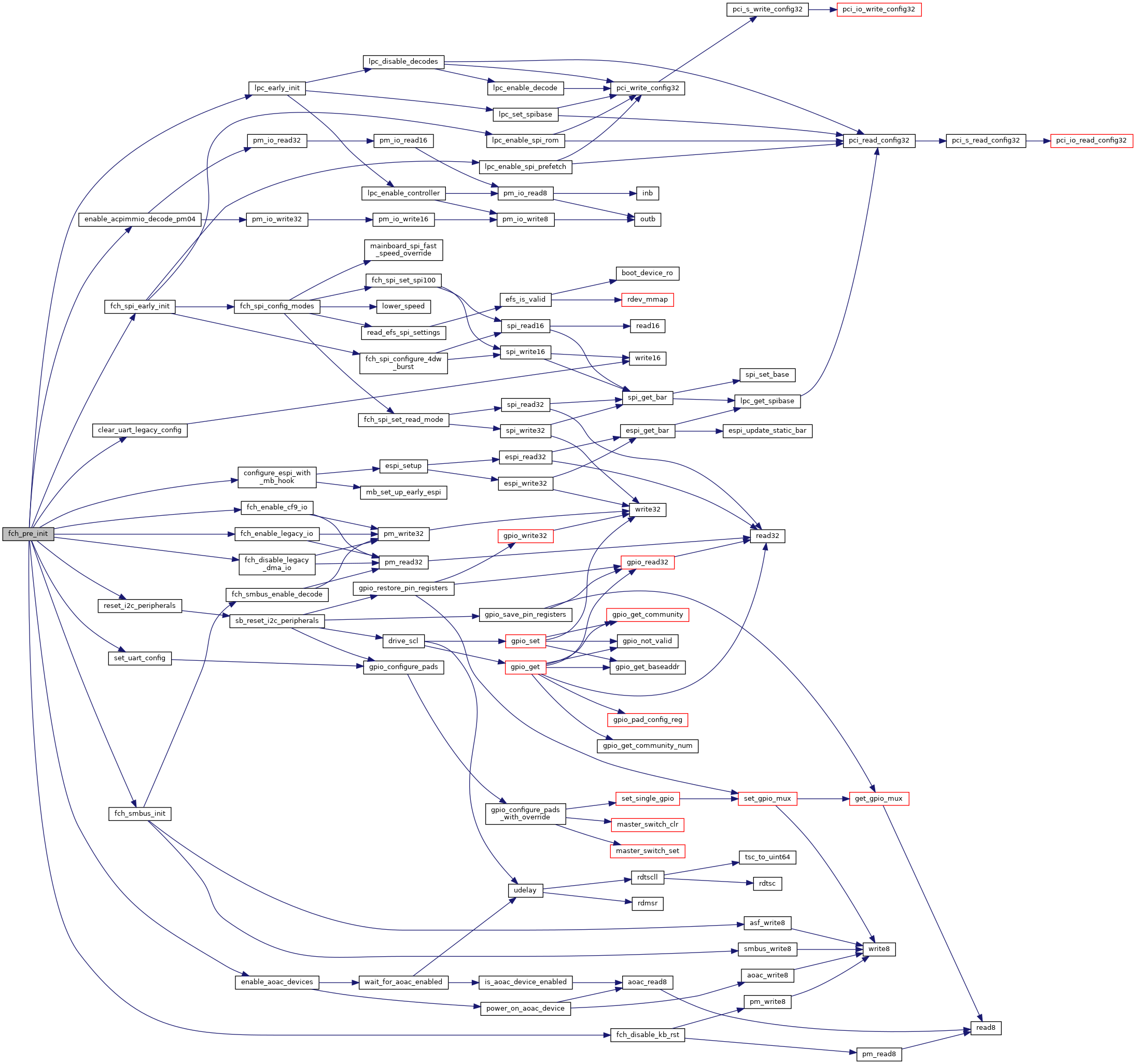

| void | fch_pre_init (void) |

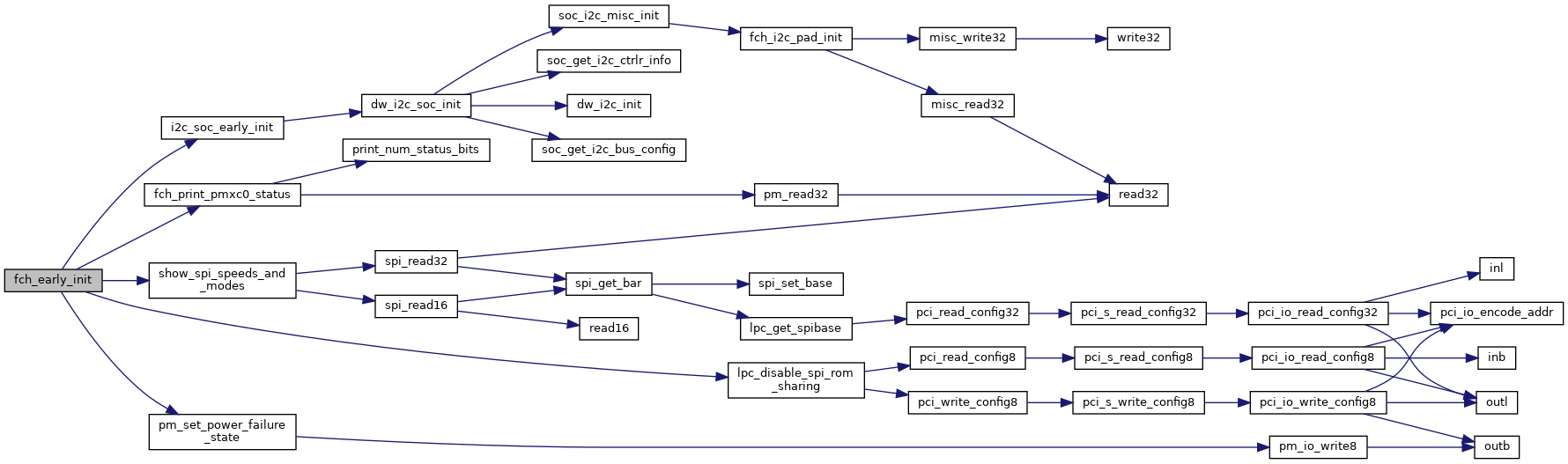

| void | fch_early_init (void) |

Variables | |

| static const struct soc_i2c_scl_pin | i2c_scl_pins [] |

Definition at line 73 of file early_fch.c.

References CONFIG, fch_print_pmxc0_status(), i2c_soc_early_init(), lpc_disable_spi_rom_sharing(), pm_set_power_failure_state(), and show_spi_speeds_and_modes().

Definition at line 37 of file early_fch.c.

References clear_uart_legacy_config(), CONFIG, configure_espi_with_mb_hook(), enable_acpimmio_decode_pm04(), enable_aoac_devices(), fch_disable_kb_rst(), fch_disable_legacy_dma_io(), fch_enable_cf9_io(), fch_enable_legacy_io(), fch_smbus_init(), fch_spi_early_init(), lpc_early_init(), reset_i2c_peripherals(), and set_uart_config().

Definition at line 25 of file early_fch.c.

References ARRAY_SIZE, config_of_soc, GPIO_I2C_MASK, soc_i2c_peripheral_reset_info::i2c_scl, i2c_scl_pins, soc_amd_sabrina_config::i2c_scl_reset, soc_i2c_peripheral_reset_info::i2c_scl_reset_mask, soc_i2c_peripheral_reset_info::num_pins, and sb_reset_i2c_peripherals().

Referenced by fch_pre_init().

|

static |

Definition at line 1 of file early_fch.c.

Referenced by reset_i2c_peripherals().