|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <stdint.h>

Go to the source code of this file.

Macros | |

| #define | COMPILER_BARRIER "memory" |

| #define | CRx_TYPE uint32_t |

| #define | CRx_IN "r" |

| #define | CRx_RET "=r" |

| #define | CR0_PE (1 << 0) |

| #define | CR0_MP (1 << 1) |

| #define | CR0_EM (1 << 2) |

| #define | CR0_TS (1 << 3) |

| #define | CR0_ET (1 << 4) |

| #define | CR0_NE (1 << 5) |

| #define | CR0_WP (1 << 16) |

| #define | CR0_AM (1 << 18) |

| #define | CR0_NW (1 << 29) |

| #define | CR0_CD (1 << 30) |

| #define | CR0_PG (1 << 31) |

| #define | CR4_VME (1 << 0) |

| #define | CR4_PVI (1 << 1) |

| #define | CR4_TSD (1 << 2) |

| #define | CR4_DE (1 << 3) |

| #define | CR4_PSE (1 << 4) |

| #define | CR4_PAE (1 << 5) |

| #define | CR4_MCE (1 << 6) |

| #define | CR4_PGE (1 << 7) |

| #define | CR4_PCE (1 << 8) |

| #define | CR4_OSFXSR (1 << 9) |

| #define | CR4_OSXMMEXCPT (1 << 10) |

| #define | CR4_VMXE (1 << 13) |

| #define | CR4_SMXE (1 << 14) |

| #define | CR4_FSGSBASE (1 << 16) |

| #define | CR4_PCIDE (1 << 17) |

| #define | CR4_OSXSAVE (1 << 18) |

| #define | CR4_SMEP (1 << 20) |

Functions | |

| static __always_inline CRx_TYPE | read_cr0 (void) |

| static __always_inline void | write_cr0 (CRx_TYPE data) |

| static __always_inline CRx_TYPE | read_cr2 (void) |

| static __always_inline CRx_TYPE | read_cr3 (void) |

| static __always_inline void | write_cr3 (CRx_TYPE data) |

| static __always_inline CRx_TYPE | read_cr4 (void) |

| static __always_inline void | write_cr4 (CRx_TYPE data) |

|

static |

Definition at line 21 of file cr.h.

References COMPILER_BARRIER, CRx_RET, CRx_TYPE, and value.

Referenced by disable_cache(), enable_cache(), paging_disable_pae(), paging_enable_pae(), paging_is_enabled(), and reg_cpu_cr_read().

|

static |

Definition at line 43 of file cr.h.

References COMPILER_BARRIER, CRx_RET, CRx_TYPE, and value.

Referenced by x86_exception().

|

static |

Definition at line 55 of file cr.h.

References COMPILER_BARRIER, CRx_RET, CRx_TYPE, and value.

Referenced by get_pdpt_addr().

|

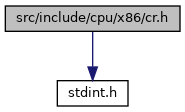

static |

Definition at line 76 of file cr.h.

References COMPILER_BARRIER, CRx_RET, CRx_TYPE, and value.

Referenced by baytrail_init_pre_device(), dnv_configure_mca(), getsec_enabled(), intel_txt_romstage_init(), paging_disable_pae(), paging_enable_pae(), reg_cpu_cr_read(), secondary_cpu_init(), and soc_init_pre_device().

|

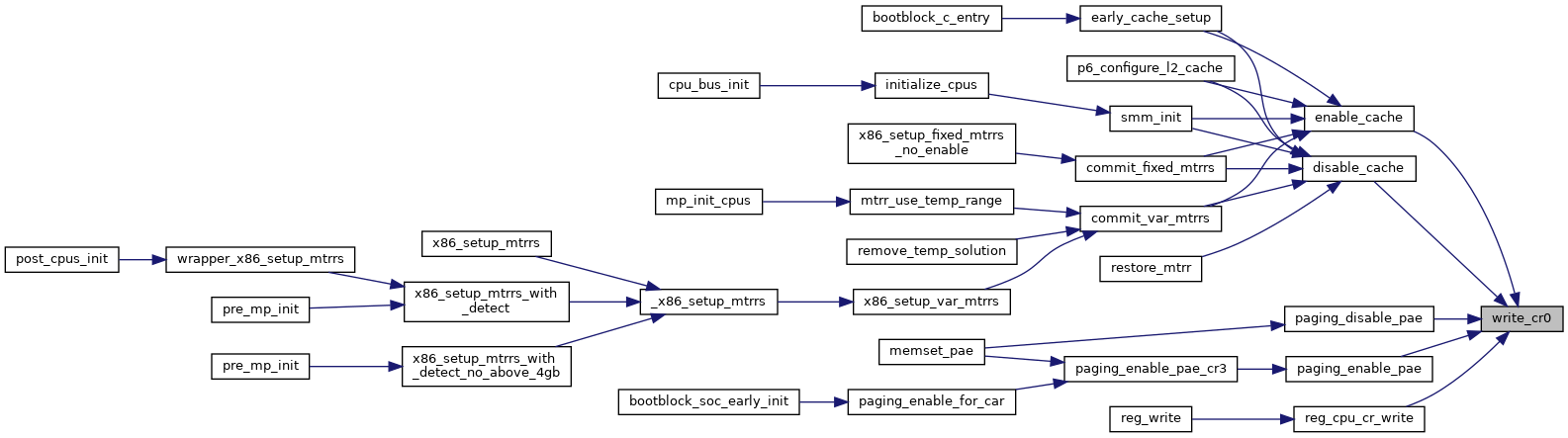

static |

Definition at line 33 of file cr.h.

References COMPILER_BARRIER, and CRx_IN.

Referenced by disable_cache(), enable_cache(), paging_disable_pae(), paging_enable_pae(), and reg_cpu_cr_write().

|

static |

Definition at line 67 of file cr.h.

References COMPILER_BARRIER, and CRx_IN.

Referenced by paging_enable_pae_cr3().

|

static |

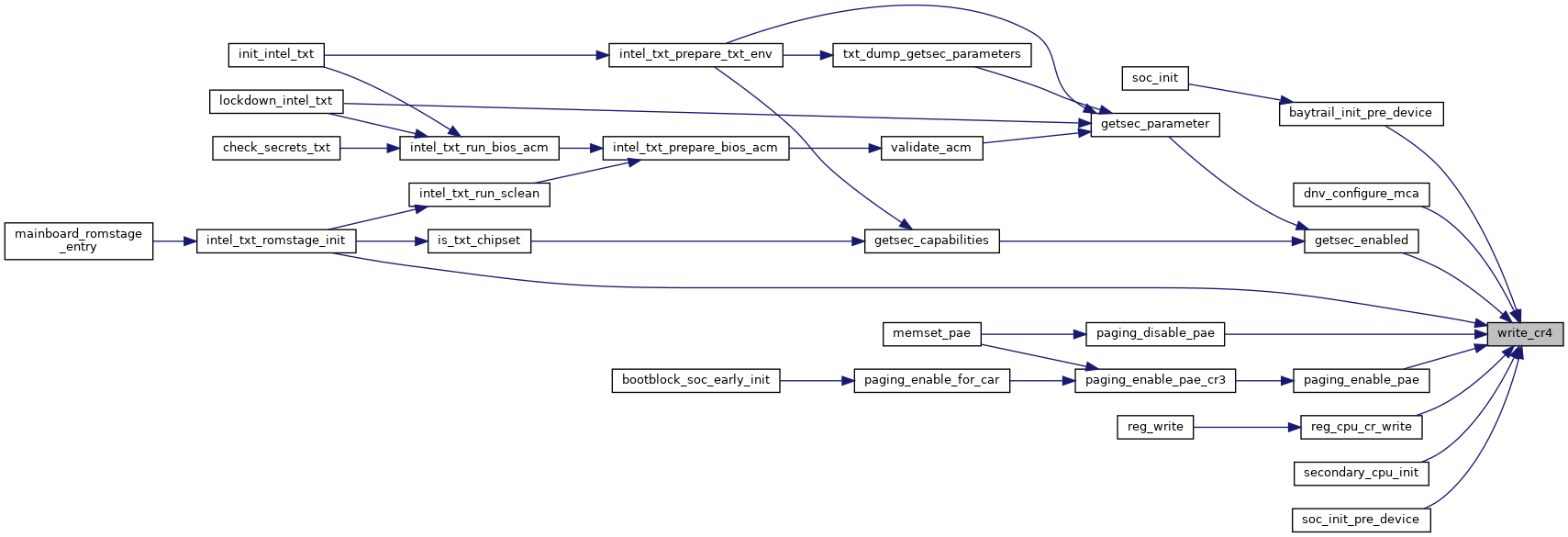

Definition at line 88 of file cr.h.

References COMPILER_BARRIER, and CRx_IN.

Referenced by baytrail_init_pre_device(), dnv_configure_mca(), getsec_enabled(), intel_txt_romstage_init(), paging_disable_pae(), paging_enable_pae(), reg_cpu_cr_write(), secondary_cpu_init(), and soc_init_pre_device().