|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

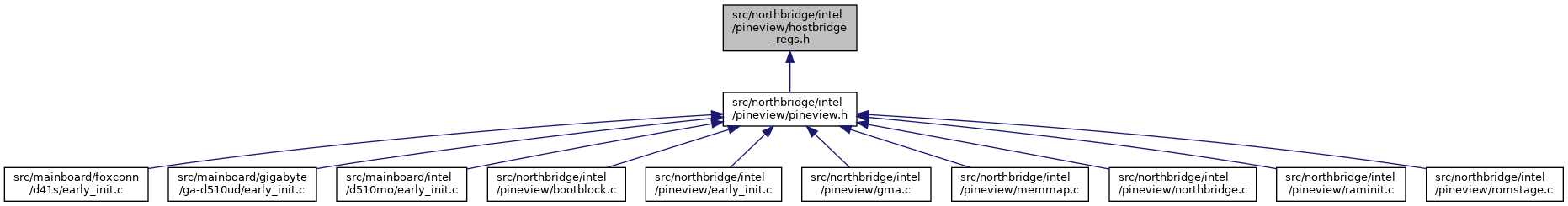

Go to the source code of this file.

Macros | |

| #define | EPBAR 0x40 |

| #define | MCHBAR 0x48 |

| #define | GGC 0x52 /* GMCH Graphics Control */ |

| #define | DEVEN 0x54 /* Device Enable */ |

| #define | DEVEN_D0F0 (1 << 0) |

| #define | DEVEN_D1F0 (1 << 1) |

| #define | DEVEN_D2F0 (1 << 3) |

| #define | DEVEN_D2F1 (1 << 4) |

| #define | BOARD_DEVEN (DEVEN_D0F0 | DEVEN_D2F0 | DEVEN_D2F1) |

| #define | PCIEXBAR 0x60 |

| #define | DMIBAR 0x68 |

| #define | PMIOBAR 0x78 |

| #define | PAM0 0x90 |

| #define | PAM1 0x91 |

| #define | PAM2 0x92 |

| #define | PAM3 0x93 |

| #define | PAM4 0x94 |

| #define | PAM5 0x95 |

| #define | PAM6 0x96 |

| #define | LAC 0x97 /* Legacy Access Control */ |

| #define | REMAPBASE 0x98 |

| #define | REMAPLIMIT 0x9a |

| #define | SMRAM 0x9d /* System Management RAM Control */ |

| #define | ESMRAMC 0x9e /* Extended System Management RAM Control */ |

| #define | TOM 0xa0 |

| #define | TOUUD 0xa2 |

| #define | GBSM 0xa4 |

| #define | BGSM 0xa8 |

| #define | TSEG 0xac |

| #define | TOLUD 0xb0 /* Top of Low Used Memory */ |

| #define | ERRSTS 0xc8 |

| #define | ERRCMD 0xca |

| #define | SMICMD 0xcc |

| #define | SCICMD 0xce |

| #define | CGDIS 0xd8 |

| #define | SKPAD 0xdc /* Scratchpad Data */ |

| #define | CAPID0 0xe0 |

| #define | DEV0T 0xf0 |

| #define | MSLCK 0xf4 |

| #define | MID0 0xf8 |

| #define | DEBUP0 0xfc |

| #define BGSM 0xa8 |

Definition at line 42 of file hostbridge_regs.h.

| #define BOARD_DEVEN (DEVEN_D0F0 | DEVEN_D2F0 | DEVEN_D2F1) |

Definition at line 18 of file hostbridge_regs.h.

| #define CAPID0 0xe0 |

Definition at line 51 of file hostbridge_regs.h.

| #define CGDIS 0xd8 |

Definition at line 49 of file hostbridge_regs.h.

| #define DEBUP0 0xfc |

Definition at line 55 of file hostbridge_regs.h.

| #define DEV0T 0xf0 |

Definition at line 52 of file hostbridge_regs.h.

| #define DEVEN 0x54 /* Device Enable */ |

Definition at line 11 of file hostbridge_regs.h.

| #define DEVEN_D0F0 (1 << 0) |

Definition at line 12 of file hostbridge_regs.h.

| #define DEVEN_D1F0 (1 << 1) |

Definition at line 13 of file hostbridge_regs.h.

| #define DEVEN_D2F0 (1 << 3) |

Definition at line 14 of file hostbridge_regs.h.

| #define DEVEN_D2F1 (1 << 4) |

Definition at line 15 of file hostbridge_regs.h.

| #define DMIBAR 0x68 |

Definition at line 22 of file hostbridge_regs.h.

| #define EPBAR 0x40 |

Definition at line 6 of file hostbridge_regs.h.

| #define ERRCMD 0xca |

Definition at line 46 of file hostbridge_regs.h.

| #define ERRSTS 0xc8 |

Definition at line 45 of file hostbridge_regs.h.

| #define ESMRAMC 0x9e /* Extended System Management RAM Control */ |

Definition at line 37 of file hostbridge_regs.h.

| #define GBSM 0xa4 |

Definition at line 41 of file hostbridge_regs.h.

| #define GGC 0x52 /* GMCH Graphics Control */ |

Definition at line 9 of file hostbridge_regs.h.

| #define LAC 0x97 /* Legacy Access Control */ |

Definition at line 33 of file hostbridge_regs.h.

| #define MCHBAR 0x48 |

Definition at line 7 of file hostbridge_regs.h.

| #define MID0 0xf8 |

Definition at line 54 of file hostbridge_regs.h.

| #define MSLCK 0xf4 |

Definition at line 53 of file hostbridge_regs.h.

| #define PAM0 0x90 |

Definition at line 25 of file hostbridge_regs.h.

| #define PAM1 0x91 |

Definition at line 26 of file hostbridge_regs.h.

| #define PAM2 0x92 |

Definition at line 27 of file hostbridge_regs.h.

| #define PAM3 0x93 |

Definition at line 28 of file hostbridge_regs.h.

| #define PAM4 0x94 |

Definition at line 29 of file hostbridge_regs.h.

| #define PAM5 0x95 |

Definition at line 30 of file hostbridge_regs.h.

| #define PAM6 0x96 |

Definition at line 31 of file hostbridge_regs.h.

| #define PCIEXBAR 0x60 |

Definition at line 21 of file hostbridge_regs.h.

| #define PMIOBAR 0x78 |

Definition at line 23 of file hostbridge_regs.h.

| #define REMAPBASE 0x98 |

Definition at line 34 of file hostbridge_regs.h.

| #define REMAPLIMIT 0x9a |

Definition at line 35 of file hostbridge_regs.h.

| #define SCICMD 0xce |

Definition at line 48 of file hostbridge_regs.h.

| #define SKPAD 0xdc /* Scratchpad Data */ |

Definition at line 50 of file hostbridge_regs.h.

| #define SMICMD 0xcc |

Definition at line 47 of file hostbridge_regs.h.

| #define SMRAM 0x9d /* System Management RAM Control */ |

Definition at line 36 of file hostbridge_regs.h.

| #define TOLUD 0xb0 /* Top of Low Used Memory */ |

Definition at line 44 of file hostbridge_regs.h.

| #define TOM 0xa0 |

Definition at line 39 of file hostbridge_regs.h.

| #define TOUUD 0xa2 |

Definition at line 40 of file hostbridge_regs.h.

| #define TSEG 0xac |

Definition at line 43 of file hostbridge_regs.h.