|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

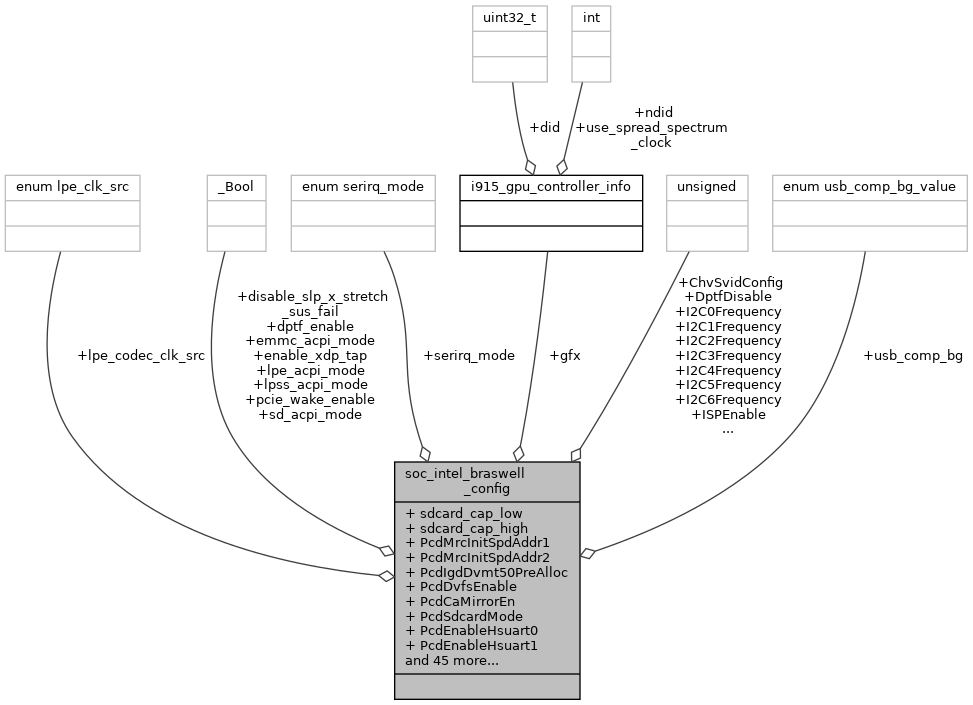

#include <chip.h>

| bool soc_intel_braswell_config::disable_slp_x_stretch_sus_fail |

| struct i915_gpu_controller_info soc_intel_braswell_config::gfx |

| enum lpe_clk_src soc_intel_braswell_config::lpe_codec_clk_src |

| enum serirq_mode soc_intel_braswell_config::serirq_mode |

| uint8_t soc_intel_braswell_config::Usb3Lane0Ow2tapgen2deemph3p5 |

| uint8_t soc_intel_braswell_config::Usb3Lane1Ow2tapgen2deemph3p5 |

| uint8_t soc_intel_braswell_config::Usb3Lane2Ow2tapgen2deemph3p5 |

| uint8_t soc_intel_braswell_config::Usb3Lane3Ow2tapgen2deemph3p5 |

| enum usb_comp_bg_value soc_intel_braswell_config::usb_comp_bg |