|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <usb_common.h>

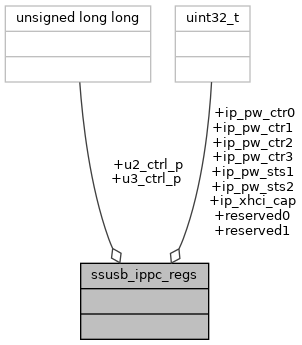

Data Fields | |

| u32 | ip_pw_ctr0 |

| u32 | ip_pw_ctr1 |

| u32 | ip_pw_ctr2 |

| u32 | ip_pw_ctr3 |

| u32 | ip_pw_sts1 |

| u32 | ip_pw_sts2 |

| u32 | reserved0 [3] |

| u32 | ip_xhci_cap |

| u32 | reserved1 [2] |

| u64 | u3_ctrl_p [4] |

| u64 | u2_ctrl_p [6] |

Definition at line 37 of file usb_common.h.

| u32 ssusb_ippc_regs::ip_pw_ctr0 |

Definition at line 38 of file usb_common.h.

Referenced by ssusb_soft_reset().

| u32 ssusb_ippc_regs::ip_pw_ctr1 |

Definition at line 39 of file usb_common.h.

Referenced by u3phy_ports_enable().

| u32 ssusb_ippc_regs::ip_pw_ctr2 |

Definition at line 40 of file usb_common.h.

| u32 ssusb_ippc_regs::ip_pw_ctr3 |

Definition at line 41 of file usb_common.h.

| u32 ssusb_ippc_regs::ip_pw_sts1 |

Definition at line 42 of file usb_common.h.

Referenced by check_ip_clk_status().

| u32 ssusb_ippc_regs::ip_pw_sts2 |

Definition at line 43 of file usb_common.h.

Referenced by check_ip_clk_status().

| u32 ssusb_ippc_regs::ip_xhci_cap |

Definition at line 45 of file usb_common.h.

Referenced by check_ip_clk_status(), and u3phy_ports_enable().

| u32 ssusb_ippc_regs::reserved0[3] |

Definition at line 44 of file usb_common.h.

| u32 ssusb_ippc_regs::reserved1[2] |

Definition at line 46 of file usb_common.h.

| u64 ssusb_ippc_regs::u2_ctrl_p[6] |

Definition at line 48 of file usb_common.h.

Referenced by u3phy_ports_enable().

| u64 ssusb_ippc_regs::u3_ctrl_p[4] |

Definition at line 47 of file usb_common.h.

Referenced by u3phy_ports_enable().