|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <spi.h>

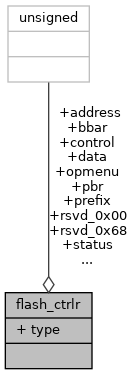

Data Fields | |

| uint8_t | rsvd_0x00 [0x3020] |

| uint16_t | status |

| uint16_t | control |

| uint32_t | address |

| uint8_t | data [64] |

| uint8_t | rsvd_0x68 [8] |

| uint32_t | bbar |

| uint8_t | prefix [2] |

| uint16_t | type |

| uint8_t | opmenu [8] |

| uint32_t | pbr [3] |

| uint32_t flash_ctrlr::bbar |

Definition at line 28 of file spi.h.

Referenced by spi_bios_base(), and spi_display().

| uint8_t flash_ctrlr::opmenu[8] |

Definition at line 31 of file spi.h.

Referenced by spi_display(), spi_init(), and xfer().

| uint32_t flash_ctrlr::pbr[3] |

Definition at line 32 of file spi.h.

Referenced by spi_display(), and spi_protection().

| uint8_t flash_ctrlr::prefix[2] |

Definition at line 29 of file spi.h.

Referenced by spi_display(), spi_init(), and xfer().

| uint16_t flash_ctrlr::status |

Definition at line 23 of file spi.h.

Referenced by spi_controller_lock(), spi_display(), and xfer().

| uint16_t flash_ctrlr::type |

Definition at line 30 of file spi.h.

Referenced by spi_display(), spi_init(), and xfer().