|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

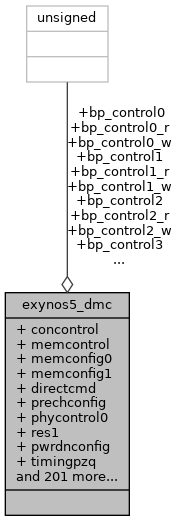

#include <dmc.h>

| uint32_t exynos5_dmc::cgcontrol |

Definition at line 65 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::concontrol |

Definition at line 11 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::directcmd |

Definition at line 15 of file dmc.h.

Referenced by ddr3_mem_ctrl_init(), dmc_config_mrs(), and dmc_config_prech().

| unsigned int exynos5_dmc::ivcontrol |

Definition at line 64 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::membaseconfig0 |

Definition at line 70 of file dmc.h.

Referenced by ddr3_mem_ctrl_init(), and dmc_config_memory().

| unsigned int exynos5_dmc::membaseconfig1 |

Definition at line 71 of file dmc.h.

Referenced by ddr3_mem_ctrl_init(), and dmc_config_memory().

| unsigned int exynos5_dmc::memconfig0 |

Definition at line 13 of file dmc.h.

Referenced by ddr3_mem_ctrl_init(), and dmc_config_memory().

| unsigned int exynos5_dmc::memconfig1 |

Definition at line 14 of file dmc.h.

Referenced by ddr3_mem_ctrl_init(), and dmc_config_memory().

| unsigned int exynos5_dmc::memcontrol |

Definition at line 12 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::phycontrol0 |

Definition at line 17 of file dmc.h.

Referenced by ddr3_mem_ctrl_init(), and update_reset_dll().

| unsigned int exynos5_dmc::phystatus |

Definition at line 25 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::prechconfig |

Definition at line 16 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| uint32_t exynos5_dmc::prechconfig0 |

Definition at line 68 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::pwrdnconfig |

Definition at line 19 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::rdlvl_config |

Definition at line 66 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::timingdata |

Definition at line 23 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::timingpower |

Definition at line 24 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::timingref |

Definition at line 21 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().

| unsigned int exynos5_dmc::timingrow |

Definition at line 22 of file dmc.h.

Referenced by ddr3_mem_ctrl_init().