|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

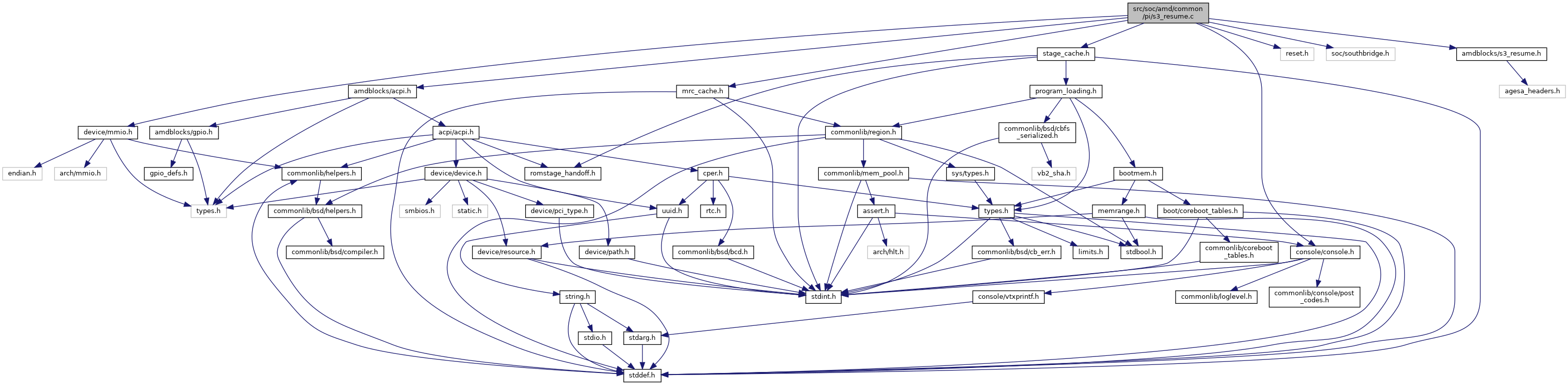

#include <device/mmio.h>#include <stage_cache.h>#include <mrc_cache.h>#include <reset.h>#include <console/console.h>#include <soc/southbridge.h>#include <amdblocks/s3_resume.h>#include <amdblocks/acpi.h>

Go to the source code of this file.

Macros | |

| #define | DEFAULT_MRC_VERSION 0 |

Functions | |

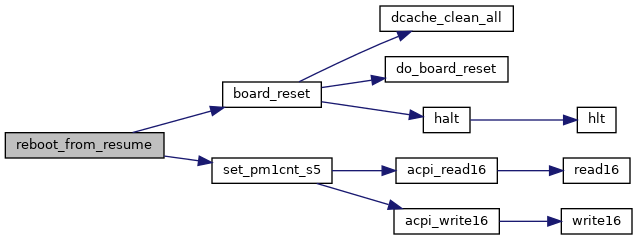

| static void __noreturn | reboot_from_resume (const char *message) |

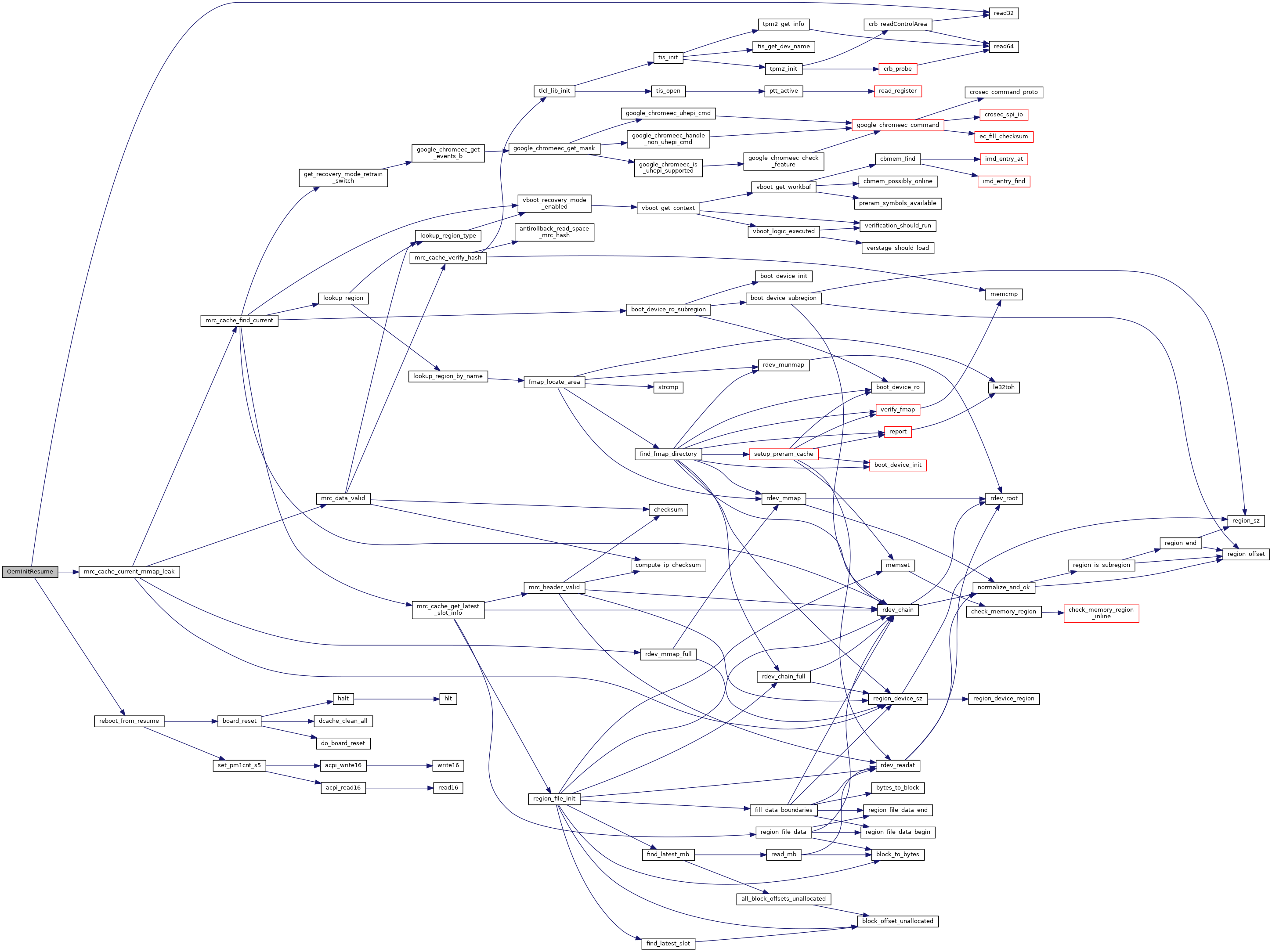

| AGESA_STATUS | OemInitResume (S3_DATA_BLOCK *dataBlock) |

| AGESA_STATUS | OemS3LateRestore (S3_DATA_BLOCK *dataBlock) |

| AGESA_STATUS | OemS3Save (S3_DATA_BLOCK *dataBlock) |

| #define DEFAULT_MRC_VERSION 0 |

Definition at line 13 of file s3_resume.c.

| AGESA_STATUS OemInitResume | ( | S3_DATA_BLOCK * | dataBlock | ) |

Definition at line 22 of file s3_resume.c.

References AGESA_SUCCESS, base, BIOS_SPEW, DEFAULT_MRC_VERSION, mrc_cache_current_mmap_leak(), MRC_TRAINING_DATA, printk, read32(), and reboot_from_resume().

| AGESA_STATUS OemS3LateRestore | ( | S3_DATA_BLOCK * | dataBlock | ) |

Definition at line 49 of file s3_resume.c.

References AGESA_FATAL, AGESA_SUCCESS, base, BIOS_ERR, BIOS_SPEW, NULL, printk, stage_cache_get_raw(), and STAGE_S3_DATA.

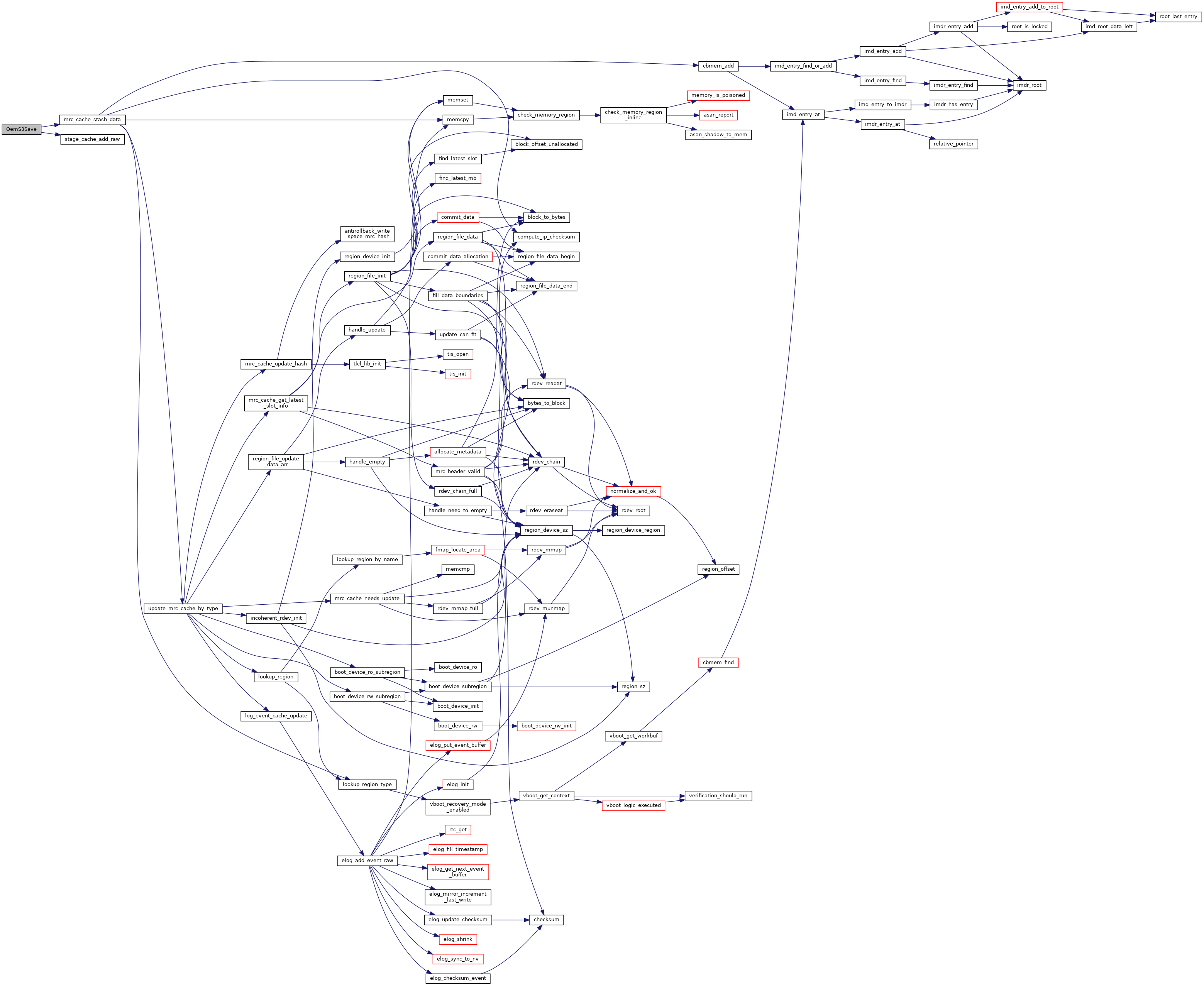

| AGESA_STATUS OemS3Save | ( | S3_DATA_BLOCK * | dataBlock | ) |

Definition at line 68 of file s3_resume.c.

References AGESA_CRITICAL, AGESA_SUCCESS, BIOS_ERR, DEFAULT_MRC_VERSION, mrc_cache_stash_data(), MRC_TRAINING_DATA, printk, stage_cache_add_raw(), and STAGE_S3_DATA.

|

static |

Definition at line 15 of file s3_resume.c.

References BIOS_ERR, board_reset(), printk, and set_pm1cnt_s5().

Referenced by OemInitResume().