|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

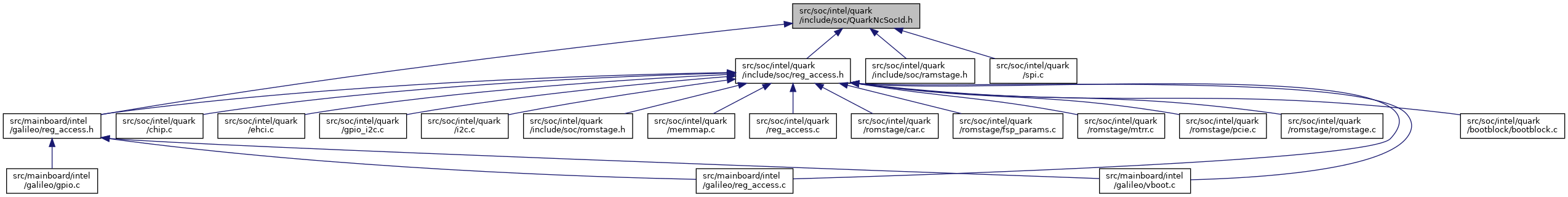

Go to the source code of this file.

| #define ASTATUS0_DEFAULT_BP (0) |

Definition at line 158 of file QuarkNcSocId.h.

| #define ASTATUS0_DEFAULT_BP_MASK (0x03 << ASTATUS1_RASISED_BP) |

Definition at line 159 of file QuarkNcSocId.h.

| #define ASTATUS0_RASISED_BP (8) |

Definition at line 154 of file QuarkNcSocId.h.

| #define ASTATUS0_RASISED_BP_MASK (0x03 << ASTATUS1_RASISED_BP) |

Definition at line 155 of file QuarkNcSocId.h.

| #define ASTATUS1_DEFAULT_BP (2) |

Definition at line 156 of file QuarkNcSocId.h.

| #define ASTATUS1_DEFAULT_BP_MASK (0x03 << ASTATUS1_RASISED_BP) |

Definition at line 157 of file QuarkNcSocId.h.

| #define ASTATUS1_RASISED_BP (10) |

Definition at line 152 of file QuarkNcSocId.h.

| #define ASTATUS1_RASISED_BP_MASK (0x03 << ASTATUS1_RASISED_BP) |

Definition at line 153 of file QuarkNcSocId.h.

| #define ASTATUS_PRI_CASUAL 0x0 |

Definition at line 148 of file QuarkNcSocId.h.

| #define ASTATUS_PRI_IMPENDING 0x1 |

Definition at line 149 of file QuarkNcSocId.h.

| #define ASTATUS_PRI_NORMAL 0x2 |

Definition at line 150 of file QuarkNcSocId.h.

| #define ASTATUS_PRI_URGENT 0x3 |

Definition at line 151 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_ALL |

Definition at line 382 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_DECC_VIOLATION BIT3 |

Definition at line 374 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_FORCE_RECOVERY BIT9 |

Definition at line 376 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_HMB_VIOLATION BIT1 |

Definition at line 372 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_IMR_VIOLATION BIT2 |

Definition at line 373 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_SMM_VIOLATION BIT0 |

Definition at line 371 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_VIOLATION |

Definition at line 377 of file QuarkNcSocId.h.

| #define B_CFG_STICKY_RW_WARM_RST BIT4 |

Definition at line 375 of file QuarkNcSocId.h.

| #define B_DFUSESTAT_ECC_DIS (BIT0) |

Definition at line 165 of file QuarkNcSocId.h.

| #define B_MUXTOP_FLEX1_BP 20 |

Definition at line 392 of file QuarkNcSocId.h.

Definition at line 391 of file QuarkNcSocId.h.

| #define B_MUXTOP_FLEX2_BP 23 |

Definition at line 390 of file QuarkNcSocId.h.

Definition at line 389 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0E_EGPE (BIT13) |

Definition at line 536 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0E_GPIO (BIT14) |

Definition at line 535 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0E_PCIE (BIT17) |

Definition at line 534 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0S_ALL 0x00003F800 |

Definition at line 526 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0S_EGPE (BIT13) |

Definition at line 529 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0S_GPIO (BIT14) |

Definition at line 528 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_GPE0S_PCIE (BIT17) |

Definition at line 527 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_PMCW_PSE (BIT31) |

Definition at line 568 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_PMSW_DRAM_INIT (BIT0) |

Definition at line 571 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIE_ALL 0x0003871F |

Definition at line 541 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIE_APM (BIT4) |

Definition at line 542 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIE_SLP (BIT2) |

Definition at line 543 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIE_SWT (BIT1) |

Definition at line 544 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_ALL 0x0003871F |

Definition at line 554 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_APM (BIT4) |

Definition at line 556 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_BIOS (BIT0) |

Definition at line 560 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_EOS (BIT31) |

Definition at line 555 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_SLP (BIT2) |

Definition at line 558 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_SPI (BIT3) |

Definition at line 557 of file QuarkNcSocId.h.

| #define B_QNC_GPE0BLK_SMIS_SWT (BIT1) |

Definition at line 559 of file QuarkNcSocId.h.

| #define B_QNC_LPC_BIOS_CNTL_BCD (BIT2) |

Definition at line 614 of file QuarkNcSocId.h.

| #define B_QNC_LPC_BIOS_CNTL_BIOSWE (BIT0) |

Definition at line 616 of file QuarkNcSocId.h.

| #define B_QNC_LPC_BIOS_CNTL_BLE (BIT1) |

Definition at line 615 of file QuarkNcSocId.h.

| #define B_QNC_LPC_BIOS_CNTL_PFE (BIT8) |

Definition at line 612 of file QuarkNcSocId.h.

| #define B_QNC_LPC_BIOS_CNTL_SMM_BWP (BIT5) |

Definition at line 613 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_C0 (BIT24) |

Definition at line 608 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_C8 (BIT25) |

Definition at line 607 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_D0 (BIT26) |

Definition at line 606 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_D8 (BIT27) |

Definition at line 605 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_E0 (BIT28) |

Definition at line 604 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_E8 (BIT29) |

Definition at line 603 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_F0 (BIT30) |

Definition at line 602 of file QuarkNcSocId.h.

| #define B_QNC_LPC_FWH_BIOS_DEC_F8 (BIT31) |

Definition at line 601 of file QuarkNcSocId.h.

| #define B_QNC_LPC_GPA_BASE_MASK 0x0000FFC0 |

Definition at line 462 of file QuarkNcSocId.h.

| #define B_QNC_LPC_GPE0BLK_MASK 0x0000FFC0 |

Definition at line 521 of file QuarkNcSocId.h.

| #define B_QNC_LPC_PM1BLK_MASK 0x0000FFF0 |

Definition at line 487 of file QuarkNcSocId.h.

| #define B_QNC_LPC_RCBA_EN (BIT0) |

Definition at line 622 of file QuarkNcSocId.h.

| #define B_QNC_LPC_RCBA_MASK 0xFFFFC000 |

Definition at line 621 of file QuarkNcSocId.h.

| #define B_QNC_LPC_SMBUS_BASE_EN (BIT31) |

Definition at line 427 of file QuarkNcSocId.h.

| #define B_QNC_LPC_SMBUS_BASE_MASK 0x0000FFC0 |

Definition at line 428 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_CCFG_UNRS (BIT15) |

Definition at line 748 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_CCFG_UPRS (BIT14) |

Definition at line 749 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_CCFG_UPSD (BIT24) |

Definition at line 747 of file QuarkNcSocId.h.

Definition at line 702 of file QuarkNcSocId.h.

Definition at line 700 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_DCTL_CEE (BIT0) |

Definition at line 708 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_DCTL_FEE (BIT2) |

Definition at line 706 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_DCTL_NFE (BIT1) |

Definition at line 707 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_DCTL_URE (BIT3) |

Definition at line 705 of file QuarkNcSocId.h.

Definition at line 762 of file QuarkNcSocId.h.

Definition at line 760 of file QuarkNcSocId.h.

Definition at line 715 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_LCAP_CPM (BIT18) |

Definition at line 710 of file QuarkNcSocId.h.

Definition at line 713 of file QuarkNcSocId.h.

Definition at line 712 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_LCTL_CCC (BIT6) |

Definition at line 718 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_LCTL_RL (BIT5) |

Definition at line 719 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_LSTS_LT (BIT11) |

Definition at line 722 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_LSTS_SCC (BIT12) |

Definition at line 721 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_MPC2_IPF (BIT11) |

Definition at line 751 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_MPC_HPCE (BIT30) |

Definition at line 754 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_MPC_HPME (BIT1) |

Definition at line 756 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_MPC_PMCE (BIT31) |

Definition at line 753 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_MPC_PMME (BIT0) |

Definition at line 757 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_RCTL_PIE (BIT3) |

Definition at line 740 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_RCTL_SCE (BIT0) |

Definition at line 743 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_RCTL_SFE (BIT2) |

Definition at line 741 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_RCTL_SNE (BIT1) |

Definition at line 742 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLCAP_MASK_RSV_VALUE 0x0006007F |

Definition at line 724 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLCTL_ABE (BIT0) |

Definition at line 733 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLCTL_HPE (BIT5) |

Definition at line 731 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLCTL_PDE (BIT3) |

Definition at line 732 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLSTS_ABP (BIT0) |

Definition at line 737 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLSTS_PDC (BIT3) |

Definition at line 736 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_SLSTS_PDS (BIT6) |

Definition at line 735 of file QuarkNcSocId.h.

| #define B_QNC_PCIE_XCAP_SI (BIT8) |

Definition at line 697 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1C_SCIEN (BIT0) |

Definition at line 516 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1C_SLPEN (BIT13) |

Definition at line 510 of file QuarkNcSocId.h.

Definition at line 511 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1E_GLOB (BIT5) |

Definition at line 506 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1E_PWAKED (BIT14) |

Definition at line 504 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1E_RTC (BIT10) |

Definition at line 505 of file QuarkNcSocId.h.

Definition at line 494 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1S_GLOB (BIT5) |

Definition at line 498 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1S_PCIEWSTS (BIT14) |

Definition at line 496 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1S_RTC (BIT10) |

Definition at line 497 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1S_TO (BIT0) |

Definition at line 499 of file QuarkNcSocId.h.

| #define B_QNC_PM1BLK_PM1S_WAKE (BIT15) |

Definition at line 495 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIA_MASK 0x00FFFFFF |

Definition at line 800 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIC_ACS (BIT2) |

Definition at line 796 of file QuarkNcSocId.h.

Definition at line 794 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIC_DBC 0x3F00 |

Definition at line 792 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIC_DC (BIT14) |

Definition at line 791 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIC_SCGO (BIT1) |

Definition at line 797 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIC_SPOP (BIT3) |

Definition at line 795 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIOPTYPE_ADD_READ (BIT1) |

Definition at line 809 of file QuarkNcSocId.h.

Definition at line 810 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIOPTYPE_NOADD_READ 0 |

Definition at line 807 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIOPTYPE_NOADD_WRITE (BIT0) |

Definition at line 808 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIPBRn_WPE (BIT31) |

Definition at line 819 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIS_BAS (BIT3) |

Definition at line 786 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIS_CDS (BIT2) |

Definition at line 787 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIS_SCIP (BIT0) |

Definition at line 788 of file QuarkNcSocId.h.

| #define B_QNC_RCRB_SPIS_SCL (BIT15) |

Definition at line 785 of file QuarkNcSocId.h.

| #define B_QNC_SMBUS_BERR (BIT2) |

Definition at line 443 of file QuarkNcSocId.h.

| #define B_QNC_SMBUS_BYTE_DONE_STS (BIT0) |

Definition at line 445 of file QuarkNcSocId.h.

| #define B_QNC_SMBUS_DERR (BIT1) |

Definition at line 444 of file QuarkNcSocId.h.

| #define B_QNC_SMBUS_HSTS_ALL 0x07 |

Definition at line 446 of file QuarkNcSocId.h.

| #define B_QNC_SMBUS_START (BIT4) |

Definition at line 434 of file QuarkNcSocId.h.

| #define B_ROM_FUSE_IN_SECURE_SKU BIT6 |

Definition at line 326 of file QuarkNcSocId.h.

| #define B_RST_CNT_COLD_RST (BIT3) |

Definition at line 665 of file QuarkNcSocId.h.

| #define B_RST_CNT_WARM_RST (BIT1) |

Definition at line 666 of file QuarkNcSocId.h.

| #define B_STPDDRCFG_FORCE_RECOVERY BIT0 |

Definition at line 324 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_IBGCHOPEN BIT18 |

Definition at line 336 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_IBGCHOPEN_BP 18 |

Definition at line 337 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_IBGEN BIT17 |

Definition at line 334 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_IBGEN_BP 17 |

Definition at line 335 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_ISNSCHOPSEL_BP 8 |

Definition at line 333 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_ISNSCHOPSEL_MASK |

Definition at line 331 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_ISNSCURRENTSEL_BP 3 |

Definition at line 330 of file QuarkNcSocId.h.

Definition at line 329 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_ISNSINTERNALVREFEN BIT14 |

Definition at line 338 of file QuarkNcSocId.h.

| #define B_TSCGF1_CONFIG_ISNSINTERNALVREFEN_BP 14 |

Definition at line 339 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG2_ICALCOARSETUNE_BP 0 |

Definition at line 353 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG2_ICALCOARSETUNE_MASK 0x000000FF |

Definition at line 352 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG2_ICALCONFIGSEL_BP 8 |

Definition at line 351 of file QuarkNcSocId.h.

Definition at line 350 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG2_ISPARECTRL_BP 24 |

Definition at line 349 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG2_ISPARECTRL_MASK 0xFF000000 |

Definition at line 348 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG_IDSCONTROL_BP 0 |

Definition at line 343 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG_IDSCONTROL_MASK 0x0000FFFF |

Definition at line 342 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG_IDSTIMING_BP 16 |

Definition at line 345 of file QuarkNcSocId.h.

| #define B_TSCGF2_CONFIG_IDSTIMING_MASK 0xFFFF0000 |

Definition at line 344 of file QuarkNcSocId.h.

| #define B_TSCGF3_CONFIG_ITSGAMMACOEFF_BP 11 |

Definition at line 357 of file QuarkNcSocId.h.

| #define B_TSCGF3_CONFIG_ITSGAMMACOEFF_MASK (0xFFF << B_TSCGF3_CONFIG_ITSGAMMACOEFF_BP) |

Definition at line 358 of file QuarkNcSocId.h.

| #define B_TSCGF3_CONFIG_ITSRST BIT0 |

Definition at line 356 of file QuarkNcSocId.h.

| #define B_WDT_CONTROL_DBL_ECC_BIT_ERR_BP 18 |

Definition at line 181 of file QuarkNcSocId.h.

Definition at line 180 of file QuarkNcSocId.h.

| #define BIT0 0x00000001 |

Definition at line 19 of file QuarkNcSocId.h.

| #define BIT1 0x00000002 |

Definition at line 20 of file QuarkNcSocId.h.

| #define BIT10 0x00000400 |

Definition at line 29 of file QuarkNcSocId.h.

| #define BIT11 0x00000800 |

Definition at line 30 of file QuarkNcSocId.h.

| #define BIT12 0x00001000 |

Definition at line 31 of file QuarkNcSocId.h.

| #define BIT13 0x00002000 |

Definition at line 32 of file QuarkNcSocId.h.

| #define BIT14 0x00004000 |

Definition at line 33 of file QuarkNcSocId.h.

| #define BIT15 0x00008000 |

Definition at line 34 of file QuarkNcSocId.h.

| #define BIT16 0x00010000 |

Definition at line 35 of file QuarkNcSocId.h.

| #define BIT17 0x00020000 |

Definition at line 36 of file QuarkNcSocId.h.

| #define BIT18 0x00040000 |

Definition at line 37 of file QuarkNcSocId.h.

| #define BIT19 0x00080000 |

Definition at line 38 of file QuarkNcSocId.h.

| #define BIT2 0x00000004 |

Definition at line 21 of file QuarkNcSocId.h.

| #define BIT20 0x00100000 |

Definition at line 39 of file QuarkNcSocId.h.

| #define BIT21 0x00200000 |

Definition at line 40 of file QuarkNcSocId.h.

| #define BIT22 0x00400000 |

Definition at line 41 of file QuarkNcSocId.h.

| #define BIT23 0x00800000 |

Definition at line 42 of file QuarkNcSocId.h.

| #define BIT24 0x01000000 |

Definition at line 43 of file QuarkNcSocId.h.

| #define BIT25 0x02000000 |

Definition at line 44 of file QuarkNcSocId.h.

| #define BIT26 0x04000000 |

Definition at line 45 of file QuarkNcSocId.h.

| #define BIT27 0x08000000 |

Definition at line 46 of file QuarkNcSocId.h.

| #define BIT28 0x10000000 |

Definition at line 47 of file QuarkNcSocId.h.

| #define BIT29 0x20000000 |

Definition at line 48 of file QuarkNcSocId.h.

| #define BIT3 0x00000008 |

Definition at line 22 of file QuarkNcSocId.h.

| #define BIT30 0x40000000 |

Definition at line 49 of file QuarkNcSocId.h.

| #define BIT31 0x80000000 |

Definition at line 50 of file QuarkNcSocId.h.

| #define BIT4 0x00000010 |

Definition at line 23 of file QuarkNcSocId.h.

| #define BIT5 0x00000020 |

Definition at line 24 of file QuarkNcSocId.h.

| #define BIT6 0x00000040 |

Definition at line 25 of file QuarkNcSocId.h.

| #define BIT7 0x00000080 |

Definition at line 26 of file QuarkNcSocId.h.

| #define BIT8 0x00000100 |

Definition at line 27 of file QuarkNcSocId.h.

| #define BIT9 0x00000200 |

Definition at line 28 of file QuarkNcSocId.h.

| #define BLOCK_DISABLE_PG (1 << 29) |

Definition at line 230 of file QuarkNcSocId.h.

| #define BLOCK_ENABLE_PG (1 << 28) |

Definition at line 229 of file QuarkNcSocId.h.

| #define CPU0_NON_SMM BIT0 |

Definition at line 261 of file QuarkNcSocId.h.

| #define CPU_SNOOP BIT30 |

Definition at line 259 of file QuarkNcSocId.h.

| #define DRAM_NON_HOST_RQ_LIMIT_BP 0 |

Definition at line 236 of file QuarkNcSocId.h.

| #define DRAM_NON_HOST_RQ_LIMIT_MASK (0x3f << DRAM_NON_HOST_RQ_LIMIT_BP) |

Definition at line 237 of file QuarkNcSocId.h.

| #define EnableIMRInt BIT31 |

Definition at line 232 of file QuarkNcSocId.h.

| #define EnableSMMInt BIT31 |

Definition at line 234 of file QuarkNcSocId.h.

| #define ESEG_RD_DRAM (BIT1) |

Definition at line 271 of file QuarkNcSocId.h.

| #define FSEG_RD_DRAM (BIT2) |

Definition at line 269 of file QuarkNcSocId.h.

| #define HLEGACY_SMI_PIN_VALUE BIT12 |

Definition at line 287 of file QuarkNcSocId.h.

| #define HMBOUND_LOCK BIT0 |

Definition at line 285 of file QuarkNcSocId.h.

| #define HMBOUND_MASK 0x0FFFFF000 |

Definition at line 284 of file QuarkNcSocId.h.

| #define IMR_EN BIT30 |

Definition at line 250 of file QuarkNcSocId.h.

| #define IMR_LOCK BIT31 |

Definition at line 249 of file QuarkNcSocId.h.

| #define IMRH_MASK 0x00FFFFFC |

Definition at line 254 of file QuarkNcSocId.h.

| #define IMRH_RESET 0x00000000 |

Definition at line 255 of file QuarkNcSocId.h.

| #define IMRL_MASK 0x00FFFFFC |

Definition at line 251 of file QuarkNcSocId.h.

| #define IMRL_RESET 0x00000000 |

Definition at line 252 of file QuarkNcSocId.h.

| #define IMRX_ALL_ACCESS 0xFFFFFFFF |

Definition at line 258 of file QuarkNcSocId.h.

| #define IOAPIC_BASE 0xFEC00000 |

Definition at line 774 of file QuarkNcSocId.h.

| #define IOAPIC_SIZE 0x1000 |

Definition at line 775 of file QuarkNcSocId.h.

Definition at line 101 of file QuarkNcSocId.h.

| #define MAX_PCI_EXPRESS_ROOT_PORTS 2 |

Definition at line 683 of file QuarkNcSocId.h.

| #define MC_BUS PCI_BUS_NUMBER_QNC |

Definition at line 60 of file QuarkNcSocId.h.

| #define MC_DEV 0x00 |

Definition at line 61 of file QuarkNcSocId.h.

| #define MC_FUN 0x00 |

Definition at line 62 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_GPE0E_THRM 12 |

Definition at line 537 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_GPE0S_THRM 12 |

Definition at line 530 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIE_APM 4 |

Definition at line 547 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIE_ESMI 8 |

Definition at line 546 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIE_GPIO 9 |

Definition at line 545 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIE_SLP 2 |

Definition at line 549 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIE_SPI 3 |

Definition at line 548 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIE_SWT 1 |

Definition at line 550 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIS_APM 4 |

Definition at line 562 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIS_GPIO 9 |

Definition at line 561 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIS_SLP 2 |

Definition at line 564 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIS_SPI 3 |

Definition at line 563 of file QuarkNcSocId.h.

| #define N_QNC_GPE0BLK_SMIS_SWT 1 |

Definition at line 565 of file QuarkNcSocId.h.

| #define N_QNC_LPC_BIOS_CNTL_BIOSWE 0 |

Definition at line 618 of file QuarkNcSocId.h.

| #define N_QNC_LPC_BIOS_CNTL_BLE 1 |

Definition at line 617 of file QuarkNcSocId.h.

| #define N_QNC_PM1BLK_PM1E_RTC 10 |

Definition at line 507 of file QuarkNcSocId.h.

| #define N_QNC_PM1BLK_PM1S_RTC 10 |

Definition at line 500 of file QuarkNcSocId.h.

| #define NON_HOST_SMM_RD_OPEN (BIT17) |

Definition at line 275 of file QuarkNcSocId.h.

| #define NON_HOST_SMM_WR_OPEN (BIT18) |

Definition at line 274 of file QuarkNcSocId.h.

| #define OCFGPIMIXLOAD_1_0 BIT6 |

Definition at line 404 of file QuarkNcSocId.h.

| #define OCFGPIMIXLOAD_1_0_MASK 0xFFFFFF3F |

Definition at line 405 of file QuarkNcSocId.h.

| #define OPTIONS_1_DMA_DISABLE (BIT0) |

Definition at line 177 of file QuarkNcSocId.h.

| #define PCI_BUS_NUMBER_QNC 0x00 |

Definition at line 412 of file QuarkNcSocId.h.

| #define PCI_DEVICE_NUMBER_PCIE_ROOTPORT 23 |

Definition at line 679 of file QuarkNcSocId.h.

| #define PCI_DEVICE_NUMBER_QNC_IOSF2AHB_0 20 |

Definition at line 672 of file QuarkNcSocId.h.

| #define PCI_DEVICE_NUMBER_QNC_IOSF2AHB_1 21 |

Definition at line 673 of file QuarkNcSocId.h.

| #define PCI_DEVICE_NUMBER_QNC_LPC 31 |

Definition at line 417 of file QuarkNcSocId.h.

| #define PCI_FUNCTION_NUMBER_PCIE_ROOTPORT_0 0 |

Definition at line 680 of file QuarkNcSocId.h.

| #define PCI_FUNCTION_NUMBER_PCIE_ROOTPORT_1 1 |

Definition at line 681 of file QuarkNcSocId.h.

| #define PCI_FUNCTION_NUMBER_QNC_IOSF2AHB 0 |

Definition at line 674 of file QuarkNcSocId.h.

| #define PCI_FUNCTION_NUMBER_QNC_LPC 0 |

Definition at line 418 of file QuarkNcSocId.h.

| #define PCIE_CAP_EXT_HEARDER_OFFSET 0x100 |

Definition at line 689 of file QuarkNcSocId.h.

| #define PCIE_CAPID 0x10 |

Definition at line 688 of file QuarkNcSocId.h.

| #define PCIE_DEV_CAP_OFFSET 0x04 |

Definition at line 690 of file QuarkNcSocId.h.

| #define PCIE_LINK_CAP_OFFSET 0x0C |

Definition at line 691 of file QuarkNcSocId.h.

| #define PCIE_LINK_CNT_OFFSET 0x10 |

Definition at line 692 of file QuarkNcSocId.h.

| #define PCIE_LINK_STS_OFFSET 0x12 |

Definition at line 693 of file QuarkNcSocId.h.

| #define PCIE_SLOT_CAP_OFFSET 0x14 |

Definition at line 694 of file QuarkNcSocId.h.

| #define QNC_ACCESS_PORT_MCR 0xD0 |

Definition at line 77 of file QuarkNcSocId.h.

| #define QNC_ACCESS_PORT_MDR 0xD4 |

Definition at line 85 of file QuarkNcSocId.h.

| #define QNC_ACCESS_PORT_MEA 0xD8 |

Definition at line 90 of file QuarkNcSocId.h.

| #define QNC_MC_REV_ID_A0 0x00 |

Definition at line 67 of file QuarkNcSocId.h.

| #define QNC_MCR_BYTE_ENABLES 0x000000f0 |

Definition at line 80 of file QuarkNcSocId.h.

| #define QNC_MCR_MASK 0x000000ff |

Definition at line 79 of file QuarkNcSocId.h.

| #define QNC_MCR_OP_OFFSET 24 |

Definition at line 93 of file QuarkNcSocId.h.

| #define QNC_MCR_PORT_OFFSET 16 |

Definition at line 94 of file QuarkNcSocId.h.

| #define QNC_MCR_REG_OFFSET 8 |

Definition at line 95 of file QuarkNcSocId.h.

| #define QNC_MEA_MASK 0xffffff00 |

Definition at line 91 of file QuarkNcSocId.h.

| #define QNC_MSG_FSBIC_REG_HMISC 0x03 |

Definition at line 266 of file QuarkNcSocId.h.

| #define QNC_MSG_FSBIC_REG_HSMMC 0x04 |

Definition at line 273 of file QuarkNcSocId.h.

| #define QNC_MSG_TMPM_REG_PMBA 0x70 |

Definition at line 170 of file QuarkNcSocId.h.

| #define QNC_NUMBER_PIRQS 8 |

Definition at line 579 of file QuarkNcSocId.h.

| #define QUARK2_MC_DEVICE_ID 0x12C0 |

Definition at line 66 of file QuarkNcSocId.h.

| #define QUARK_ALT_OPCODE_READ 0x06 |

Definition at line 112 of file QuarkNcSocId.h.

| #define QUARK_ALT_OPCODE_WRITE 0x07 |

Definition at line 113 of file QuarkNcSocId.h.

| #define QUARK_DRAM_BASE_ADDR_READY 0x78 |

Definition at line 121 of file QuarkNcSocId.h.

| #define QUARK_ECC_SCRUB_PAUSE 0xC3 |

Definition at line 125 of file QuarkNcSocId.h.

| #define QUARK_ECC_SCRUB_RESUME 0xC2 |

Definition at line 124 of file QuarkNcSocId.h.

| #define QUARK_ICLK_MUXTOP 0x0140 |

Definition at line 388 of file QuarkNcSocId.h.

| #define QUARK_ICLK_REF2_DBUFF0 0x2000 |

Definition at line 397 of file QuarkNcSocId.h.

| #define QUARK_ICLK_SB_PORT_ID 0x32 |

Definition at line 140 of file QuarkNcSocId.h.

| #define QUARK_ICLK_SSC1 0x0314 |

Definition at line 394 of file QuarkNcSocId.h.

| #define QUARK_ICLK_SSC2 0x0414 |

Definition at line 395 of file QuarkNcSocId.h.

| #define QUARK_ICLK_SSC3 0x0514 |

Definition at line 396 of file QuarkNcSocId.h.

| #define QUARK_MC_DEVICE_ID 0x0958 |

Definition at line 65 of file QuarkNcSocId.h.

| #define QUARK_MC_VENDOR_ID V_INTEL_VENDOR_ID |

Definition at line 64 of file QuarkNcSocId.h.

| #define QUARK_NC_ECC_SCRUB_CONFIG_REG 0x50 |

Definition at line 203 of file QuarkNcSocId.h.

| #define QUARK_NC_ECC_SCRUB_END_MEM_REG 0x77 |

Definition at line 212 of file QuarkNcSocId.h.

| #define QUARK_NC_ECC_SCRUB_NEXT_READ_REG 0x7C |

Definition at line 213 of file QuarkNcSocId.h.

| #define QUARK_NC_ECC_SCRUB_START_MEM_REG 0x76 |

Definition at line 211 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_HLEGACY_REG 0x0A |

Definition at line 286 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_HMBOUND_REG 0x08 |

Definition at line 283 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_CAP 0x40 |

Definition at line 288 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_DEF_TYPE 0x41 |

Definition at line 289 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE0 0x5A |

Definition at line 303 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE1 0x5C |

Definition at line 305 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE2 0x5E |

Definition at line 307 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE3 0x60 |

Definition at line 309 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE4 0x62 |

Definition at line 311 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE5 0x64 |

Definition at line 313 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE6 0x66 |

Definition at line 315 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSBASE7 0x68 |

Definition at line 317 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK0 0x5B |

Definition at line 304 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK1 0x5D |

Definition at line 306 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK2 0x5F |

Definition at line 308 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK3 0x61 |

Definition at line 310 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK4 0x63 |

Definition at line 312 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK5 0x65 |

Definition at line 314 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK6 0x67 |

Definition at line 316 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_PHYSMASK7 0x69 |

Definition at line 318 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_SMRR_PHYSBASE 0x58 |

Definition at line 301 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_IA32_MTRR_SMRR_PHYSMASK 0x59 |

Definition at line 302 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX16K_80000 0x44 |

Definition at line 291 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX16K_A0000 0x46 |

Definition at line 292 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_C0000 0x48 |

Definition at line 293 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_C8000 0x4A |

Definition at line 294 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_D0000 0x4C |

Definition at line 295 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_D8000 0x4E |

Definition at line 296 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_E0000 0x50 |

Definition at line 297 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_E8000 0x52 |

Definition at line 298 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_F0000 0x54 |

Definition at line 299 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX4K_F8000 0x56 |

Definition at line 300 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_MTRR_FIX64K_00000 0x42 |

Definition at line 290 of file QuarkNcSocId.h.

| #define QUARK_NC_HOST_BRIDGE_SB_PORT_ID 0x03 |

Definition at line 133 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_ARBITER_REG_ASTATUS 0x21 |

Definition at line 146 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_ARBITER_SB_PORT_ID 0x00 |

Definition at line 131 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_CONTROLLER_REG_DFUSESTAT 0x70 |

Definition at line 164 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_CONTROLLER_SB_PORT_ID 0x01 |

Definition at line 132 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_BIMRVCTL 0x19 |

Definition at line 231 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_BSMMVCTL 0x1C |

Definition at line 233 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_BTHCTRL 0x20 |

Definition at line 235 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_ESRAMPGCTRL_BLOCK 0x82 |

Definition at line 228 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR0 0x40 |

Definition at line 240 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR1 0x44 |

Definition at line 241 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR2 0x48 |

Definition at line 242 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR3 0x4C |

Definition at line 243 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR4 0x50 |

Definition at line 244 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR5 0x54 |

Definition at line 245 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR6 0x58 |

Definition at line 246 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMR7 0x5C |

Definition at line 247 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMRXH 0x01 |

Definition at line 253 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMRXL 0x00 |

Definition at line 248 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMRXRM 0x02 |

Definition at line 256 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_IMRXWM 0x03 |

Definition at line 257 of file QuarkNcSocId.h.

| #define QUARK_NC_MEMORY_MANAGER_SB_PORT_ID 0x05 |

Definition at line 135 of file QuarkNcSocId.h.

| #define QUARK_NC_RMU_REG_CONFIG 0x71 |

Definition at line 172 of file QuarkNcSocId.h.

| #define QUARK_NC_RMU_REG_OPTIONS_1 0x72 |

Definition at line 176 of file QuarkNcSocId.h.

| #define QUARK_NC_RMU_REG_TS_MODE 0xB0 |

Definition at line 190 of file QuarkNcSocId.h.

| #define QUARK_NC_RMU_REG_TS_TRIP 0xB2 |

Definition at line 192 of file QuarkNcSocId.h.

| #define QUARK_NC_RMU_REG_WDT_CONTROL 0x74 |

Definition at line 179 of file QuarkNcSocId.h.

| #define QUARK_NC_RMU_SB_PORT_ID 0x04 |

Definition at line 134 of file QuarkNcSocId.h.

| #define QUARK_NC_TOTAL_IMR_SET 0x8 |

Definition at line 239 of file QuarkNcSocId.h.

| #define QUARK_OPCODE_IO_READ 0x02 |

Definition at line 118 of file QuarkNcSocId.h.

| #define QUARK_OPCODE_IO_WRITE 0x03 |

Definition at line 119 of file QuarkNcSocId.h.

| #define QUARK_OPCODE_READ 0x10 |

Definition at line 106 of file QuarkNcSocId.h.

| #define QUARK_OPCODE_WRITE 0x11 |

Definition at line 107 of file QuarkNcSocId.h.

| #define QUARK_PCIE_AFE_PCIE_RXPICTRL0_L0 0x2080 |

Definition at line 402 of file QuarkNcSocId.h.

| #define QUARK_PCIE_AFE_PCIE_RXPICTRL0_L1 0x2180 |

Definition at line 403 of file QuarkNcSocId.h.

| #define QUARK_SC_PCIE_AFE_SB_PORT_ID 0x16 |

Definition at line 137 of file QuarkNcSocId.h.

| #define QUARK_SC_USB_AFE_SB_PORT_ID 0x14 |

Definition at line 136 of file QuarkNcSocId.h.

| #define QUARK_SCSS_CRU_SB_PORT_ID 0x34 |

Definition at line 141 of file QuarkNcSocId.h.

| #define QUARK_SCSS_FUSE_SB_PORT_ID 0x33 |

Definition at line 139 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_CFG_STICKY_RW 0x51 |

Definition at line 370 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_SB_PORT_ID 0x31 |

Definition at line 138 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_SOCCLKEN_CONFIG 0x36 |

Definition at line 368 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_SOCCLKEN_CONFIG 0x36 |

Definition at line 368 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_SPI_ROM_FUSE 0x25 |

Definition at line 325 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_STPDDRCFG 0x00 |

Definition at line 323 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_TSCGF1_CONFIG 0x31 |

Definition at line 328 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_TSCGF2_CONFIG 0x32 |

Definition at line 341 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_TSCGF2_CONFIG2 0x33 |

Definition at line 347 of file QuarkNcSocId.h.

| #define QUARK_SCSS_SOC_UNIT_TSCGF3_CONFIG 0x34 |

Definition at line 355 of file QuarkNcSocId.h.

| #define QUARK_V_LPC_DEVICE_ID_0 0x095E |

Definition at line 423 of file QuarkNcSocId.h.

| #define R_APM_CNT 0xB2 |

Definition at line 659 of file QuarkNcSocId.h.

| #define R_EFI_PCI_SVID 0x2C |

Definition at line 769 of file QuarkNcSocId.h.

| #define R_QNC_GPE0BLK_GPE0E 0x04 |

Definition at line 532 of file QuarkNcSocId.h.

| #define R_QNC_GPE0BLK_GPE0S 0x00 |

Definition at line 524 of file QuarkNcSocId.h.

| #define R_QNC_GPE0BLK_PMCW 0x28 |

Definition at line 567 of file QuarkNcSocId.h.

| #define R_QNC_GPE0BLK_PMSW 0x2C |

Definition at line 570 of file QuarkNcSocId.h.

| #define R_QNC_GPE0BLK_SMIE 0x10 |

Definition at line 539 of file QuarkNcSocId.h.

| #define R_QNC_GPE0BLK_SMIS 0x14 |

Definition at line 552 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGEN_CORE_WELL 0x00 |

Definition at line 467 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGGPE_CORE_WELL 0x14 |

Definition at line 472 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGIO_CORE_WELL 0x04 |

Definition at line 468 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGLVL_CORE_WELL 0x08 |

Definition at line 469 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGSMI_CORE_WELL 0x18 |

Definition at line 473 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGTNE_CORE_WELL 0x10 |

Definition at line 471 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGTPE_CORE_WELL 0x0C |

Definition at line 470 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CGTS_CORE_WELL 0x1C |

Definition at line 474 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_CNMIEN_CORE_WELL 0x40 |

Definition at line 483 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGEN_RESUME_WELL 0x20 |

Definition at line 475 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGGPE_RESUME_WELL 0x34 |

Definition at line 480 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGIO_RESUME_WELL 0x24 |

Definition at line 476 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGLVL_RESUME_WELL 0x28 |

Definition at line 477 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGSMI_RESUME_WELL 0x38 |

Definition at line 481 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGTNE_RESUME_WELL 0x30 |

Definition at line 479 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGTPE_RESUME_WELL 0x2C |

Definition at line 478 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RGTS_RESUME_WELL 0x3C |

Definition at line 482 of file QuarkNcSocId.h.

| #define R_QNC_GPIO_RNMIEN_RESUME_WELL 0x44 |

Definition at line 484 of file QuarkNcSocId.h.

| #define R_QNC_LPC_ACTL 0x58 |

Definition at line 573 of file QuarkNcSocId.h.

| #define R_QNC_LPC_BIOS_CNTL 0xD8 |

Definition at line 610 of file QuarkNcSocId.h.

| #define R_QNC_LPC_DEVICE_ID 0x02 |

Definition at line 422 of file QuarkNcSocId.h.

| #define R_QNC_LPC_FWH_BIOS_DEC 0xD4 |

Definition at line 600 of file QuarkNcSocId.h.

| #define R_QNC_LPC_GBA_BASE 0x44 |

Definition at line 461 of file QuarkNcSocId.h.

| #define R_QNC_LPC_GPE0BLK 0x4C |

Definition at line 520 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQA_ROUT 0x60 |

Definition at line 580 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQB_ROUT 0x61 |

Definition at line 581 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQC_ROUT 0x62 |

Definition at line 582 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQD_ROUT 0x63 |

Definition at line 583 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQE_ROUT 0x64 |

Definition at line 584 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQF_ROUT 0x65 |

Definition at line 585 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQG_ROUT 0x66 |

Definition at line 586 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PIRQH_ROUT 0x67 |

Definition at line 587 of file QuarkNcSocId.h.

| #define R_QNC_LPC_PM1BLK 0x48 |

Definition at line 486 of file QuarkNcSocId.h.

| #define R_QNC_LPC_RCBA 0xF0 |

Definition at line 620 of file QuarkNcSocId.h.

| #define R_QNC_LPC_REV_ID 0x08 |

Definition at line 424 of file QuarkNcSocId.h.

| #define R_QNC_LPC_SMBUS_BASE 0x40 |

Definition at line 426 of file QuarkNcSocId.h.

| #define R_QNC_LPC_VENDOR_ID 0x00 |

Definition at line 420 of file QuarkNcSocId.h.

| #define R_QNC_LPC_WDT_WDTCR 0x10 |

Definition at line 596 of file QuarkNcSocId.h.

| #define R_QNC_LPC_WDT_WDTLR 0x18 |

Definition at line 597 of file QuarkNcSocId.h.

| #define R_QNC_LPC_WDTBA 0x84 |

Definition at line 594 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_BNUM 0x18 |

Definition at line 685 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_CAP_PTR 0x34 |

Definition at line 686 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_CCFG 0xD0 |

Definition at line 745 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_DCAP 0x44 |

Definition at line 698 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_DCTL 0x48 |

Definition at line 703 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_IOSFSBCTL 0xF6 |

Definition at line 758 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_LCAP 0x4C |

Definition at line 709 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_LCTL 0x50 |

Definition at line 717 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_LSTS 0x52 |

Definition at line 720 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_MPC 0xD8 |

Definition at line 752 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_MPC2 0xD4 |

Definition at line 750 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_RCTL 0x5C |

Definition at line 738 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_SLCAP 0x54 |

Definition at line 723 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_SLCTL 0x58 |

Definition at line 730 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_SLSTS 0x5A |

Definition at line 734 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_SVID 0x94 |

Definition at line 744 of file QuarkNcSocId.h.

| #define R_QNC_PCIE_XCAP 0x42 |

Definition at line 696 of file QuarkNcSocId.h.

| #define R_QNC_PM1BLK_PM1C 0x04 |

Definition at line 509 of file QuarkNcSocId.h.

| #define R_QNC_PM1BLK_PM1E 0x02 |

Definition at line 502 of file QuarkNcSocId.h.

| #define R_QNC_PM1BLK_PM1S 0x00 |

Definition at line 492 of file QuarkNcSocId.h.

| #define R_QNC_PM1BLK_PM1T 0x08 |

Definition at line 518 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_AGENT0IR 0x3140 |

Definition at line 821 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_AGENT1IR 0x3142 |

Definition at line 822 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_AGENT2IR 0x3144 |

Definition at line 823 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_AGENT3IR 0x3146 |

Definition at line 824 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIA (R_QNC_RCRB_SPIBASE + 0x04) |

Definition at line 799 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIBASE 0x3020 |

Definition at line 783 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIC (R_QNC_RCRB_SPIBASE + 0x02) |

Definition at line 790 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPID0 (R_QNC_RCRB_SPIBASE + 0x08) |

Definition at line 801 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIOPMENU (R_QNC_RCRB_SPIBASE + 0x58) |

Definition at line 812 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIOPTYPE (R_QNC_RCRB_SPIBASE + 0x56) |

Definition at line 805 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIPBR0 (R_QNC_RCRB_SPIBASE + 0x60) |

Definition at line 815 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIPBR1 (R_QNC_RCRB_SPIBASE + 0x64) |

Definition at line 816 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIPBR2 (R_QNC_RCRB_SPIBASE + 0x68) |

Definition at line 817 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIPREOP (R_QNC_RCRB_SPIBASE + 0x54) |

Definition at line 803 of file QuarkNcSocId.h.

| #define R_QNC_RCRB_SPIS (R_QNC_RCRB_SPIBASE + 0x00) |

Definition at line 784 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HBD 0x20 |

Definition at line 458 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HCLK 0x02 |

Definition at line 448 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HCMD 0x05 |

Definition at line 455 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HCTL 0x00 |

Definition at line 433 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HD0 0x06 |

Definition at line 456 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HD1 0x07 |

Definition at line 457 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_HSTS 0x01 |

Definition at line 442 of file QuarkNcSocId.h.

| #define R_QNC_SMBUS_TSA 0x04 |

Definition at line 451 of file QuarkNcSocId.h.

| #define RMU BIT29 |

Definition at line 260 of file QuarkNcSocId.h.

| #define RST_CNT 0xCF9 |

Definition at line 664 of file QuarkNcSocId.h.

| #define S_QNC_GPE0BLK_GPE0E 4 |

Definition at line 533 of file QuarkNcSocId.h.

| #define S_QNC_GPE0BLK_GPE0S 4 |

Definition at line 525 of file QuarkNcSocId.h.

| #define S_QNC_GPE0BLK_SMIE 4 |

Definition at line 540 of file QuarkNcSocId.h.

| #define S_QNC_GPE0BLK_SMIS 4 |

Definition at line 553 of file QuarkNcSocId.h.

| #define S_QNC_LPC_BIOS_CNTL 4 |

Definition at line 611 of file QuarkNcSocId.h.

| #define S_QNC_PM1BLK_PM1E 2 |

Definition at line 503 of file QuarkNcSocId.h.

| #define S_QNC_PM1BLK_PM1S 2 |

Definition at line 493 of file QuarkNcSocId.h.

| #define SCRUB_CFG_ACTIVE (BIT13) |

Definition at line 208 of file QuarkNcSocId.h.

| #define SCRUB_CFG_BLOCKSIZE_MASK 0x1F |

Definition at line 207 of file QuarkNcSocId.h.

| #define SCRUB_CFG_BLOCKSIZE_SHIFT 0x08 |

Definition at line 206 of file QuarkNcSocId.h.

| #define SCRUB_CFG_INTERVAL_MASK 0xFF |

Definition at line 205 of file QuarkNcSocId.h.

| #define SCRUB_CFG_INTERVAL_SHIFT 0x00 |

Definition at line 204 of file QuarkNcSocId.h.

| #define SCRUB_CFG_INVALID 0x00000FFF |

Definition at line 209 of file QuarkNcSocId.h.

| #define SCRUB_PAUSE_MSG | ( | ) |

Definition at line 220 of file QuarkNcSocId.h.

| #define SCRUB_RESUME_MSG | ( | ) |

Definition at line 215 of file QuarkNcSocId.h.

| #define SMI_EN (BIT19) |

Definition at line 267 of file QuarkNcSocId.h.

| #define SMM_CODE_RD_OPEN (BIT16) |

Definition at line 276 of file QuarkNcSocId.h.

| #define SMM_CTL_EN (BIT3) |

Definition at line 277 of file QuarkNcSocId.h.

| #define SMM_END_MASK 0xFFF00000 |

Definition at line 282 of file QuarkNcSocId.h.

| #define SMM_LOCKED (BIT0) |

Definition at line 280 of file QuarkNcSocId.h.

| #define SMM_READ_OPEN (BIT1) |

Definition at line 279 of file QuarkNcSocId.h.

| #define SMM_START_MASK 0x0000FFF0 |

Definition at line 281 of file QuarkNcSocId.h.

| #define SMM_WRITE_OPEN (BIT2) |

Definition at line 278 of file QuarkNcSocId.h.

| #define SOCCLKEN_CONFIG_BB_RST_B BIT16 |

Definition at line 366 of file QuarkNcSocId.h.

| #define SOCCLKEN_CONFIG_PHY_I_CMNRESET_L BIT19 |

Definition at line 363 of file QuarkNcSocId.h.

| #define SOCCLKEN_CONFIG_PHY_I_SIDE_RST_L BIT20 |

Definition at line 362 of file QuarkNcSocId.h.

| #define SOCCLKEN_CONFIG_SBI_BB_RST_B BIT18 |

Definition at line 364 of file QuarkNcSocId.h.

| #define SOCCLKEN_CONFIG_SBI_RST_100_CORE_B BIT17 |

Definition at line 365 of file QuarkNcSocId.h.

| #define TS_CAT_TRIP_CLEAR_THOLD_BP 16 |

Definition at line 196 of file QuarkNcSocId.h.

| #define TS_CAT_TRIP_CLEAR_THOLD_MASK (0xFF << TS_CAT_TRIP_CLEAR_THOLD_BP) |

Definition at line 197 of file QuarkNcSocId.h.

| #define TS_CAT_TRIP_SET_THOLD_BP 0 |

Definition at line 200 of file QuarkNcSocId.h.

| #define TS_CAT_TRIP_SET_THOLD_MASK (0xFF << TS_CAT_TRIP_SET_THOLD_BP) |

Definition at line 201 of file QuarkNcSocId.h.

| #define TS_ENABLE (BIT15) |

Definition at line 191 of file QuarkNcSocId.h.

| #define TS_HOT_TRIP_CLEAR_THOLD_BP 24 |

Definition at line 194 of file QuarkNcSocId.h.

| #define TS_HOT_TRIP_CLEAR_THOLD_MASK (0xFF << TS_HOT_TRIP_CLEAR_THOLD_BP) |

Definition at line 195 of file QuarkNcSocId.h.

| #define TS_HOT_TRIP_SET_THOLD_BP 8 |

Definition at line 198 of file QuarkNcSocId.h.

| #define TS_HOT_TRIP_SET_THOLD_MASK (0xFF << TS_HOT_TRIP_SET_THOLD_BP) |

Definition at line 199 of file QuarkNcSocId.h.

| #define TS_LOCK_AUX_TRIP_PT_REGS_ENABLE (BIT6) |

Definition at line 173 of file QuarkNcSocId.h.

| #define TS_LOCK_THRM_CTRL_REGS_ENABLE (BIT5) |

Definition at line 174 of file QuarkNcSocId.h.

| #define V_INTEL_VENDOR_ID 0x8086 |

Definition at line 410 of file QuarkNcSocId.h.

| #define V_LPC_VENDOR_ID V_INTEL_VENDOR_ID |

Definition at line 421 of file QuarkNcSocId.h.

| #define V_PCIE_MAX_TRY_TIMES 200 |

Definition at line 764 of file QuarkNcSocId.h.

| #define V_QNC_LPC_ACTL_SCIS_IRQ9 0x00 |

Definition at line 574 of file QuarkNcSocId.h.

| #define V_QNC_PCIE_LCAP_APMS_OFFSET 10 |

Definition at line 716 of file QuarkNcSocId.h.

| #define V_QNC_PCIE_SLCAP_PSN_OFFSET 19 |

Definition at line 729 of file QuarkNcSocId.h.

| #define V_QNC_PCIE_SLCAP_SLV 0x0A |

Definition at line 726 of file QuarkNcSocId.h.

| #define V_QNC_PCIE_SLCAP_SLV_OFFSET 7 |

Definition at line 727 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCLK_100KHZ 0x0054 |

Definition at line 449 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCTL_CMD_BLOCK 5 |

Definition at line 440 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCTL_CMD_BYTE 1 |

Definition at line 436 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCTL_CMD_BYTE_DATA 2 |

Definition at line 437 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCTL_CMD_PROCESS_CALL 4 |

Definition at line 439 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCTL_CMD_QUICK 0 |

Definition at line 435 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_HCTL_CMD_WORD_DATA 3 |

Definition at line 438 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_RW_SEL_READ 1 |

Definition at line 452 of file QuarkNcSocId.h.

| #define V_QNC_SMBUS_RW_SEL_WRITE 0 |

Definition at line 453 of file QuarkNcSocId.h.

| #define V_S0 0x00000000 |

Definition at line 512 of file QuarkNcSocId.h.

| #define V_S3 0x00001400 |

Definition at line 513 of file QuarkNcSocId.h.

| #define V_S4 0x00001800 |

Definition at line 514 of file QuarkNcSocId.h.

| #define V_S5 0x00001C00 |

Definition at line 515 of file QuarkNcSocId.h.

| #define V_WDT_CONTROL_DBL_ECC_BIT_ERR_CAT (0x1 << B_WDT_CONTROL_DBL_ECC_BIT_ERR_BP) |

Definition at line 183 of file QuarkNcSocId.h.

| #define V_WDT_CONTROL_DBL_ECC_BIT_ERR_NONE 0 |

Definition at line 182 of file QuarkNcSocId.h.

| #define V_WDT_CONTROL_DBL_ECC_BIT_ERR_SERR (0x3 << B_WDT_CONTROL_DBL_ECC_BIT_ERR_BP) |

Definition at line 187 of file QuarkNcSocId.h.

| #define V_WDT_CONTROL_DBL_ECC_BIT_ERR_WARM (0x2 << B_WDT_CONTROL_DBL_ECC_BIT_ERR_BP) |

Definition at line 185 of file QuarkNcSocId.h.