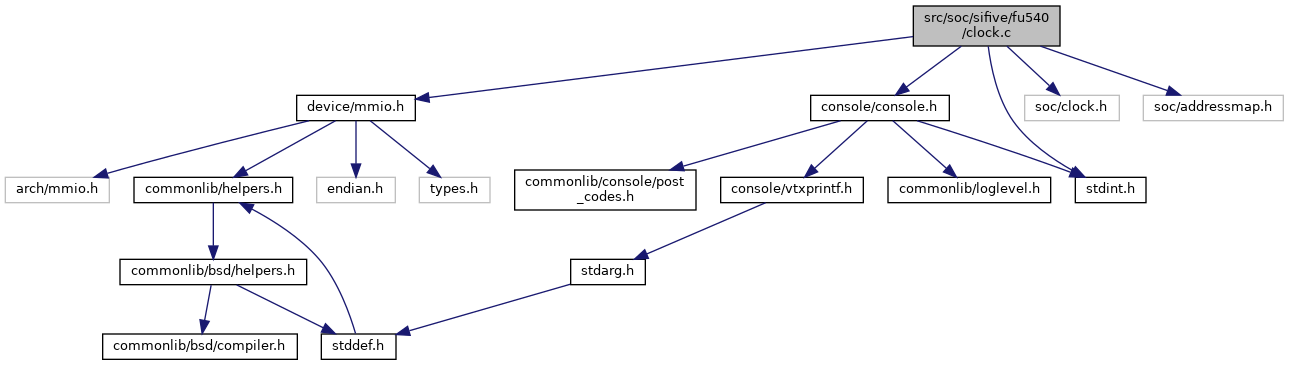

#include <device/mmio.h>

#include <console/console.h>

#include <soc/clock.h>

#include <soc/addressmap.h>

#include <stdint.h>

Go to the source code of this file.

◆ FU540_BASE_FQY

| #define FU540_BASE_FQY 33330 |

◆ PRCI_CORECLK_CORE_PLL

| #define PRCI_CORECLK_CORE_PLL 0 |

◆ PRCI_CORECLK_HFCLK

| #define PRCI_CORECLK_HFCLK 1 |

◆ PRCI_CORECLK_MASK

| #define PRCI_CORECLK_MASK 1 |

◆ PRCI_CORECLKSEL_CORECLKSEL

| #define PRCI_CORECLKSEL_CORECLKSEL 1 |

◆ PRCI_DDRPLLCFG1_MASK

| #define PRCI_DDRPLLCFG1_MASK (1u << 31) |

◆ PRCI_DEVICESRESET_DDR_AHB_RST_N

| #define PRCI_DEVICESRESET_DDR_AHB_RST_N |

( |

|

x | ) |

(((x) & 0x1) << 2) |

◆ PRCI_DEVICESRESET_DDR_AXI_RST_N

| #define PRCI_DEVICESRESET_DDR_AXI_RST_N |

( |

|

x | ) |

(((x) & 0x1) << 1) |

◆ PRCI_DEVICESRESET_DDR_CTRL_RST_N

| #define PRCI_DEVICESRESET_DDR_CTRL_RST_N |

( |

|

x | ) |

(((x) & 0x1) << 0) |

◆ PRCI_DEVICESRESET_DDR_PHY_RST_N

| #define PRCI_DEVICESRESET_DDR_PHY_RST_N |

( |

|

x | ) |

(((x) & 0x1) << 3) |

◆ PRCI_DEVICESRESET_GEMGXL_RST_N

| #define PRCI_DEVICESRESET_GEMGXL_RST_N |

( |

|

x | ) |

(((x) & 0x1) << 5) |

◆ PRCI_GEMGXLPPLCFG1_MASK

| #define PRCI_GEMGXLPPLCFG1_MASK (1u << 31) |

◆ PRCI_PLLCFG_BYPASS_MASK

◆ PRCI_PLLCFG_BYPASS_SHIFT

| #define PRCI_PLLCFG_BYPASS_SHIFT 24 |

◆ PRCI_PLLCFG_DIVF_MASK

◆ PRCI_PLLCFG_DIVF_SHIFT

| #define PRCI_PLLCFG_DIVF_SHIFT 6 |

◆ PRCI_PLLCFG_DIVQ_MASK

◆ PRCI_PLLCFG_DIVQ_SHIFT

| #define PRCI_PLLCFG_DIVQ_SHIFT 15 |

◆ PRCI_PLLCFG_DIVR_MASK

◆ PRCI_PLLCFG_DIVR_SHIFT

| #define PRCI_PLLCFG_DIVR_SHIFT 0 |

◆ PRCI_PLLCFG_FSE_MASK

◆ PRCI_PLLCFG_FSE_SHIFT

| #define PRCI_PLLCFG_FSE_SHIFT 25 |

◆ PRCI_PLLCFG_LOCK

| #define PRCI_PLLCFG_LOCK (1u << 31) |

◆ PRCI_PLLCFG_RANGE_MASK

◆ PRCI_PLLCFG_RANGE_SHIFT

| #define PRCI_PLLCFG_RANGE_SHIFT 18 |

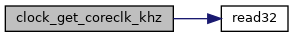

◆ clock_get_coreclk_khz()

| int clock_get_coreclk_khz |

( |

void |

| ) |

|

Definition at line 253 of file clock.c.

References BIOS_SPEW, prci_ctlr::coreclksel, prci_ctlr::corepllcfg0, FU540_BASE_FQY, prci, PRCI_CORECLK_MASK, PRCI_PLLCFG_DIVF_MASK, PRCI_PLLCFG_DIVF_SHIFT, PRCI_PLLCFG_DIVQ_MASK, PRCI_PLLCFG_DIVQ_SHIFT, PRCI_PLLCFG_DIVR_MASK, PRCI_PLLCFG_DIVR_SHIFT, printk, and read32().

Referenced by clock_get_tlclk_khz().

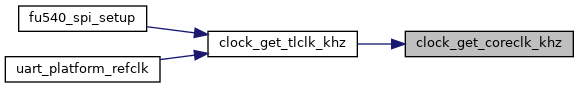

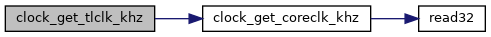

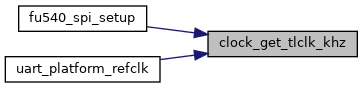

◆ clock_get_tlclk_khz()

| int clock_get_tlclk_khz |

( |

void |

| ) |

|

◆ prci