|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

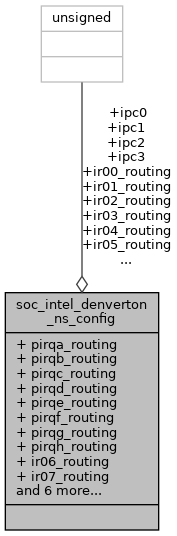

#include <chip.h>

Data Fields | |

| uint8_t | pirqa_routing |

| Interrupt Routing configuration If bit7 is 1, the interrupt is disabled. More... | |

| uint8_t | pirqb_routing |

| uint8_t | pirqc_routing |

| uint8_t | pirqd_routing |

| uint8_t | pirqe_routing |

| uint8_t | pirqf_routing |

| uint8_t | pirqg_routing |

| uint8_t | pirqh_routing |

| uint16_t | ir00_routing |

| Device Interrupt Routing configuration Interrupt Pin x Route. More... | |

| uint16_t | ir01_routing |

| uint16_t | ir02_routing |

| uint16_t | ir03_routing |

| uint16_t | ir04_routing |

| uint16_t | ir05_routing |

| uint16_t | ir06_routing |

| uint16_t | ir07_routing |

| uint16_t | ir08_routing |

| uint16_t | ir09_routing |

| uint16_t | ir10_routing |

| uint16_t | ir11_routing |

| uint16_t | ir12_routing |

| uint32_t | ipc0 |

| Device Interrupt Polarity Control ipc0 - IRQ-00-31 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc1 - IRQ-32-63 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc2 - IRQ-64-95 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc3 - IRQ-96-119 - 1: Active low to IOAPIC, 0: Active high to IOAPIC. More... | |

| uint32_t | ipc1 |

| uint32_t | ipc2 |

| uint32_t | ipc3 |

| uint32_t | tcc_offset |

| uint32_t soc_intel_denverton_ns_config::ipc0 |

Device Interrupt Polarity Control ipc0 - IRQ-00-31 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc1 - IRQ-32-63 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc2 - IRQ-64-95 - 1: Active low to IOAPIC, 0: Active high to IOAPIC ipc3 - IRQ-96-119 - 1: Active low to IOAPIC, 0: Active high to IOAPIC.

| uint16_t soc_intel_denverton_ns_config::ir00_routing |

| uint8_t soc_intel_denverton_ns_config::pirqa_routing |