|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

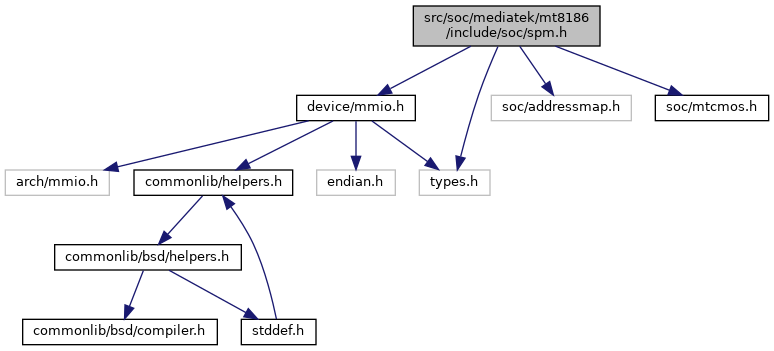

Go to the source code of this file.

Data Structures | |

| struct | mtk_spm_regs |

| struct | pwr_ctrl |

| struct | pcm_desc |

| struct | dyna_load_pcm |

Functions | |

| check_member (mtk_spm_regs, poweron_config_set, 0x0) | |

| check_member (mtk_spm_regs, dis_pwr_con, 0x354) | |

| check_member (mtk_spm_regs, nna_pwr_con, 0x3E0) | |

| check_member (mtk_spm_regs, ap_mdsrc_req, 0x430) | |

| check_member (mtk_spm_regs, ssusb_top_pwr_con, 0x9F0) | |

| check_member (mtk_spm_regs, ssusb_top_p1_pwr_con, 0x9F4) | |

| check_member (mtk_spm_regs, adsp_infra_pwr_con, 0x9F8) | |

| check_member (mtk_spm_regs, adsp_ao_pwr_con, 0x9FC) | |

| int | spm_init (void) |

Variables | |

| static struct mtk_spm_regs *const | mtk_spm = (void *)SPM_BASE |

| static const struct power_domain_data | disp [] |

| static const struct power_domain_data | audio [] |

| #define AP_PLL_CON3 (APMIXED_BASE + 0xC) |

| #define AP_PLL_CON4 (APMIXED_BASE + 0x10) |

| #define INFRA_AO_RES_CTRL_MASK (INFRACFG_AO_BASE + 0xB8) |

| #define ISRC_ALL (ISRC_ALL_EXC_TWAM | ISRC_TWAM) |

| #define ISRC_ALL_EXC_TWAM ISRS_PCM_RETURN |

| #define ISRM_ALL (ISRM_ALL_EXC_TWAM | ISRM_TWAM) |

| #define ISRM_ALL_EXC_TWAM ISRM_RET_IRQ_AUX |

| #define ISRM_RET_IRQ_AUX |

| #define MD32PCM_CFGREG_SW_RSTN (MD32PCM_BASE + 0x0000) |

| #define MD32PCM_DMA0_CON (MD32PCM_BASE + 0x0214) |

| #define MD32PCM_DMA0_COUNT (MD32PCM_BASE + 0x0210) |

| #define MD32PCM_DMA0_DST (MD32PCM_BASE + 0x0204) |

| #define MD32PCM_DMA0_RLCT (MD32PCM_BASE + 0x0224) |

| #define MD32PCM_DMA0_SRC (MD32PCM_BASE + 0x0200) |

| #define MD32PCM_DMA0_START (MD32PCM_BASE + 0x0218) |

| #define MD32PCM_DMA0_WPPT (MD32PCM_BASE + 0x0208) |

| #define MD32PCM_DMA0_WPTO (MD32PCM_BASE + 0x020C) |

| #define MD32PCM_INTC_IRQ_RAW_STA (MD32PCM_BASE + 0x033C) |

| #define PCM_SW_INT_ALL |

| #define PCM_TIMER_MAX (0xffffffff - PCM_WDT_TIMEOUT) |

| #define SPM_REGWR_CFG_KEY (SPM_PROJECT_CODE << 16) |

| check_member | ( | mtk_spm_regs | , |

| adsp_ao_pwr_con | , | ||

| 0x9FC | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| adsp_infra_pwr_con | , | ||

| 0x9F8 | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| ap_mdsrc_req | , | ||

| 0x430 | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| dis_pwr_con | , | ||

| 0x354 | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| nna_pwr_con | , | ||

| 0x3E0 | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| poweron_config_set | , | ||

| 0x0 | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| ssusb_top_p1_pwr_con | , | ||

| 0x9F4 | |||

| ) |

| check_member | ( | mtk_spm_regs | , |

| ssusb_top_pwr_con | , | ||

| 0x9F0 | |||

| ) |

|

static |

|

static |

|

static |