|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

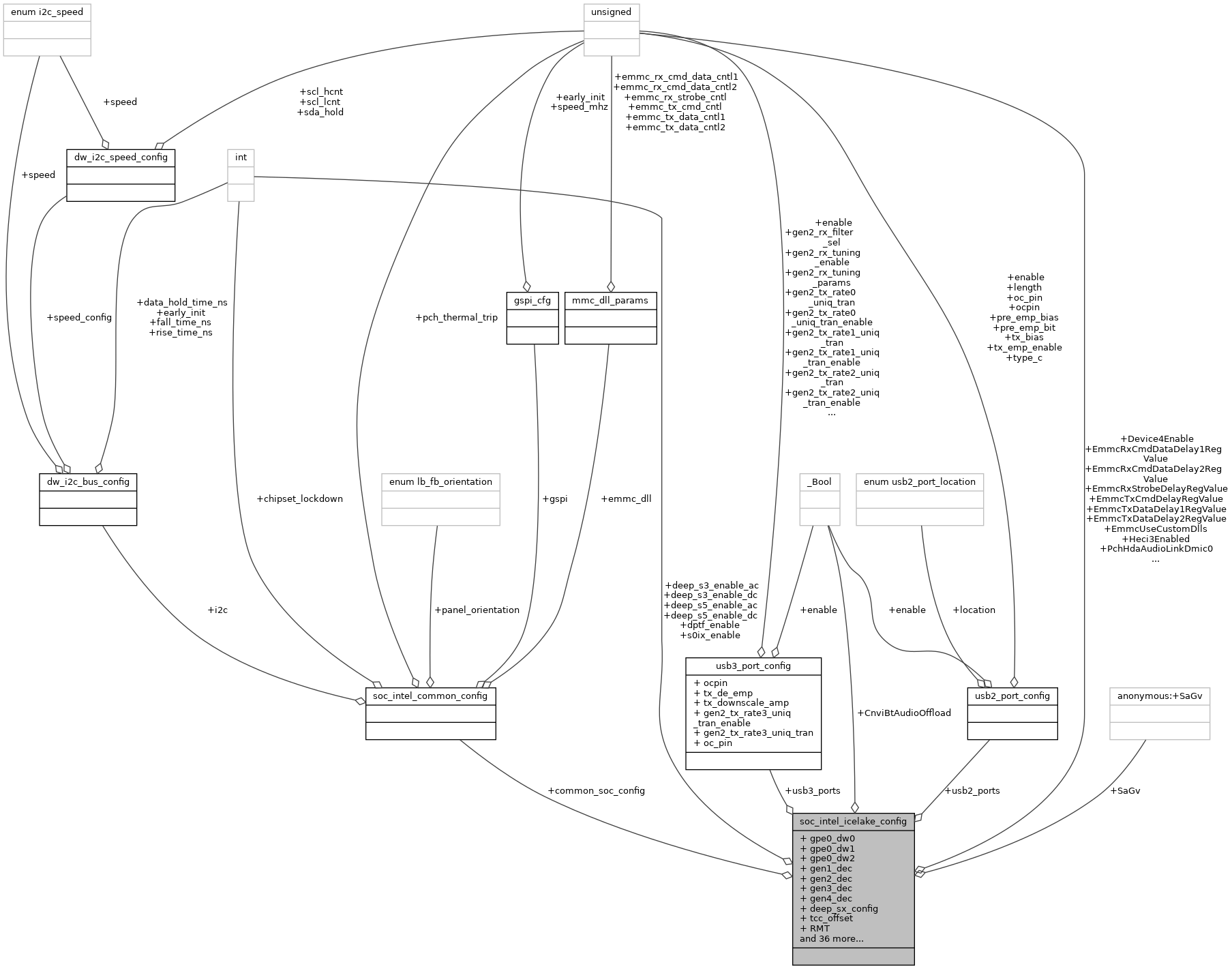

#include <chip.h>

Public Types | |

| enum | { SaGv_Disabled , SaGv_FixedLow , SaGv_FixedMid , SaGv_FixedHigh , SaGv_Enabled } |

| anonymous enum |

| struct soc_intel_common_config soc_intel_icelake_config::common_soc_config |

| uint32_t soc_intel_icelake_config::EmmcRxCmdDataDelay1RegValue |

| uint32_t soc_intel_icelake_config::EmmcRxCmdDataDelay2RegValue |

| uint8_t soc_intel_icelake_config::gpio_pm[TOTAL_GPIO_COMM] |

| uint8_t soc_intel_icelake_config::PcieClkSrcClkReq[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_icelake_config::PcieClkSrcUsage[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_icelake_config::PcieRpEnable[CONFIG_MAX_ROOT_PORTS] |

| enum { ... } soc_intel_icelake_config::SaGv |

| uint8_t soc_intel_icelake_config::SdCardPowerEnableActiveHigh |

| uint8_t soc_intel_icelake_config::SerialIoGSpiCsMode[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_icelake_config::SerialIoGSpiCsState[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_icelake_config::SerialIoGSpiMode[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_icelake_config::SerialIoI2cMode[CONFIG_SOC_INTEL_I2C_DEV_MAX] |

| uint8_t soc_intel_icelake_config::SerialIoUartMode[CONFIG_SOC_INTEL_UART_DEV_MAX] |

| struct usb2_port_config soc_intel_icelake_config::usb2_ports[16] |

| struct usb3_port_config soc_intel_icelake_config::usb3_ports[10] |