|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

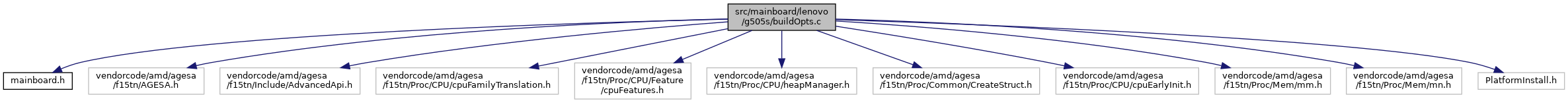

#include "mainboard.h"#include <vendorcode/amd/agesa/f15tn/AGESA.h>#include <vendorcode/amd/agesa/f15tn/Include/AdvancedApi.h>#include <vendorcode/amd/agesa/f15tn/Proc/CPU/cpuFamilyTranslation.h>#include <vendorcode/amd/agesa/f15tn/Proc/CPU/Feature/cpuFeatures.h>#include <vendorcode/amd/agesa/f15tn/Proc/CPU/heapManager.h>#include <vendorcode/amd/agesa/f15tn/Proc/Common/CreateStruct.h>#include <vendorcode/amd/agesa/f15tn/Proc/CPU/cpuEarlyInit.h>#include <vendorcode/amd/agesa/f15tn/Proc/Mem/mm.h>#include <vendorcode/amd/agesa/f15tn/Proc/Mem/mn.h>#include <PlatformInstall.h>

Go to the source code of this file.

Variables | |

| GPIO_CONTROL | lenovo_g505s_gpio [] |

| SCI_MAP_CONTROL | lenovo_g505s_sci_map [] |

| #define BLDCFG_AMD_PLATFORM_TYPE AMD_PLATFORM_MOBILE |

Definition at line 35 of file buildOpts.c.

| #define BLDCFG_CFG_GNB_HD_AUDIO TRUE |

Definition at line 49 of file buildOpts.c.

| #define BLDCFG_ECC_SYNC_FLOOD FALSE |

Definition at line 42 of file buildOpts.c.

| #define BLDCFG_ENABLE_ECC_FEATURE TRUE |

Definition at line 41 of file buildOpts.c.

| #define BLDCFG_FCH_GPIO_CONTROL_LIST (lenovo_g505s_gpio) |

Definition at line 78 of file buildOpts.c.

| #define BLDCFG_FCH_SCI_MAP_LIST (lenovo_g505s_sci_map) |

Definition at line 99 of file buildOpts.c.

| #define BLDCFG_IOMMU_SUPPORT TRUE |

Definition at line 47 of file buildOpts.c.

| #define BLDCFG_MEMORY_CHANNEL_INTERLEAVING TRUE |

Definition at line 40 of file buildOpts.c.

| #define BLDCFG_MEMORY_RDIMM_CAPABLE FALSE |

Definition at line 37 of file buildOpts.c.

| #define BLDCFG_MEMORY_SODIMM_CAPABLE TRUE |

Definition at line 39 of file buildOpts.c.

| #define BLDCFG_MEMORY_UDIMM_CAPABLE TRUE |

Definition at line 38 of file buildOpts.c.

| #define BLDCFG_UMA_ALLOCATION_MODE UMA_SPECIFIED |

Definition at line 44 of file buildOpts.c.

| #define BLDCFG_UMA_ALLOCATION_SIZE 0x2000 /* (0x2000 << 16) = 512M */ |

Definition at line 45 of file buildOpts.c.

| #define BLDOPT_REMOVE_CRAT TRUE |

Definition at line 32 of file buildOpts.c.

| #define BLDOPT_REMOVE_LRDIMMS_SUPPORT TRUE |

Definition at line 28 of file buildOpts.c.

| #define BLDOPT_REMOVE_SRAT FALSE |

Definition at line 30 of file buildOpts.c.

| #define BLDOPT_REMOVE_WHEA FALSE |

Definition at line 31 of file buildOpts.c.

| #define GEVENT_PIN | ( | gpe | ) | ((gpe) + 0x40) |

Definition at line 84 of file buildOpts.c.

| #define INPUT (GpioOutEnB) |

Definition at line 69 of file buildOpts.c.

| #define INSTALL_FAMILY_15_MODEL_1x_SUPPORT TRUE |

Definition at line 20 of file buildOpts.c.

| #define INSTALL_FP2_SOCKET_SUPPORT TRUE |

Definition at line 24 of file buildOpts.c.

| #define INSTALL_FS1_SOCKET_SUPPORT TRUE |

Definition at line 23 of file buildOpts.c.

| #define OUTPUT_HIGH (GpioOut) |

Definition at line 67 of file buildOpts.c.

| #define OUTPUT_LOW (0) |

Definition at line 68 of file buildOpts.c.

| #define PULL_DOWN (PullDown | PullUpB) |

Definition at line 71 of file buildOpts.c.

| #define PULL_NONE (PullUpB) |

Definition at line 72 of file buildOpts.c.

| #define PULL_UP (0) |

Definition at line 70 of file buildOpts.c.

| #define SCI_MAP_OHCI_12_0 0x58 |

Definition at line 85 of file buildOpts.c.

| #define SCI_MAP_OHCI_13_0 0x59 |

Definition at line 86 of file buildOpts.c.

| #define SCI_MAP_PWRBTN 0x73 |

Definition at line 88 of file buildOpts.c.

| #define SCI_MAP_XHCI_10_0 0x78 |

Definition at line 87 of file buildOpts.c.

| GPIO_CONTROL lenovo_g505s_gpio[] |

Definition at line 74 of file buildOpts.c.

| SCI_MAP_CONTROL lenovo_g505s_sci_map[] |

Definition at line 90 of file buildOpts.c.