|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

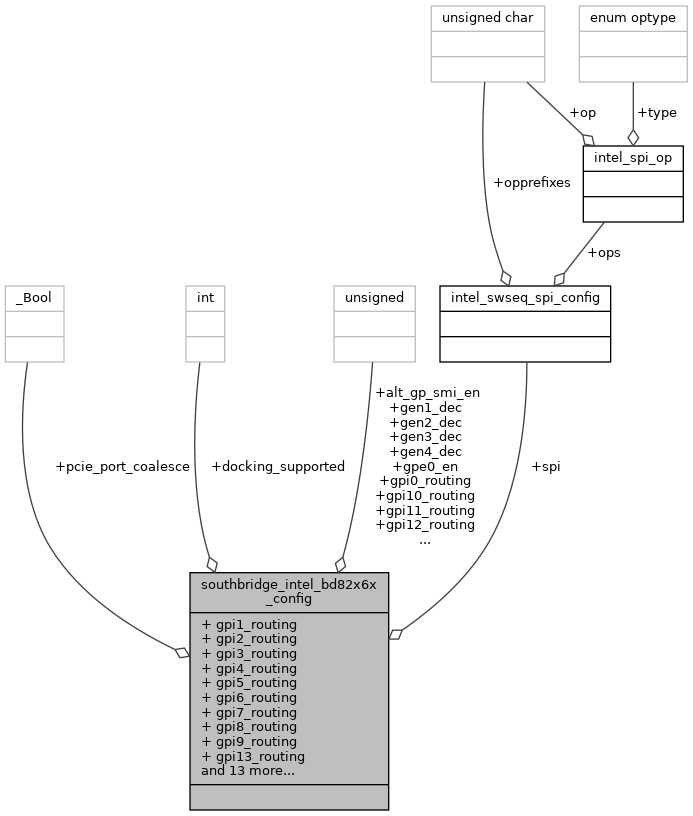

#include <chip.h>

| uint8_t southbridge_intel_bd82x6x_config::gpi0_routing |

| uint8_t southbridge_intel_bd82x6x_config::sata_interface_speed_support |

| struct intel_swseq_spi_config southbridge_intel_bd82x6x_config::spi |

| uint32_t southbridge_intel_bd82x6x_config::superspeed_capable_ports |

| uint32_t southbridge_intel_bd82x6x_config::xhci_overcurrent_mapping |

| uint32_t southbridge_intel_bd82x6x_config::xhci_switchable_ports |