#include <chip.h>

Definition at line 13 of file chip.h.

◆ alt_gp_smi_en

| uint16_t southbridge_intel_i82801ix_config::alt_gp_smi_en |

◆ c4onc3_enable

| unsigned int southbridge_intel_i82801ix_config::c4onc3_enable |

◆ c5_enable

| unsigned int southbridge_intel_i82801ix_config::c5_enable |

◆ c6_enable

| unsigned int southbridge_intel_i82801ix_config::c6_enable |

◆ gen1_dec

| uint32_t southbridge_intel_i82801ix_config::gen1_dec |

◆ gen2_dec

| uint32_t southbridge_intel_i82801ix_config::gen2_dec |

◆ gen3_dec

| uint32_t southbridge_intel_i82801ix_config::gen3_dec |

◆ gen4_dec

| uint32_t southbridge_intel_i82801ix_config::gen4_dec |

◆ gpe0_en

| uint32_t southbridge_intel_i82801ix_config::gpe0_en |

◆ gpi0_routing

| uint8_t southbridge_intel_i82801ix_config::gpi0_routing |

GPI Routing configuration.

Only the lower two bits have a meaning: 00: No effect 01: SMI# (if corresponding ALT_GPI_SMI_EN bit is also set) 10: SCI (if corresponding GPIO_EN bit is also set) 11: reserved

Definition at line 36 of file chip.h.

◆ gpi10_routing

| uint8_t southbridge_intel_i82801ix_config::gpi10_routing |

◆ gpi11_routing

| uint8_t southbridge_intel_i82801ix_config::gpi11_routing |

◆ gpi12_routing

| uint8_t southbridge_intel_i82801ix_config::gpi12_routing |

◆ gpi13_routing

| uint8_t southbridge_intel_i82801ix_config::gpi13_routing |

◆ gpi14_routing

| uint8_t southbridge_intel_i82801ix_config::gpi14_routing |

◆ gpi15_routing

| uint8_t southbridge_intel_i82801ix_config::gpi15_routing |

◆ gpi1_routing

| uint8_t southbridge_intel_i82801ix_config::gpi1_routing |

◆ gpi2_routing

| uint8_t southbridge_intel_i82801ix_config::gpi2_routing |

◆ gpi3_routing

| uint8_t southbridge_intel_i82801ix_config::gpi3_routing |

◆ gpi4_routing

| uint8_t southbridge_intel_i82801ix_config::gpi4_routing |

◆ gpi5_routing

| uint8_t southbridge_intel_i82801ix_config::gpi5_routing |

◆ gpi6_routing

| uint8_t southbridge_intel_i82801ix_config::gpi6_routing |

◆ gpi7_routing

| uint8_t southbridge_intel_i82801ix_config::gpi7_routing |

◆ gpi8_routing

| uint8_t southbridge_intel_i82801ix_config::gpi8_routing |

◆ gpi9_routing

| uint8_t southbridge_intel_i82801ix_config::gpi9_routing |

◆ pcie_hotplug_map

| uint8_t southbridge_intel_i82801ix_config::pcie_hotplug_map[8] |

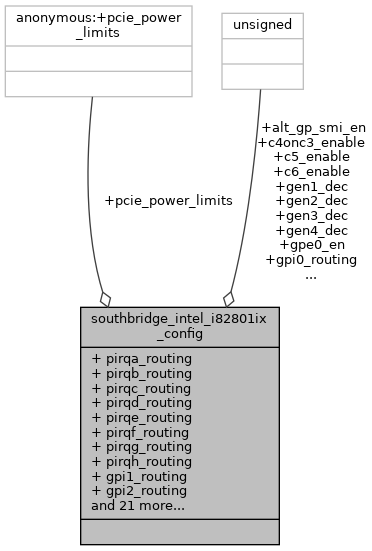

| struct { ... } southbridge_intel_i82801ix_config::pcie_power_limits[6] |

◆ pcie_slot_implemented

| unsigned int southbridge_intel_i82801ix_config::pcie_slot_implemented |

◆ pirqa_routing

| uint8_t southbridge_intel_i82801ix_config::pirqa_routing |

Interrupt Routing configuration If bit7 is 1, the interrupt is disabled.

Definition at line 18 of file chip.h.

◆ pirqb_routing

| uint8_t southbridge_intel_i82801ix_config::pirqb_routing |

◆ pirqc_routing

| uint8_t southbridge_intel_i82801ix_config::pirqc_routing |

◆ pirqd_routing

| uint8_t southbridge_intel_i82801ix_config::pirqd_routing |

◆ pirqe_routing

| uint8_t southbridge_intel_i82801ix_config::pirqe_routing |

◆ pirqf_routing

| uint8_t southbridge_intel_i82801ix_config::pirqf_routing |

◆ pirqg_routing

| uint8_t southbridge_intel_i82801ix_config::pirqg_routing |

◆ pirqh_routing

| uint8_t southbridge_intel_i82801ix_config::pirqh_routing |

◆ sata_clock_request

| unsigned int southbridge_intel_i82801ix_config::sata_clock_request |

◆ sata_port_map

| uint8_t southbridge_intel_i82801ix_config::sata_port_map |

◆ sata_traffic_monitor

| unsigned int southbridge_intel_i82801ix_config::sata_traffic_monitor |

◆ scale

| uint8_t southbridge_intel_i82801ix_config::scale |

◆ throttle_duty

| unsigned int southbridge_intel_i82801ix_config::throttle_duty |

◆ value

| uint8_t southbridge_intel_i82801ix_config::value |

The documentation for this struct was generated from the following file:

- src/southbridge/intel/i82801ix/chip.h