|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

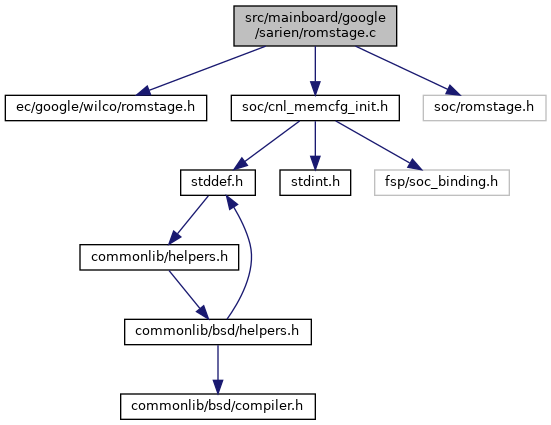

Go to the source code of this file.

Functions | |

| void | mainboard_memory_init_params (FSPM_UPD *memupd) |

Variables | |

| static const struct cnl_mb_cfg | memcfg |

| void mainboard_memory_init_params | ( | FSPM_UPD * | memupd | ) |

Definition at line 45 of file romstage.c.

References cannonlake_memcfg_init(), memcfg, and wilco_ec_romstage_init().

|

static |

Definition at line 1 of file romstage.c.

Referenced by mainboard_memory_init_params().