|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

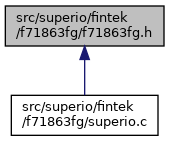

Go to the source code of this file.

Macros | |

| #define | F71863FG_FDC 0x00 /* Floppy */ |

| #define | F71863FG_SP1 0x01 /* UART1 */ |

| #define | F71863FG_SP2 0x02 /* UART2 */ |

| #define | F71863FG_PP 0x03 /* Parallel port */ |

| #define | F71863FG_HWM 0x04 /* Hardware monitor */ |

| #define | F71863FG_KBC 0x05 /* PS/2 keyboard and mouse */ |

| #define | F71863FG_GPIO 0x06 /* General Purpose I/O (GPIO) */ |

| #define | F71863FG_VID 0x07 /* VID */ |

| #define | F71863FG_SPI 0x08 /* SPI */ |

| #define | F71863FG_PME 0x0a /* Power Management Events (PME) and ACPI */ |

| #define F71863FG_FDC 0x00 /* Floppy */ |

Definition at line 7 of file f71863fg.h.

| #define F71863FG_GPIO 0x06 /* General Purpose I/O (GPIO) */ |

Definition at line 13 of file f71863fg.h.

| #define F71863FG_HWM 0x04 /* Hardware monitor */ |

Definition at line 11 of file f71863fg.h.

| #define F71863FG_KBC 0x05 /* PS/2 keyboard and mouse */ |

Definition at line 12 of file f71863fg.h.

| #define F71863FG_PME 0x0a /* Power Management Events (PME) and ACPI */ |

Definition at line 16 of file f71863fg.h.

| #define F71863FG_PP 0x03 /* Parallel port */ |

Definition at line 10 of file f71863fg.h.

| #define F71863FG_SP1 0x01 /* UART1 */ |

Definition at line 8 of file f71863fg.h.

| #define F71863FG_SP2 0x02 /* UART2 */ |

Definition at line 9 of file f71863fg.h.

| #define F71863FG_SPI 0x08 /* SPI */ |

Definition at line 15 of file f71863fg.h.

| #define F71863FG_VID 0x07 /* VID */ |

Definition at line 14 of file f71863fg.h.