|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Macros | |

| #define | ONOFF(cond, reg, bits) ((cond) ? ((reg) | (bits)) : ((reg) & ~(bits))) |

| #define | XBCS 0x4e /* X-Bus chip select register */ |

| #define | GENCFG 0xb0 /* General configuration register */ |

| #define | GPO2223 (1<<28) /* GPO22/23 */ |

| #define | RTCCFG 0xcb /* Real time clock configuration register */ |

| #define | RTC_POS_DECODE (1<<5) |

| #define | UPPER_RAM_EN (1<<2) |

| #define | RTC_ENABLE (1<<0) |

| #define | IDETIM_PRI 0x40 /* IDE timing register, primary channel */ |

| #define | IDETIM_SEC 0x42 /* IDE timing register, secondary channel */ |

| #define | UDMACTL 0x48 /* Ultra DMA/33 control register */ |

| #define | UDMATIM 0x4a /* Ultra DMA/33 timing register */ |

| #define | SMBBA 0x90 /* SMBus base address */ |

| #define | SMBUS_IO_BASE 0x0f00 |

| #define | SMBHSTCFG 0xd2 /* SMBus host configuration */ |

| #define | PMSTS 0x00 /* Power Management Status */ |

| #define | PMEN 0x02 /* Power Management Resume Enable */ |

| #define | PWRBTN_EN (1<<8) |

| #define | GBL_EN (1<<5) |

| #define | PMCNTRL 0x04 /* Power Management Control */ |

| #define | SUS_EN (1<<13) /* S0-S5 trigger */ |

| #define | SUS_TYP_MSK (7<<10) |

| #define | SUS_TYP_S0 (5<<10) |

| #define | SUS_TYP_S1 (4<<10) |

| #define | SUS_TYP_S2 (3<<10) /* S2 may also map as 2<<10 */ |

| #define | SUS_TYP_S3 (1<<10) |

| #define | SUS_TYP_S5 (0<<10) |

| #define | SCI_EN (1<<0) |

| #define | PMTMR 0x08 /* Power Management Timer */ |

| #define | GPSTS 0x0c /* General Purpose Status */ |

| #define | GPEN 0x0e /* General Purpose Enable */ |

| #define | THRM_EN (1<<0) |

| #define | PCNTRL 0x10 /* Processor control */ |

| #define | GLBSTS 0x18 /* Global Status */ |

| #define | IRQ_RSM_STS (1<<11) |

| #define | EXTSMI_STS (1<<10) |

| #define | GSTBY_STS (1<<8) |

| #define | GP_STS (1<<7) |

| #define | PM1_STS (1<<6) |

| #define | APM_STS (1<<5) |

| #define | DEV_STS (1<<4) |

| #define | LEGACY_USB_STS (1<<1) |

| #define | BIOS_STS (1<<0) |

| #define | DEVSTS 0x1c /* Device Status */ |

| #define | GLBEN 0x20 /* Global Enable */ |

| #define | EXTSMI_EN (1<<10) /* EXTSMI# signal triggers SMI */ |

| #define | GSTBY_EN (1<<8) |

| #define | BM_TRP_EN (1<<1) |

| #define | BIOS_EN (1<<1) /* GBL_RLS write triggers SMI */ |

| #define | LEGACY_USB_EN (1<<0) /* Keyboard controller access triggers SMI */ |

| #define | GLBCTL 0x28 /* Global Control */ |

| #define | EOS (1<<16) /* End of SMI */ |

| #define | SMI_EN (1<<0) /* SMI enable */ |

| #define | DEVCTL 0x2c /* Device Control */ |

| #define | TRP_EN_DEV12 (1<<24) /* SMI on dev12 trap */ |

| #define | GPO0 0x34 |

| #define | GPO1 0x35 |

| #define | GPO2 0x36 |

| #define | GPO3 0x37 |

| #define | PMBA 0x40 /* Power management base address */ |

| #define | DEFAULT_PMBASE 0xe400 |

| #define | PM_IO_BASE DEFAULT_PMBASE |

| #define | DEVRESA 0x5c /* Device resource A */ |

| #define | DEVRESB 0x60 /* Device resource B */ |

| #define | DEVRESC 0x64 /* Device resource C */ |

| #define | DEVRESD 0x52 /* Device resource D */ |

| #define | DEVRESE 0x68 /* Device resource E */ |

| #define | DEVRESF 0x6c /* Device resource F */ |

| #define | DEVRESG 0x70 /* Device resource G */ |

| #define | DEVRESH 0x74 /* Device resource H */ |

| #define | DEVRESI 0x78 /* Device resource I */ |

| #define | DEVRESJ 0x7c /* Device resource J */ |

| #define | PMREGMISC 0x80 /* Miscellaneous power management */ |

| #define | PMIOSE (1 << 0) /* PM I/O Space Enable */ |

| #define | EXT_BIOS_ENABLE_1MB (1 << 9) /* 1-Meg Extended BIOS Enable */ |

| #define | EXT_BIOS_ENABLE (1 << 7) /* Extended BIOS Enable */ |

| #define | LOWER_BIOS_ENABLE (1 << 6) /* Lower BIOS Enable */ |

| #define | WRITE_PROTECT_ENABLE (1 << 2) /* Write Protect Enable */ |

| #define | SMB_HST_EN (1 << 0) /* Host Interface Enable */ |

| #define | IDE_DECODE_ENABLE (1 << 15) /* IDE Decode Enable */ |

| #define | DTE0 (1 << 3) /* DMA Timing Enable Only, drive 0 */ |

| #define | DTE1 (1 << 7) /* DMA Timing Enable Only, drive 1 */ |

| #define | PSDE0 (1 << 0) /* Primary Drive 0 UDMA/33 */ |

| #define | PSDE1 (1 << 1) /* Primary Drive 1 UDMA/33 */ |

| #define | SSDE0 (1 << 2) /* Secondary Drive 0 UDMA/33 */ |

| #define | SSDE1 (1 << 3) /* Secondary Drive 1 UDMA/33 */ |

| #define | ISA (1 << 0) /* Select ISA */ |

Functions | |

| void | enable_pm (void) |

| void | i82371eb_early_init (void) |

| #define APM_STS (1<<5) |

Definition at line 67 of file i82371eb.h.

Definition at line 76 of file i82371eb.h.

| #define BIOS_STS (1<<0) |

Definition at line 70 of file i82371eb.h.

| #define BM_TRP_EN (1<<1) |

Definition at line 75 of file i82371eb.h.

| #define DEFAULT_PMBASE 0xe400 |

Definition at line 90 of file i82371eb.h.

| #define DEV_STS (1<<4) |

Definition at line 68 of file i82371eb.h.

| #define DEVCTL 0x2c /* Device Control */ |

Definition at line 81 of file i82371eb.h.

| #define DEVRESA 0x5c /* Device resource A */ |

Definition at line 92 of file i82371eb.h.

| #define DEVRESB 0x60 /* Device resource B */ |

Definition at line 93 of file i82371eb.h.

| #define DEVRESC 0x64 /* Device resource C */ |

Definition at line 94 of file i82371eb.h.

| #define DEVRESD 0x52 /* Device resource D */ |

Definition at line 95 of file i82371eb.h.

Definition at line 96 of file i82371eb.h.

| #define DEVRESF 0x6c /* Device resource F */ |

Definition at line 97 of file i82371eb.h.

| #define DEVRESG 0x70 /* Device resource G */ |

Definition at line 98 of file i82371eb.h.

| #define DEVRESH 0x74 /* Device resource H */ |

Definition at line 99 of file i82371eb.h.

| #define DEVRESI 0x78 /* Device resource I */ |

Definition at line 100 of file i82371eb.h.

| #define DEVRESJ 0x7c /* Device resource J */ |

Definition at line 101 of file i82371eb.h.

| #define DEVSTS 0x1c /* Device Status */ |

Definition at line 71 of file i82371eb.h.

| #define DTE0 (1 << 3) /* DMA Timing Enable Only, drive 0 */ |

Definition at line 112 of file i82371eb.h.

| #define DTE1 (1 << 7) /* DMA Timing Enable Only, drive 1 */ |

Definition at line 113 of file i82371eb.h.

| #define EOS (1<<16) /* End of SMI */ |

Definition at line 79 of file i82371eb.h.

| #define EXT_BIOS_ENABLE (1 << 7) /* Extended BIOS Enable */ |

Definition at line 107 of file i82371eb.h.

| #define EXT_BIOS_ENABLE_1MB (1 << 9) /* 1-Meg Extended BIOS Enable */ |

Definition at line 106 of file i82371eb.h.

| #define EXTSMI_EN (1<<10) /* EXTSMI# signal triggers SMI */ |

Definition at line 73 of file i82371eb.h.

| #define EXTSMI_STS (1<<10) |

Definition at line 63 of file i82371eb.h.

| #define GBL_EN (1<<5) |

Definition at line 46 of file i82371eb.h.

| #define GENCFG 0xb0 /* General configuration register */ |

Definition at line 24 of file i82371eb.h.

| #define GLBCTL 0x28 /* Global Control */ |

Definition at line 78 of file i82371eb.h.

| #define GLBEN 0x20 /* Global Enable */ |

Definition at line 72 of file i82371eb.h.

| #define GLBSTS 0x18 /* Global Status */ |

Definition at line 61 of file i82371eb.h.

| #define GP_STS (1<<7) |

Definition at line 65 of file i82371eb.h.

| #define GPEN 0x0e /* General Purpose Enable */ |

Definition at line 58 of file i82371eb.h.

| #define GPO0 0x34 |

Definition at line 83 of file i82371eb.h.

| #define GPO1 0x35 |

Definition at line 84 of file i82371eb.h.

| #define GPO2 0x36 |

Definition at line 85 of file i82371eb.h.

| #define GPO2223 (1<<28) /* GPO22/23 */ |

Definition at line 25 of file i82371eb.h.

| #define GPO3 0x37 |

Definition at line 86 of file i82371eb.h.

| #define GPSTS 0x0c /* General Purpose Status */ |

Definition at line 57 of file i82371eb.h.

| #define GSTBY_EN (1<<8) |

Definition at line 74 of file i82371eb.h.

| #define GSTBY_STS (1<<8) |

Definition at line 64 of file i82371eb.h.

| #define IDE_DECODE_ENABLE (1 << 15) /* IDE Decode Enable */ |

Definition at line 111 of file i82371eb.h.

| #define IDETIM_PRI 0x40 /* IDE timing register, primary channel */ |

Definition at line 32 of file i82371eb.h.

| #define IDETIM_SEC 0x42 /* IDE timing register, secondary channel */ |

Definition at line 33 of file i82371eb.h.

| #define IRQ_RSM_STS (1<<11) |

Definition at line 62 of file i82371eb.h.

| #define ISA (1 << 0) /* Select ISA */ |

Definition at line 118 of file i82371eb.h.

| #define LEGACY_USB_EN (1<<0) /* Keyboard controller access triggers SMI */ |

Definition at line 77 of file i82371eb.h.

| #define LEGACY_USB_STS (1<<1) |

Definition at line 69 of file i82371eb.h.

| #define LOWER_BIOS_ENABLE (1 << 6) /* Lower BIOS Enable */ |

Definition at line 108 of file i82371eb.h.

| #define ONOFF | ( | cond, | |

| reg, | |||

| bits | |||

| ) | ((cond) ? ((reg) | (bits)) : ((reg) & ~(bits))) |

Definition at line 21 of file i82371eb.h.

| #define PCNTRL 0x10 /* Processor control */ |

Definition at line 60 of file i82371eb.h.

| #define PM1_STS (1<<6) |

Definition at line 66 of file i82371eb.h.

| #define PM_IO_BASE DEFAULT_PMBASE |

Definition at line 91 of file i82371eb.h.

Definition at line 89 of file i82371eb.h.

| #define PMCNTRL 0x04 /* Power Management Control */ |

Definition at line 47 of file i82371eb.h.

| #define PMEN 0x02 /* Power Management Resume Enable */ |

Definition at line 44 of file i82371eb.h.

| #define PMIOSE (1 << 0) /* PM I/O Space Enable */ |

Definition at line 103 of file i82371eb.h.

| #define PMREGMISC 0x80 /* Miscellaneous power management */ |

Definition at line 102 of file i82371eb.h.

| #define PMSTS 0x00 /* Power Management Status */ |

Definition at line 43 of file i82371eb.h.

| #define PMTMR 0x08 /* Power Management Timer */ |

Definition at line 56 of file i82371eb.h.

| #define PSDE0 (1 << 0) /* Primary Drive 0 UDMA/33 */ |

Definition at line 114 of file i82371eb.h.

| #define PSDE1 (1 << 1) /* Primary Drive 1 UDMA/33 */ |

Definition at line 115 of file i82371eb.h.

| #define PWRBTN_EN (1<<8) |

Definition at line 45 of file i82371eb.h.

| #define RTC_ENABLE (1<<0) |

Definition at line 29 of file i82371eb.h.

| #define RTC_POS_DECODE (1<<5) |

Definition at line 27 of file i82371eb.h.

| #define RTCCFG 0xcb /* Real time clock configuration register */ |

Definition at line 26 of file i82371eb.h.

| #define SCI_EN (1<<0) |

Definition at line 55 of file i82371eb.h.

| #define SMB_HST_EN (1 << 0) /* Host Interface Enable */ |

Definition at line 110 of file i82371eb.h.

Definition at line 38 of file i82371eb.h.

| #define SMBHSTCFG 0xd2 /* SMBus host configuration */ |

Definition at line 40 of file i82371eb.h.

| #define SMBUS_IO_BASE 0x0f00 |

Definition at line 39 of file i82371eb.h.

| #define SMI_EN (1<<0) /* SMI enable */ |

Definition at line 80 of file i82371eb.h.

| #define SSDE0 (1 << 2) /* Secondary Drive 0 UDMA/33 */ |

Definition at line 116 of file i82371eb.h.

| #define SSDE1 (1 << 3) /* Secondary Drive 1 UDMA/33 */ |

Definition at line 117 of file i82371eb.h.

Definition at line 48 of file i82371eb.h.

| #define SUS_TYP_MSK (7<<10) |

Definition at line 49 of file i82371eb.h.

| #define SUS_TYP_S0 (5<<10) |

Definition at line 50 of file i82371eb.h.

| #define SUS_TYP_S1 (4<<10) |

Definition at line 51 of file i82371eb.h.

| #define SUS_TYP_S2 (3<<10) /* S2 may also map as 2<<10 */ |

Definition at line 52 of file i82371eb.h.

| #define SUS_TYP_S3 (1<<10) |

Definition at line 53 of file i82371eb.h.

| #define SUS_TYP_S5 (0<<10) |

Definition at line 54 of file i82371eb.h.

| #define THRM_EN (1<<0) |

Definition at line 59 of file i82371eb.h.

| #define TRP_EN_DEV12 (1<<24) /* SMI on dev12 trap */ |

Definition at line 82 of file i82371eb.h.

| #define UDMACTL 0x48 /* Ultra DMA/33 control register */ |

Definition at line 34 of file i82371eb.h.

| #define UDMATIM 0x4a /* Ultra DMA/33 timing register */ |

Definition at line 35 of file i82371eb.h.

| #define UPPER_RAM_EN (1<<2) |

Definition at line 28 of file i82371eb.h.

| #define WRITE_PROTECT_ENABLE (1 << 2) /* Write Protect Enable */ |

Definition at line 109 of file i82371eb.h.

| #define XBCS 0x4e /* X-Bus chip select register */ |

Definition at line 23 of file i82371eb.h.

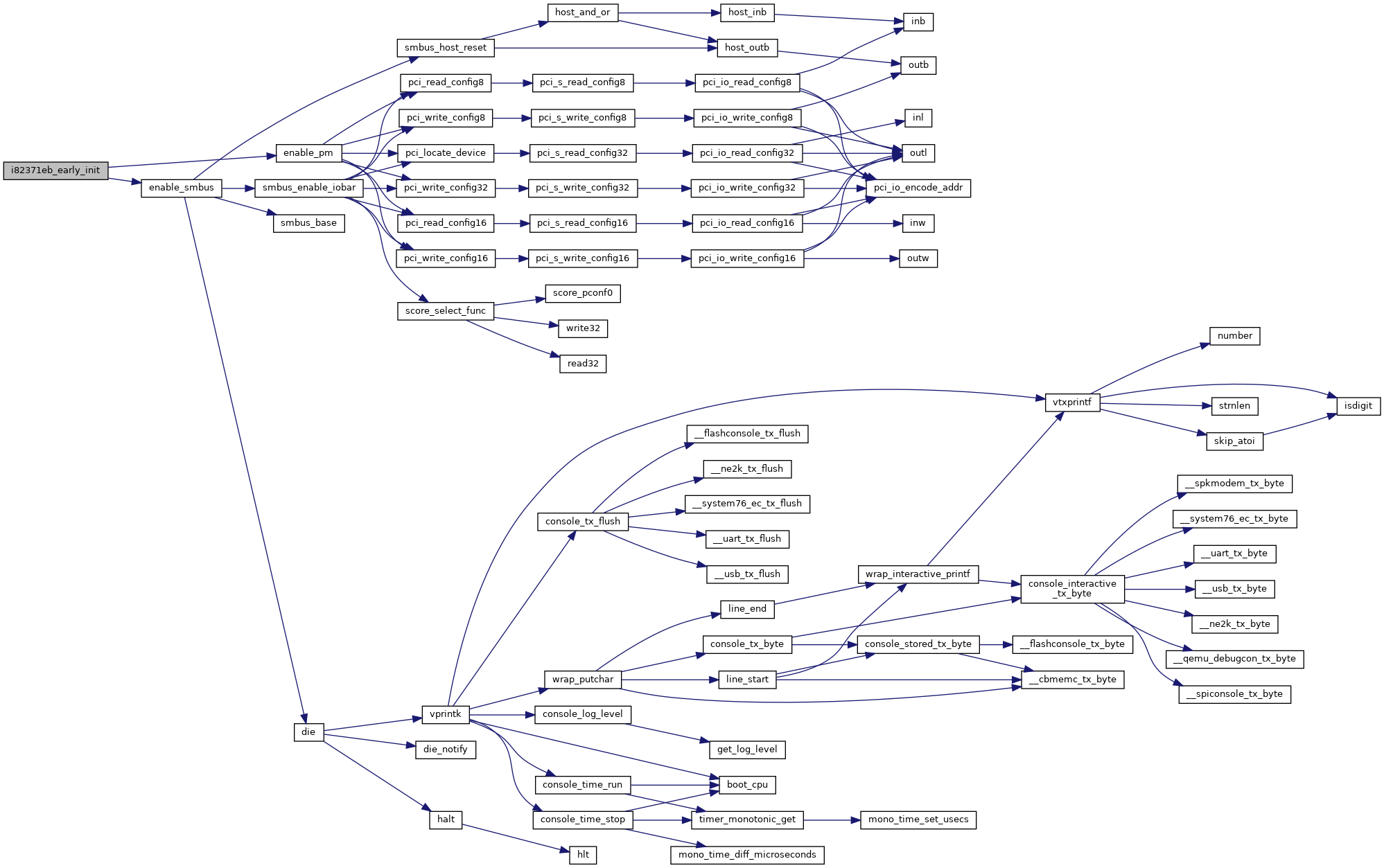

Definition at line 10 of file early_pm.c.

References DEFAULT_PMBASE, PCI_COMMAND, PCI_COMMAND_IO, PCI_DID_INTEL_82371AB_SMB_ACPI, PCI_ID, pci_locate_device(), pci_read_config16(), pci_read_config8(), PCI_VID_INTEL, pci_write_config16(), pci_write_config32(), pci_write_config8(), PMBA, PMIOSE, and PMREGMISC.

Referenced by i82371eb_early_init().

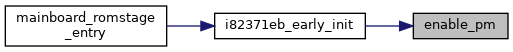

Definition at line 11 of file early_smbus.c.

References enable_pm(), and enable_smbus().

Referenced by mainboard_romstage_entry().