|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

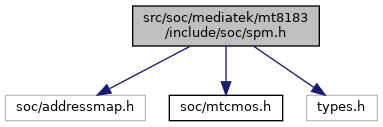

Go to the source code of this file.

Data Structures | |

| struct | mtk_spm_regs |

| struct | pcm_desc |

| struct | dyna_load_pcm |

Macros | |

| #define | SPM_PROJECT_CODE 0xb16 |

| #define | SPM_REGWR_CFG_KEY (SPM_PROJECT_CODE << 16) |

| #define | BCLK_CG_EN_LSB (1U << 0) /* 1b */ |

| #define | MD_BCLK_CG_EN_LSB (1U << 1) /* 1b */ |

| #define | PCM_IM_HOST_W_EN_LSB (1U << 30) /* 1b */ |

| #define | PCM_IM_HOST_EN_LSB (1U << 31) /* 1b */ |

| #define | SYSCLK0_EN_CTRL_LSB (1U << 0) /* 2b */ |

| #define | SYSCLK1_EN_CTRL_LSB (1U << 2) /* 2b */ |

| #define | SPM_LOCK_INFRA_DCM_LSB (1U << 5) /* 1b */ |

| #define | EXT_SRCCLKEN_MASK (1U << 6) /* 1b */ |

| #define | CXO32K_REMOVE_EN_MD1_LSB (1U << 9) /* 1b */ |

| #define | CLKSQ1_SEL_CTRL_LSB (1U << 12) /* 1b */ |

| #define | SRCLKEN0_EN_LSB (1U << 13) /* 1b */ |

| #define | PCM_KICK_L_LSB (1U << 0) /* 1b */ |

| #define | IM_KICK_L_LSB (1U << 1) /* 1b */ |

| #define | PCM_CK_EN_LSB (1U << 2) /* 1b */ |

| #define | EN_IM_SLEEP_DVS_LSB (1U << 3) /* 1b */ |

| #define | IM_AUTO_PDN_EN_LSB (1U << 4) /* 1b */ |

| #define | PCM_SW_RESET_LSB (1U << 15) /* 1b */ |

| #define | IM_SLAVE_LSB (1U << 0) /* 1b */ |

| #define | IM_SLEEP_LSB (1U << 1) /* 1b */ |

| #define | MIF_APBEN_LSB (1U << 3) /* 1b */ |

| #define | IM_PDN_LSB (1U << 4) /* 1b */ |

| #define | PCM_TIMER_EN_LSB (1U << 5) /* 1b */ |

| #define | IM_NONRP_EN_LSB (1U << 6) /* 1b */ |

| #define | DIS_MIF_PROT_LSB (1U << 7) /* 1b */ |

| #define | PCM_WDT_EN_LSB (1U << 8) /* 1b */ |

| #define | PCM_WDT_WAKE_MODE_LSB (1U << 9) /* 1b */ |

| #define | SPM_SRAM_SLEEP_B_LSB (1U << 10) /* 1b */ |

| #define | SPM_SRAM_ISOINT_B_LSB (1U << 11) /* 1b */ |

| #define | EVENT_LOCK_EN_LSB (1U << 12) /* 1b */ |

| #define | SRCCLKEN_FAST_RESP_LSB (1U << 13) /* 1b */ |

| #define | SCP_APB_INTERNAL_EN_LSB (1U << 14) /* 1b */ |

| #define | PCM_IRQ_ROOT_MASK_LSB (1U << 3) /* 1b */ |

| #define | WAKEUP_EVENT_MASK_B_BIT0 (1U << 0) /* 1b */ |

| #define | SPARE1_DDREN_MASK_B_LSB (1U << 0) /* 1b */ |

| #define | SPM_PC_TRACE_OFFSET_LSB (1U << 0) /* 12b */ |

| #define | SPM_PC_TRACE_OFFSET (1U << 3) /* 1b */ |

| #define | SPM_PC_TRACE_HW_EN_LSB (1U << 16) /* 1b */ |

| #define | SPARE_ACK_MASK_B_BIT0 (1U << 0) /* 1b */ |

| #define | SPARE_ACK_MASK_B_BIT1 (1U << 1) /* 1b */ |

| #define | CONN_DDR_EN_DBC_LEN (0x00000154 << 20) |

| #define | IFR_SRAMROM_ROM_PDN (0x0000003f) |

| #define | IM_STATE (0x4 << 7) |

| #define | IM_STATE_MASK (0x7 << 7) |

| #define | MD_DDR_EN_0_DBC_LEN (0x00000154) |

| #define | MD_DDR_EN_1_DBC_LEN (0x00000154 << 10) |

| #define | PCM_FSM_STA_DEF (0x00108490) |

| #define | PCM_FSM_STA_MASK (0x7FFFFF) |

| #define | POWER_ON_VAL1_DEF (0x00015800) |

| #define | SPM_CORE_TIMEOUT (5000) |

| #define | SPM_MAS_PAUSE_MASK_B_VAL (0xFFFFFFFF) |

| #define | SPM_MAS_PAUSE2_MASK_B_VAL (0xFFFFFFFF) |

| #define | SPM_PCM_REG1_DATA_CHECK (0x1) |

| #define | SPM_PCM_REG15_DATA_CHECK (0x0) |

| #define | SPM_WAKEUP_EVENT_MASK_DEF (0xF0F92218) |

| #define | SYSCLK1_EN_CTRL (0x3 << 2) |

| #define | SYSCLK1_SRC_MASK_B (0x10 << 23) |

| #define | ISRM_TWAM (1U << 2) |

| #define | ISRM_PCM_RETURN (1U << 3) |

| #define | ISRM_RET_IRQ_AUX (0x3FF00) |

| #define | ISRM_ALL_EXC_TWAM (ISRM_RET_IRQ_AUX) |

| #define | ISRM_ALL (ISRM_ALL_EXC_TWAM | ISRM_TWAM) |

| #define | ISRS_TWAM (1U << 2) |

| #define | ISRS_PCM_RETURN (1U << 3) |

| #define | ISRS_SW_INT0 (1U << 4) |

| #define | ISRC_TWAM (ISRS_TWAM) |

| #define | ISRC_ALL_EXC_TWAM (ISRS_PCM_RETURN) |

| #define | ISRC_ALL (ISRC_ALL_EXC_TWAM | ISRC_TWAM) |

| #define | PCM_PWRIO_EN_R0 (1U << 0) |

| #define | PCM_PWRIO_EN_R7 (1U << 7) |

| #define | PCM_RF_SYNC_R0 (1U << 16) |

| #define | PCM_RF_SYNC_R6 (1U << 22) |

| #define | PCM_RF_SYNC_R7 (1U << 23) |

| #define | PCM_SW_INT_ALL (0x3FF) |

| #define | PCM_EVENT_VECTOR_NUM 16 |

Enumerations | |

| enum | { DISP_PWR_STA_MASK = 0x1 << 3 , DISP_SRAM_PDN_MASK = 0x1 << 8 , DISP_SRAM_ACK_MASK = 0x1 << 12 , AUDIO_PWR_STA_MASK = 0x1 << 24 , AUDIO_SRAM_PDN_MASK = 0xf << 8 , AUDIO_SRAM_ACK_MASK = 0xf << 12 } |

| enum | dyna_load_pcm_index { DYNA_LOAD_PCM_SUSPEND_LP4_3733 = 0 , DYNA_LOAD_PCM_SUSPEND_LP4_3200 , DYNA_LOAD_PCM_MAX } |

Functions | |

| check_member (mtk_spm_regs, spm_ack_chk_latch4, 0x0974) | |

| int | spm_init (void) |

Variables | |

| static struct mtk_spm_regs *const | mtk_spm = (void *)SPM_BASE |

| static const struct power_domain_data | disp [] |

| static const struct power_domain_data | audio [] |

| #define ISRC_ALL (ISRC_ALL_EXC_TWAM | ISRC_TWAM) |

| #define ISRC_ALL_EXC_TWAM (ISRS_PCM_RETURN) |

| #define ISRM_ALL (ISRM_ALL_EXC_TWAM | ISRM_TWAM) |

| #define ISRM_ALL_EXC_TWAM (ISRM_RET_IRQ_AUX) |

| #define SPM_REGWR_CFG_KEY (SPM_PROJECT_CODE << 16) |

| anonymous enum |

| enum dyna_load_pcm_index |

| check_member | ( | mtk_spm_regs | , |

| spm_ack_chk_latch4 | , | ||

| 0x0974 | |||

| ) |

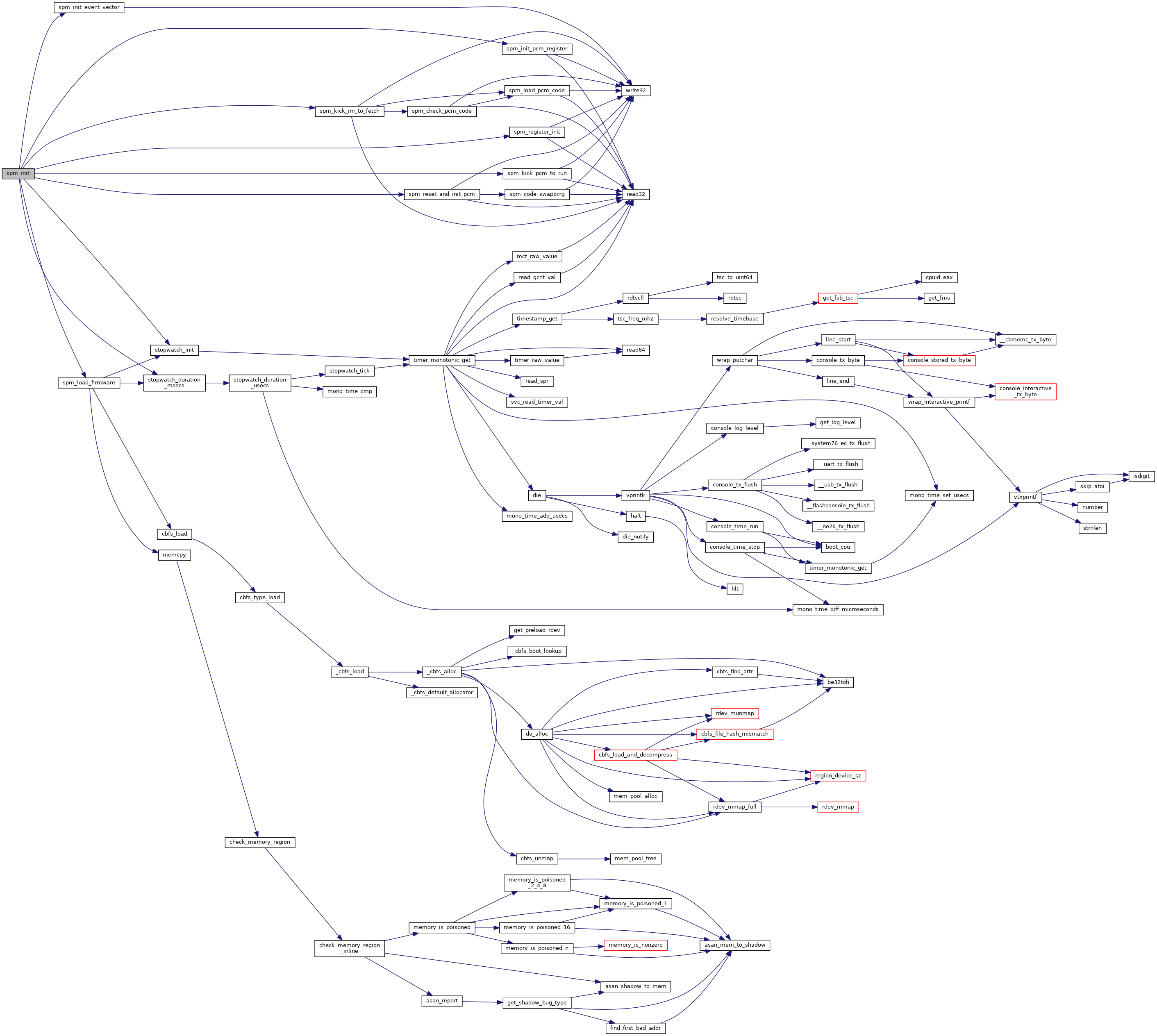

| int spm_init | ( | void | ) |

Definition at line 298 of file spm.c.

References BIOS_DEBUG, BIOS_ERR, BIOS_INFO, CONFIG, dyna_load_pcm::desc, DYNA_LOAD_PCM_SUSPEND_LP4_3200, DYNA_LOAD_PCM_SUSPEND_LP4_3733, printk, spm_init_event_vector(), spm_init_pcm_register(), spm_kick_im_to_fetch(), spm_kick_pcm_to_run(), spm_load_firmware(), spm_register_init(), spm_reset_and_init_pcm(), stopwatch_duration_msecs(), and stopwatch_init().

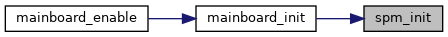

Referenced by mainboard_init().

|

static |

|

static |

|

static |