|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

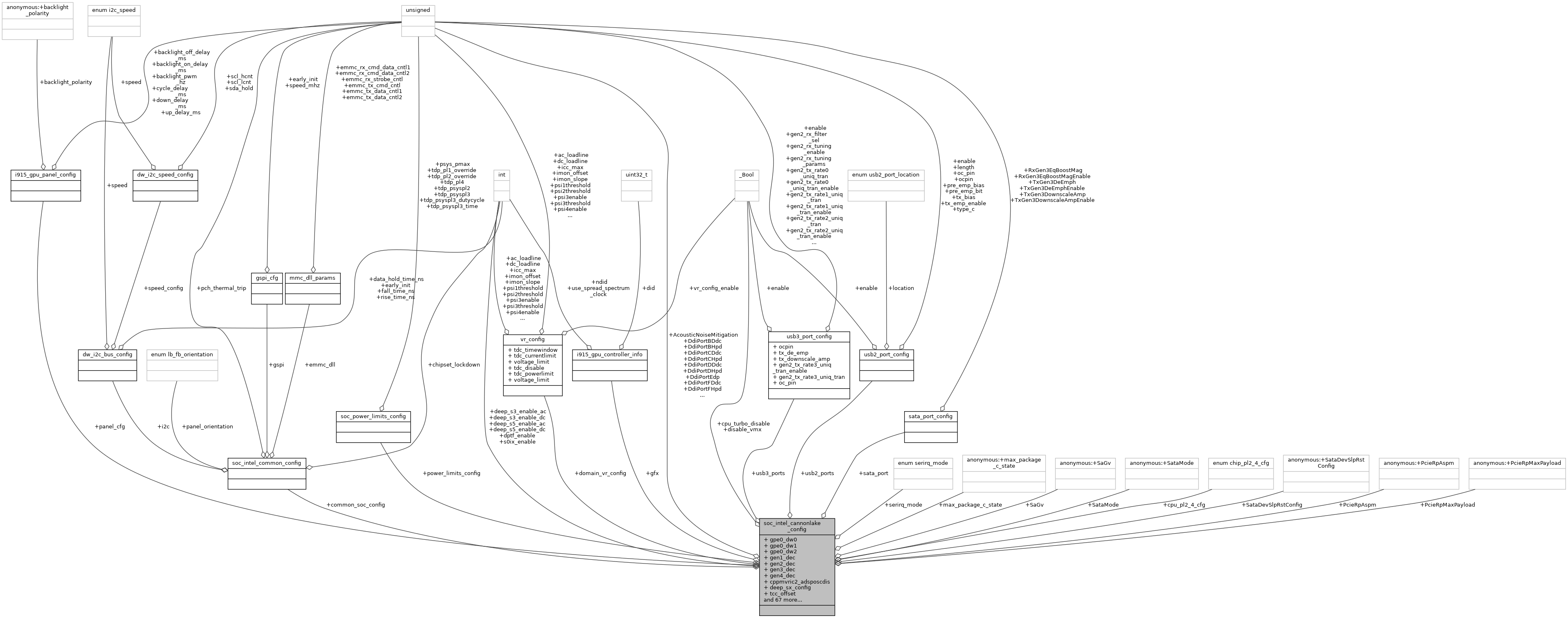

#include <chip.h>

Public Types | |

| enum | { MAX_PC_DEFAULT = 0 , MAX_PC0_1 = 1 , MAX_PC2 = 2 , MAX_PC3 = 3 , MAX_PC6 = 4 , MAX_PC7 = 5 , MAX_PC7S = 6 , MAX_PC8 = 7 , MAX_PC9 = 8 , MAX_PC10 = 9 } |

| enum | { SaGv_Disabled , SaGv_FixedLow , SaGv_FixedHigh , SaGv_Enabled } |

| enum | { SATA_AHCI , SATA_RAID } |

| enum | { SataDevSlpResumeReset = 1 , SataDevSlpHostDeepReset = 3 , SataDevSlpPlatformReset = 5 , SataDevSlpDswReset = 7 } |

| enum | { AspmDefault , AspmDisabled , AspmL0s , AspmL1 , AspmL0sL1 , AspmAutoConfig } |

| enum | { RpMaxPayload_128 , RpMaxPayload_256 } |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| struct soc_intel_common_config soc_intel_cannonlake_config::common_soc_config |

| enum chip_pl2_4_cfg soc_intel_cannonlake_config::cpu_pl2_4_cfg |

| struct vr_config soc_intel_cannonlake_config::domain_vr_config[NUM_VR_DOMAINS] |

| struct i915_gpu_controller_info soc_intel_cannonlake_config::gfx |

| uint8_t soc_intel_cannonlake_config::gpio_pm[TOTAL_GPIO_COMM] |

| enum { ... } soc_intel_cannonlake_config::max_package_c_state |

| struct i915_gpu_panel_config soc_intel_cannonlake_config::panel_cfg |

Definition at line 443 of file chip.h.

Referenced by graphics_soc_panel_init().

| uint8_t soc_intel_cannonlake_config::PchHdaIDispCodecDisconnect |

| uint8_t soc_intel_cannonlake_config::PchPmSlpS0VmRuntimeControl |

| uint8_t soc_intel_cannonlake_config::PcieClkSrcClkReq[CONFIG_MAX_PCIE_CLOCK_SRC] |

| uint8_t soc_intel_cannonlake_config::PcieClkSrcUsage[CONFIG_MAX_PCIE_CLOCK_SRC] |

| uint8_t soc_intel_cannonlake_config::PcieRpAdvancedErrorReporting[CONFIG_MAX_ROOT_PORTS] |

| enum { ... } soc_intel_cannonlake_config::PcieRpAspm[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_cannonlake_config::PcieRpEnable[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_cannonlake_config::PcieRpHotPlug[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_cannonlake_config::PcieRpLtrEnable[CONFIG_MAX_ROOT_PORTS] |

| enum { ... } soc_intel_cannonlake_config::PcieRpMaxPayload[CONFIG_MAX_ROOT_PORTS] |

| uint8_t soc_intel_cannonlake_config::PcieRpSlotImplemented[CONFIG_MAX_ROOT_PORTS] |

| struct soc_power_limits_config soc_intel_cannonlake_config::power_limits_config |

| enum { ... } soc_intel_cannonlake_config::SaGv |

| struct sata_port_config soc_intel_cannonlake_config::sata_port[SOC_INTEL_CML_SATA_DEV_MAX] |

| enum { ... } soc_intel_cannonlake_config::SataDevSlpRstConfig |

| enum { ... } soc_intel_cannonlake_config::SataMode |

| uint8_t soc_intel_cannonlake_config::SataPortsDevSlpResetConfig[8] |

| uint8_t soc_intel_cannonlake_config::SerialIoDevMode[PchSerialIoIndexMAX] |

| enum serirq_mode soc_intel_cannonlake_config::serirq_mode |

| struct usb2_port_config soc_intel_cannonlake_config::usb2_ports[16] |

| uint16_t soc_intel_cannonlake_config::usb2_wake_enable_bitmap |

| struct usb3_port_config soc_intel_cannonlake_config::usb3_ports[10] |

| uint16_t soc_intel_cannonlake_config::usb3_wake_enable_bitmap |