|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

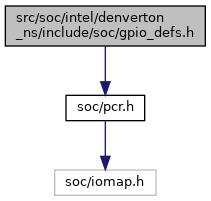

#include <soc/pcr.h>

Go to the source code of this file.

| #define B_PCH_GPIO_PAD_MODE ((1 << 12) | (1 << 11) | (1 << 10)) |

Definition at line 188 of file gpio_defs.h.

| #define B_PCH_GPIO_PADTOL (1 << 25) |

Definition at line 228 of file gpio_defs.h.

| #define B_PCH_GPIO_PRE_GFRX_SEL (1 << 24) |

Definition at line 144 of file gpio_defs.h.

| #define B_PCH_GPIO_RST_CONF ((1 << 31) | (1 << 30)) |

Definition at line 116 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_APIC_ROUTE (1 << 20) |

Definition at line 164 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_LVL_EDG ((1 << 26) | (1 << 25)) |

Definition at line 136 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_NMI_ROUTE (1 << 17) |

Definition at line 182 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_PAD_STATE (1 << 29) |

Definition at line 124 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_RAW1 (1 << 28) |

Definition at line 130 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_SCI_ROUTE (1 << 19) |

Definition at line 170 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_SMI_ROUTE (1 << 18) |

Definition at line 176 of file gpio_defs.h.

| #define B_PCH_GPIO_RX_STATE (1 << 1) |

Definition at line 212 of file gpio_defs.h.

| #define B_PCH_GPIO_RXDIS (1 << 9) |

Definition at line 200 of file gpio_defs.h.

| #define B_PCH_GPIO_RXINV (1 << 23) |

Definition at line 150 of file gpio_defs.h.

| #define B_PCH_GPIO_RXTXENCFG ((1 << 22) | (1 << 21)) |

Definition at line 156 of file gpio_defs.h.

| #define B_PCH_GPIO_TERM ((1 << 13) | (1 << 12) | (1 << 11) | (1 << 10)) |

Definition at line 235 of file gpio_defs.h.

| #define B_PCH_GPIO_TX_STATE (1 << 0) |

Definition at line 218 of file gpio_defs.h.

| #define B_PCH_GPIO_TXDIS (1 << 8) |

Definition at line 206 of file gpio_defs.h.

| #define GPIO_DNV_GROUP_MAX GPIO_DNV_GROUP_SC1 |

Definition at line 308 of file gpio_defs.h.

| #define GPIO_DNV_GROUP_MIN GPIO_DNV_GROUP_NC |

Definition at line 307 of file gpio_defs.h.

| #define GPIO_DNV_GROUP_NC 0x0100 |

Denverton GPIO Groups.

Definition at line 303 of file gpio_defs.h.

| #define GPIO_DNV_GROUP_SC0 0x0102 |

Definition at line 305 of file gpio_defs.h.

| #define GPIO_DNV_GROUP_SC1 0x0103 |

Definition at line 306 of file gpio_defs.h.

| #define GPIO_DNV_GROUP_SC_DFX 0x0101 |

Definition at line 304 of file gpio_defs.h.

| #define GPIO_GET_CHIPSET_ID | ( | Pad | ) | (Pad >> 24) |

Definition at line 483 of file gpio_defs.h.

| #define GPIO_GET_GROUP_FROM_PAD | ( | Pad | ) | (Pad >> 16) |

Definition at line 480 of file gpio_defs.h.

| #define GPIO_GET_GROUP_INDEX | ( | Group | ) | (Group & 0xFF) |

Definition at line 479 of file gpio_defs.h.

| #define GPIO_GET_GROUP_INDEX_FROM_PAD | ( | Pad | ) | GPIO_GET_GROUP_INDEX((Pad >> 16)) |

Definition at line 481 of file gpio_defs.h.

| #define GPIO_GET_PAD_NUMBER | ( | Pad | ) | (Pad & 0xFFFF) |

Definition at line 482 of file gpio_defs.h.

| #define GPIO_PAD_DEF | ( | Group, | |

| Pad | |||

| ) | (uint32_t)((Group << 16) + Pad) |

Definition at line 478 of file gpio_defs.h.

| #define GPIO_PCIE_CLKREQ5_N 98 |

Definition at line 263 of file gpio_defs.h.

| #define GPIO_PCIE_CLKREQ6_N 99 |

Definition at line 267 of file gpio_defs.h.

| #define GPIO_PCIE_CLKREQ7_N 100 |

Definition at line 271 of file gpio_defs.h.

| #define GPIO_SATA0_SDOUT 94 |

Definition at line 295 of file gpio_defs.h.

| #define GPIO_SATA1_SDOUT 95 |

Definition at line 291 of file gpio_defs.h.

| #define GPIO_SMB3_CLTT_CLK 13 |

Definition at line 259 of file gpio_defs.h.

| #define GPIO_SMB3_CLTT_DATA 12 |

Definition at line 255 of file gpio_defs.h.

| #define GPIO_UART0_RXD 101 |

Definition at line 275 of file gpio_defs.h.

| #define GPIO_UART0_TXD 102 |

Definition at line 279 of file gpio_defs.h.

| #define GPIO_UART1_RXD 96 |

Definition at line 283 of file gpio_defs.h.

| #define GPIO_UART1_TXD 97 |

Definition at line 287 of file gpio_defs.h.

| #define GROUP_INDEX_MASK 0x00FF0000 |

Definition at line 474 of file gpio_defs.h.

| #define GROUP_INFO_MASK 0xFFFF0000 |

Definition at line 473 of file gpio_defs.h.

| #define GROUP_INFO_POSITION 16 |

Definition at line 472 of file gpio_defs.h.

| #define N_PCH_GPIO_PAD_MODE 10 |

Definition at line 189 of file gpio_defs.h.

| #define N_PCH_GPIO_PADTOL 25 |

Definition at line 229 of file gpio_defs.h.

| #define N_PCH_GPIO_PRE_GFRX_SEL 24 |

Definition at line 145 of file gpio_defs.h.

| #define N_PCH_GPIO_RST_CONF 30 |

Definition at line 117 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_APIC_ROUTE 20 |

Definition at line 165 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_LVL_EDG 25 |

Definition at line 137 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_NMI_ROUTE 17 |

Definition at line 183 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_PAD_STATE 29 |

Definition at line 125 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_RAW1 28 |

Definition at line 131 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_SCI_ROUTE 19 |

Definition at line 171 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_SMI_ROUTE 18 |

Definition at line 177 of file gpio_defs.h.

| #define N_PCH_GPIO_RX_STATE 1 |

Definition at line 213 of file gpio_defs.h.

| #define N_PCH_GPIO_RXDIS 9 |

Definition at line 201 of file gpio_defs.h.

| #define N_PCH_GPIO_RXINV 23 |

Definition at line 151 of file gpio_defs.h.

| #define N_PCH_GPIO_RXTXENCFG 21 |

Definition at line 157 of file gpio_defs.h.

| #define N_PCH_GPIO_TERM 10 |

Definition at line 236 of file gpio_defs.h.

| #define N_PCH_GPIO_TX_STATE 0 |

Definition at line 219 of file gpio_defs.h.

| #define N_PCH_GPIO_TXDIS 8 |

Definition at line 207 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_I2C_CLK 0x0100000A |

Definition at line 319 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_I2C_DATA 0x0100000B |

Definition at line 320 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_LED0 0x01000017 |

Definition at line 332 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_LED1 0x01000018 |

Definition at line 333 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_SDP0 0x01000000 |

Definition at line 309 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_SDP1 0x01000002 |

Definition at line 311 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_SDP2 0x01000004 |

Definition at line 313 of file gpio_defs.h.

| #define NORTH_ALL_GBE0_SDP3 0x01000006 |

Definition at line 315 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_I2C_CLK 0x0100000C |

Definition at line 321 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_I2C_DATA 0x0100000D |

Definition at line 322 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_LED0 0x01000019 |

Definition at line 334 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_LED1 0x0100001A |

Definition at line 335 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_SDP0 0x01000001 |

Definition at line 310 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_SDP1 0x01000003 |

Definition at line 312 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_SDP2 0x01000005 |

Definition at line 314 of file gpio_defs.h.

| #define NORTH_ALL_GBE1_SDP3 0x01000007 |

Definition at line 316 of file gpio_defs.h.

| #define NORTH_ALL_GBE2_LED0 0x01000008 |

Definition at line 317 of file gpio_defs.h.

| #define NORTH_ALL_GBE2_LED1 0x01000009 |

Definition at line 318 of file gpio_defs.h.

| #define NORTH_ALL_GPIO_0 0x0100001B |

Definition at line 336 of file gpio_defs.h.

| #define NORTH_ALL_GPIO_1 0x01000021 |

Definition at line 342 of file gpio_defs.h.

| #define NORTH_ALL_GPIO_2 0x01000022 |

Definition at line 343 of file gpio_defs.h.

| #define NORTH_ALL_MEMHOT_N 0x01000028 |

Definition at line 349 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_ARB_IN 0x01000012 |

Definition at line 327 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_ARB_OUT 0x01000016 |

Definition at line 331 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_CLK_IN 0x0100000F |

Definition at line 324 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_CRS_DV 0x01000011 |

Definition at line 326 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_RXD0 0x0100000E |

Definition at line 323 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_RXD1 0x01000010 |

Definition at line 325 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_TX_EN 0x01000013 |

Definition at line 328 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_TXD0 0x01000014 |

Definition at line 329 of file gpio_defs.h.

| #define NORTH_ALL_NCSI_TXD1 0x01000015 |

Definition at line 330 of file gpio_defs.h.

| #define NORTH_ALL_PCIE_CLKREQ0_N 0x0100001C |

Definition at line 337 of file gpio_defs.h.

| #define NORTH_ALL_PCIE_CLKREQ1_N 0x0100001D |

Definition at line 338 of file gpio_defs.h.

| #define NORTH_ALL_PCIE_CLKREQ2_N 0x0100001E |

Definition at line 339 of file gpio_defs.h.

| #define NORTH_ALL_PCIE_CLKREQ3_N 0x0100001F |

Definition at line 340 of file gpio_defs.h.

| #define NORTH_ALL_PCIE_CLKREQ4_N 0x01000020 |

Definition at line 341 of file gpio_defs.h.

| #define NORTH_ALL_PROCHOT_N 0x01000027 |

Definition at line 348 of file gpio_defs.h.

| #define NORTH_ALL_SVID_ALERT_N 0x01000023 |

Definition at line 344 of file gpio_defs.h.

| #define NORTH_ALL_SVID_CLK 0x01000025 |

Definition at line 346 of file gpio_defs.h.

| #define NORTH_ALL_SVID_DATA 0x01000024 |

Definition at line 345 of file gpio_defs.h.

| #define NORTH_ALL_THERMTRIP_N 0x01000026 |

Definition at line 347 of file gpio_defs.h.

| #define PAD_INFO_MASK 0x0000FFFF |

Definition at line 471 of file gpio_defs.h.

| #define PID_NorthCommunity PID_GPIOCOM0 |

Definition at line 248 of file gpio_defs.h.

| #define PID_PCIE_CLKREQ5_N PID_SouthCommunity |

Definition at line 265 of file gpio_defs.h.

| #define PID_PCIE_CLKREQ6_N PID_SouthCommunity |

Definition at line 269 of file gpio_defs.h.

| #define PID_PCIE_CLKREQ7_N PID_SouthCommunity |

Definition at line 273 of file gpio_defs.h.

| #define PID_SATA0_SDOUT PID_SouthCommunity |

Definition at line 297 of file gpio_defs.h.

| #define PID_SATA1_SDOUT PID_SouthCommunity |

Definition at line 293 of file gpio_defs.h.

| #define PID_SMB3_CLTT_CLK PID_SouthCommunity |

Definition at line 261 of file gpio_defs.h.

| #define PID_SMB3_CLTT_DATA PID_SouthCommunity |

Definition at line 257 of file gpio_defs.h.

| #define PID_SouthCommunity PID_GPIOCOM1 |

Definition at line 249 of file gpio_defs.h.

| #define PID_UART0_RXD PID_SouthCommunity |

Definition at line 277 of file gpio_defs.h.

| #define PID_UART0_TXD PID_SouthCommunity |

Definition at line 281 of file gpio_defs.h.

| #define PID_UART1_RXD PID_SouthCommunity |

Definition at line 285 of file gpio_defs.h.

| #define PID_UART1_TXD PID_SouthCommunity |

Definition at line 289 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_PCIE_CLKREQ5_N 0x4A0 |

Definition at line 264 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_PCIE_CLKREQ6_N 0x4a8 |

Definition at line 268 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_PCIE_CLKREQ7_N 0x4b0 |

Definition at line 272 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_SATA0_SDOUT 0x5a8 |

Definition at line 296 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_SATA1_SDOUT 0x5b0 |

Definition at line 292 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_SMB3_CLTT_CLK 0x498 |

Definition at line 260 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_SMB3_CLTT_DATA 0x490 |

Definition at line 256 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_UART0_RXD 0x4b8 |

Definition at line 276 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_UART0_TXD 0x4c0 |

Definition at line 280 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_UART1_RXD 0x5b8 |

Definition at line 284 of file gpio_defs.h.

| #define R_PAD_CFG_DW0_UART1_TXD 0x5c0 |

Definition at line 288 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_NORTH_ALL_0 0x90 |

Definition at line 95 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_NORTH_ALL_1 0x98 |

Definition at line 97 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_SOUTH_DFX_0 0x90 |

Definition at line 100 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_SOUTH_GROUP0_0 0x98 |

Definition at line 102 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_SOUTH_GROUP0_1 0xA0 |

Definition at line 104 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_SOUTH_GROUP1_0 0xA8 |

Definition at line 106 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCK_SOUTH_GROUP1_1 0xB0 |

Definition at line 108 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_NORTH_ALL_0 0x94 |

Definition at line 96 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_NORTH_ALL_1 0x9C |

Definition at line 98 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_SOUTH_DFX_0 0x94 |

Definition at line 101 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_SOUTH_GROUP0_0 0x9C |

Definition at line 103 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_SOUTH_GROUP0_1 0xA4 |

Definition at line 105 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_SOUTH_GROUP1_0 0xAC |

Definition at line 107 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_GPP_PADCFGLOCKTX_SOUTH_GROUP1_1 0xB4 |

Definition at line 109 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC1_PADCFGLOCK_1 0x98 |

Definition at line 30 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC1_PADCFGLOCKTX_1 0x9C |

Definition at line 31 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_GPI_GPE_EN 0x0160 |

Definition at line 36 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_GPI_GPE_STS 0x0140 |

Definition at line 35 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_GPI_IE 0x0120 |

Definition at line 34 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_GPI_IS 0x0100 |

Definition at line 33 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_GPI_VWM_EN 0x70 |

Definition at line 27 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_HOSTSW_OWN 0xC0 |

Definition at line 32 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_NMI_EN 0x01E0 |

Definition at line 40 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_NMI_STS 0x01C0 |

Definition at line 39 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_PAD_OWN 0x20 |

Definition at line 26 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_PADCFG_OFFSET 0x400 |

Definition at line 41 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_PADCFGLOCK 0x90 |

Definition at line 28 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_PADCFGLOCKTX 0x94 |

Definition at line 29 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_SMI_EN 0x01A0 |

Definition at line 38 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_NC_SMI_STS 0x0180 |

Definition at line 37 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_GPI_GPE_EN 0x0164 |

Definition at line 71 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_GPI_GPE_STS 0x0144 |

Definition at line 70 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_GPI_IE 0x0124 |

Definition at line 69 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_GPI_IS 0x0104 |

Definition at line 68 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_GPI_VWM_EN 0x74 |

Definition at line 64 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_HOSTSW_OWN 0xC4 |

Definition at line 67 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_NMI_EN 0x01E4 |

Definition at line 75 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_NMI_STS 0x01C4 |

Definition at line 74 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_PAD_OWN 0x2C |

Definition at line 63 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_PADCFG_OFFSET 0x490 |

Definition at line 76 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_PADCFGLOCK 0x98 |

Definition at line 65 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_PADCFGLOCKTX 0x9C |

Definition at line 66 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_SMI_EN 0x01A4 |

Definition at line 73 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC0_SMI_STS 0x0184 |

Definition at line 72 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_GPI_GPE_EN 0x016C |

Definition at line 88 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_GPI_GPE_STS 0x014C |

Definition at line 87 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_GPI_IE 0x012C |

Definition at line 86 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_GPI_IS 0x010C |

Definition at line 85 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_GPI_VWM_EN 0x7C |

Definition at line 81 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_HOSTSW_OWN 0xCC |

Definition at line 84 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_NMI_EN 0x01EC |

Definition at line 92 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_NMI_STS 0x01CC |

Definition at line 91 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_PAD_OWN 0x48 |

Definition at line 80 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_PADCFG_OFFSET 0x638 |

Definition at line 93 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_PADCFGLOCK 0xA8 |

Definition at line 82 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_PADCFGLOCKTX 0xAC |

Definition at line 83 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_SMI_EN 0x01AC |

Definition at line 90 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC1_SMI_STS 0x018C |

Definition at line 89 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_GPI_GPE_EN 0x0160 |

Definition at line 58 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_GPI_GPE_STS 0x0140 |

Definition at line 57 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_GPI_IE 0x0120 |

Definition at line 56 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_GPI_IS 0x0100 |

Definition at line 55 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_GPI_VWM_EN 0x70 |

Definition at line 51 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_HOSTSW_OWN 0xC0 |

Definition at line 54 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_PAD_OWN 0x20 |

Definition at line 50 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_PADCFG_OFFSET 0x400 |

Definition at line 59 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_PADCFGLOCK 0x90 |

Definition at line 52 of file gpio_defs.h.

| #define R_PCH_PCR_GPIO_SC_DFX_PADCFGLOCKTX 0x94 |

Definition at line 53 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT0 0x01010002 |

Definition at line 352 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT1 0x01010003 |

Definition at line 353 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT10 0x0101000C |

Definition at line 362 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT11 0x0101000D |

Definition at line 363 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT12 0x0101000E |

Definition at line 364 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT13 0x0101000F |

Definition at line 365 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT14 0x01010010 |

Definition at line 366 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT15 0x01010011 |

Definition at line 367 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT2 0x01010004 |

Definition at line 354 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT3 0x01010005 |

Definition at line 355 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT4 0x01010006 |

Definition at line 356 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT5 0x01010007 |

Definition at line 357 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT6 0x01010008 |

Definition at line 358 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT7 0x01010009 |

Definition at line 359 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT8 0x0101000A |

Definition at line 360 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT9 0x0101000B |

Definition at line 361 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT_CLK0 0x01010000 |

Definition at line 350 of file gpio_defs.h.

| #define SOUTH_DFX_DFX_PORT_CLK1 0x01010001 |

Definition at line 351 of file gpio_defs.h.

| #define SOUTH_GROUP0_CTBTRIGINOUT 0x01020030 |

Definition at line 418 of file gpio_defs.h.

| #define SOUTH_GROUP0_CTBTRIGOUT 0x01020031 |

Definition at line 419 of file gpio_defs.h.

| #define SOUTH_GROUP0_CX_PRDY_N 0x0102002E |

Definition at line 416 of file gpio_defs.h.

| #define SOUTH_GROUP0_CX_PREQ_N 0x0102002F |

Definition at line 417 of file gpio_defs.h.

| #define SOUTH_GROUP0_DFX_SPARE2 0x01020032 |

Definition at line 420 of file gpio_defs.h.

| #define SOUTH_GROUP0_DFX_SPARE3 0x01020033 |

Definition at line 421 of file gpio_defs.h.

| #define SOUTH_GROUP0_DFX_SPARE4 0x01020034 |

Definition at line 422 of file gpio_defs.h.

| #define SOUTH_GROUP0_ERROR0_N 0x0102000B |

Definition at line 381 of file gpio_defs.h.

| #define SOUTH_GROUP0_ERROR1_N 0x0102000A |

Definition at line 380 of file gpio_defs.h.

| #define SOUTH_GROUP0_ERROR2_N 0x01020009 |

Definition at line 379 of file gpio_defs.h.

| #define SOUTH_GROUP0_FLEX_CLK_SE0 0x01020019 |

Definition at line 395 of file gpio_defs.h.

| #define SOUTH_GROUP0_FLEX_CLK_SE1 0x0102001A |

Definition at line 396 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_12 0x01020000 |

Definition at line 370 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_4 0x0102001B |

Definition at line 397 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_5 0x0102001C |

Definition at line 398 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_6 0x0102001D |

Definition at line 399 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_7 0x0102001E |

Definition at line 400 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_8 0x01020027 |

Definition at line 409 of file gpio_defs.h.

| #define SOUTH_GROUP0_GPIO_9 0x01020028 |

Definition at line 410 of file gpio_defs.h.

| #define SOUTH_GROUP0_IERR_N 0x0102000C |

Definition at line 382 of file gpio_defs.h.

| #define SOUTH_GROUP0_MCERR_N 0x0102000D |

Definition at line 383 of file gpio_defs.h.

| #define SOUTH_GROUP0_PCIE_CLKREQ5_N 0x01020002 |

Definition at line 372 of file gpio_defs.h.

| #define SOUTH_GROUP0_PCIE_CLKREQ6_N 0x01020003 |

Definition at line 373 of file gpio_defs.h.

| #define SOUTH_GROUP0_PCIE_CLKREQ7_N 0x01020004 |

Definition at line 374 of file gpio_defs.h.

| #define SOUTH_GROUP0_SATA0_LED_N 0x0102001F |

Definition at line 401 of file gpio_defs.h.

| #define SOUTH_GROUP0_SATA0_SDOUT 0x01020023 |

Definition at line 405 of file gpio_defs.h.

| #define SOUTH_GROUP0_SATA1_LED_N 0x01020020 |

Definition at line 402 of file gpio_defs.h.

| #define SOUTH_GROUP0_SATA1_SDOUT 0x01020024 |

Definition at line 406 of file gpio_defs.h.

| #define SOUTH_GROUP0_SATA_PDETECT0 0x01020021 |

Definition at line 403 of file gpio_defs.h.

| #define SOUTH_GROUP0_SATA_PDETECT1 0x01020022 |

Definition at line 404 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB0_LEG_ALRT_N 0x01020010 |

Definition at line 386 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB0_LEG_CLK 0x0102000E |

Definition at line 384 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB0_LEG_DATA 0x0102000F |

Definition at line 385 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB1_HOST_CLK 0x01020012 |

Definition at line 388 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB1_HOST_DATA 0x01020011 |

Definition at line 387 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB2_PECI_CLK 0x01020014 |

Definition at line 390 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB2_PECI_DATA 0x01020013 |

Definition at line 389 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB3_CLTT_CLK 0x01020001 |

Definition at line 369 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB3_CLTT_DATA 0x01020000 |

Definition at line 368 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB4_CSME0_ALRT_N 0x01020017 |

Definition at line 393 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB4_CSME0_CLK 0x01020016 |

Definition at line 392 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB4_CSME0_DATA 0x01020015 |

Definition at line 391 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB5_GBE_ALRT_N 0x01020001 |

Definition at line 371 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB5_GBE_CLK 0x01020007 |

Definition at line 377 of file gpio_defs.h.

| #define SOUTH_GROUP0_SMB5_GBE_DATA 0x01020008 |

Definition at line 378 of file gpio_defs.h.

| #define SOUTH_GROUP0_TCK 0x01020029 |

Definition at line 411 of file gpio_defs.h.

| #define SOUTH_GROUP0_TDI 0x0102002C |

Definition at line 414 of file gpio_defs.h.

| #define SOUTH_GROUP0_TDO 0x0102002D |

Definition at line 415 of file gpio_defs.h.

| #define SOUTH_GROUP0_TMS 0x0102002B |

Definition at line 413 of file gpio_defs.h.

| #define SOUTH_GROUP0_TRST_N 0x0102002A |

Definition at line 412 of file gpio_defs.h.

| #define SOUTH_GROUP0_UART0_RXD 0x01020005 |

Definition at line 375 of file gpio_defs.h.

| #define SOUTH_GROUP0_UART0_TXD 0x01020006 |

Definition at line 376 of file gpio_defs.h.

| #define SOUTH_GROUP0_UART1_RXD 0x01020025 |

Definition at line 407 of file gpio_defs.h.

| #define SOUTH_GROUP0_UART1_TXD 0x01020026 |

Definition at line 408 of file gpio_defs.h.

| #define SOUTH_GROUP0_USB_OC0_N 0x01020018 |

Definition at line 394 of file gpio_defs.h.

| #define SOUTH_GROUP1_ADR_TRIGGER 0x01030002 |

Definition at line 425 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_CLK 0x01030020 |

Definition at line 456 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_CMD 0x0103001E |

Definition at line 454 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D0 0x01030021 |

Definition at line 457 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D1 0x01030022 |

Definition at line 458 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D2 0x01030023 |

Definition at line 459 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D3 0x01030024 |

Definition at line 460 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D4 0x01030025 |

Definition at line 461 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D5 0x01030026 |

Definition at line 462 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D6 0x01030027 |

Definition at line 463 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_D7 0x01030028 |

Definition at line 464 of file gpio_defs.h.

| #define SOUTH_GROUP1_EMMC_STROBE 0x0103001F |

Definition at line 455 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_ALRT0_N 0x0103001A |

Definition at line 450 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_CLK 0x01030018 |

Definition at line 448 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_CLK_LOOPBK 0x0103001D |

Definition at line 453 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_CS0_N 0x01030017 |

Definition at line 447 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_IO0 0x01030013 |

Definition at line 443 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_IO1 0x01030014 |

Definition at line 444 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_IO2 0x01030015 |

Definition at line 445 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_IO3 0x01030016 |

Definition at line 446 of file gpio_defs.h.

| #define SOUTH_GROUP1_ESPI_RST_N 0x01030019 |

Definition at line 449 of file gpio_defs.h.

| #define SOUTH_GROUP1_GPIO_10 0x0103001B |

Definition at line 451 of file gpio_defs.h.

| #define SOUTH_GROUP1_GPIO_11 0x0103001C |

Definition at line 452 of file gpio_defs.h.

| #define SOUTH_GROUP1_GPIO_3 0x01030029 |

Definition at line 465 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_AC_PRESENT 0x01030002 |

Definition at line 426 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_PLTRST_N 0x01030008 |

Definition at line 432 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_PWRBTN_N 0x01030006 |

Definition at line 430 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_RESETBUTTON_N 0x01030007 |

Definition at line 431 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_SLP_S3_N 0x01030004 |

Definition at line 428 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_SLP_S45_N 0x01030003 |

Definition at line 427 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_SUSCLK 0x01030001 |

Definition at line 424 of file gpio_defs.h.

| #define SOUTH_GROUP1_PMU_WAKE_N 0x01030005 |

Definition at line 429 of file gpio_defs.h.

| #define SOUTH_GROUP1_SLP_S0IX_N 0x0103000A |

Definition at line 434 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_CLK 0x01030011 |

Definition at line 441 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_CLK_LOOPBK 0x01030012 |

Definition at line 442 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_CS0_N 0x0103000B |

Definition at line 435 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_CS1_N 0x0103000C |

Definition at line 436 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_IO2 0x0103000F |

Definition at line 439 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_IO3 0x01030010 |

Definition at line 440 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_MISO_IO1 0x0103000E |

Definition at line 438 of file gpio_defs.h.

| #define SOUTH_GROUP1_SPI_MOSI_IO0 0x0103000D |

Definition at line 437 of file gpio_defs.h.

| #define SOUTH_GROUP1_SUS_STAT_N 0x01030009 |

Definition at line 433 of file gpio_defs.h.

| #define SOUTH_GROUP1_SUSPWRDNACK 0x01030000 |

Definition at line 423 of file gpio_defs.h.

| #define UNIQUE_ID_MASK 0xFF000000 |

Definition at line 475 of file gpio_defs.h.

| #define UNIQUE_ID_POSITION 24 |

Definition at line 476 of file gpio_defs.h.

| #define V_PCH_GPIO_GROUP_MAX 4 |

Definition at line 17 of file gpio_defs.h.

| #define V_PCH_GPIO_NC_PAD_MAX 41 |

Definition at line 13 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_GPIO 0 |

Definition at line 190 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_1 1 |

Definition at line 191 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_2 2 |

Definition at line 192 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_3 3 |

Definition at line 193 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_4 4 |

Definition at line 194 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_5 5 |

Definition at line 195 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_6 6 |

Definition at line 196 of file gpio_defs.h.

| #define V_PCH_GPIO_PAD_MODE_NAT_7 7 |

Definition at line 197 of file gpio_defs.h.

| #define V_PCH_GPIO_PADTOL_CLEAR 0x00 |

Definition at line 231 of file gpio_defs.h.

| #define V_PCH_GPIO_PADTOL_NONE 0x00 |

Definition at line 230 of file gpio_defs.h.

| #define V_PCH_GPIO_PADTOL_SET 0x01 |

Definition at line 232 of file gpio_defs.h.

| #define V_PCH_GPIO_PRE_GFRX_SEL_DIS 0x00 |

Definition at line 146 of file gpio_defs.h.

| #define V_PCH_GPIO_PRE_GFRX_SEL_EN 0x01 |

Definition at line 147 of file gpio_defs.h.

| #define V_PCH_GPIO_RST_CONF_DEEP_RST 0x01 |

Definition at line 119 of file gpio_defs.h.

| #define V_PCH_GPIO_RST_CONF_GPIO_RST 0x02 |

Definition at line 120 of file gpio_defs.h.

| #define V_PCH_GPIO_RST_CONF_POW_GOOD 0x00 |

Definition at line 118 of file gpio_defs.h.

| #define V_PCH_GPIO_RST_CONF_RESUME_RST 0x03 |

Definition at line 121 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_APIC_ROUTE_DIS 0x00 |

Definition at line 166 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_APIC_ROUTE_EN 0x01 |

Definition at line 167 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_LVL_EDG_0 0x02 |

Definition at line 140 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_LVL_EDG_EDG 0x01 |

Definition at line 139 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_LVL_EDG_LVL 0x00 |

Definition at line 138 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_LVL_EDG_RIS_FAL 0x03 |

Definition at line 141 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_NMI_ROUTE_DIS 0x00 |

Definition at line 184 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_NMI_ROUTE_EN 0x01 |

Definition at line 185 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_PAD_STATE_INT 0x01 |

Definition at line 127 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_PAD_STATE_RAW 0x00 |

Definition at line 126 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_RAW1_DIS 0x00 |

Definition at line 132 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_RAW1_EN 0x01 |

Definition at line 133 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_SCI_ROUTE_DIS 0x00 |

Definition at line 172 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_SCI_ROUTE_EN 0x01 |

Definition at line 173 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_SMI_ROUTE_DIS 0x00 |

Definition at line 178 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_SMI_ROUTE_EN 0x01 |

Definition at line 179 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_STATE_HIGH 0x01 |

Definition at line 215 of file gpio_defs.h.

| #define V_PCH_GPIO_RX_STATE_LOW 0x00 |

Definition at line 214 of file gpio_defs.h.

| #define V_PCH_GPIO_RXDIS_DIS 0x01 |

Definition at line 203 of file gpio_defs.h.

| #define V_PCH_GPIO_RXDIS_EN 0x00 |

Definition at line 202 of file gpio_defs.h.

| #define V_PCH_GPIO_RXINV_NO 0x00 |

Definition at line 152 of file gpio_defs.h.

| #define V_PCH_GPIO_RXINV_YES 0x01 |

Definition at line 153 of file gpio_defs.h.

| #define V_PCH_GPIO_RXTXENCFG_DEF_FUN 0x00 |

Definition at line 158 of file gpio_defs.h.

| #define V_PCH_GPIO_RXTXENCFG_TX_EN_H 0x02 |

Definition at line 160 of file gpio_defs.h.

| #define V_PCH_GPIO_RXTXENCFG_TX_EN_L 0x01 |

Definition at line 159 of file gpio_defs.h.

| #define V_PCH_GPIO_RXTXENCFG_TXRXEN 0x03 |

Definition at line 161 of file gpio_defs.h.

| #define V_PCH_GPIO_SC0_PAD_MAX 53 |

Definition at line 15 of file gpio_defs.h.

| #define V_PCH_GPIO_SC1_PAD_MAX 42 |

Definition at line 16 of file gpio_defs.h.

| #define V_PCH_GPIO_SC_DFX_PAD_MAX 18 |

Definition at line 14 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_NATIVE 0x0F |

Definition at line 246 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPD_20K 0x04 |

Definition at line 239 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPD_5K 0x02 |

Definition at line 238 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPD_NONE 0x00 |

Definition at line 237 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPU_1K 0x09 |

Definition at line 241 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPU_1K_2K 0x0D |

Definition at line 245 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPU_20K 0x0C |

Definition at line 244 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPU_2K 0x0B |

Definition at line 242 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPU_5K 0x0A |

Definition at line 243 of file gpio_defs.h.

| #define V_PCH_GPIO_TERM_WPU_NONE 0x08 |

Definition at line 240 of file gpio_defs.h.

| #define V_PCH_GPIO_TX_STATE_HIGH 0x01 |

Definition at line 221 of file gpio_defs.h.

| #define V_PCH_GPIO_TX_STATE_LOW 0x00 |

Definition at line 220 of file gpio_defs.h.

| #define V_PCH_GPIO_TXDIS_DIS 0x01 |

Definition at line 209 of file gpio_defs.h.

| #define V_PCH_GPIO_TXDIS_EN 0x00 |

Definition at line 208 of file gpio_defs.h.