|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

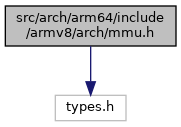

#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | mmu_context |

Functions | |

| void | mmu_init (void) |

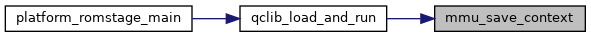

| void | mmu_save_context (struct mmu_context *mmu_context) |

| void | mmu_restore_context (const struct mmu_context *mmu_context) |

| void | mmu_config_range (void *start, size_t size, uint64_t tag) |

| void | mmu_enable (void) |

| void | mmu_disable (void) |

| #define BITS_RESOLVED_PER_LVL (GRANULE_SIZE_SHIFT - 3) |

| #define BLOCK_SH_INNER_SHAREABLE (3 << BLOCK_SH_SHIFT) |

| #define BLOCK_SH_NON_SHAREABLE (0 << BLOCK_SH_SHIFT) |

| #define BLOCK_SH_OUTER_SHAREABLE (2 << BLOCK_SH_SHIFT) |

| #define BLOCK_SH_UNPREDICTABLE (1 << BLOCK_SH_SHIFT) |

| #define GRANULE_SIZE (1 << GRANULE_SIZE_SHIFT) |

| #define GRANULE_SIZE_MASK ((1 << GRANULE_SIZE_SHIFT) - 1) |

| #define L0_ADDR_MASK (((1UL << BITS_RESOLVED_PER_LVL) - 1) << L0_ADDR_SHIFT) |

| #define L0_ADDR_SHIFT (GRANULE_SIZE_SHIFT + BITS_RESOLVED_PER_LVL * 3) |

| #define L0_XLAT_SIZE (1UL << L0_ADDR_SHIFT) |

| #define L1_ADDR_MASK (((1UL << BITS_RESOLVED_PER_LVL) - 1) << L1_ADDR_SHIFT) |

| #define L1_ADDR_SHIFT (GRANULE_SIZE_SHIFT + BITS_RESOLVED_PER_LVL * 2) |

| #define L1_XLAT_SIZE (1UL << L1_ADDR_SHIFT) |

| #define L2_ADDR_MASK (((1UL << BITS_RESOLVED_PER_LVL) - 1) << L2_ADDR_SHIFT) |

| #define L2_ADDR_SHIFT (GRANULE_SIZE_SHIFT + BITS_RESOLVED_PER_LVL * 1) |

| #define L2_XLAT_SIZE (1UL << L2_ADDR_SHIFT) |

| #define L3_ADDR_MASK (((1UL << BITS_RESOLVED_PER_LVL) - 1) << L3_ADDR_SHIFT) |

| #define L3_ADDR_SHIFT (GRANULE_SIZE_SHIFT + BITS_RESOLVED_PER_LVL * 0) |

| #define L3_XLAT_SIZE (1UL << L3_ADDR_SHIFT) |

| #define MAIR_ATTRIBUTES |

| #define TCR_IRGN0_NM_NC (0x00 << TCR_IRGN0_SHIFT) |

| #define TCR_IRGN0_NM_WBNWAC (0x03 << TCR_IRGN0_SHIFT) |

| #define TCR_IRGN0_NM_WBWAC (0x01 << TCR_IRGN0_SHIFT) |

| #define TCR_IRGN0_NM_WTC (0x02 << TCR_IRGN0_SHIFT) |

| #define TCR_ORGN0_NM_NC (0x00 << TCR_ORGN0_SHIFT) |

| #define TCR_ORGN0_NM_WBNWAC (0x03 << TCR_ORGN0_SHIFT) |

| #define TCR_ORGN0_NM_WBWAC (0x01 << TCR_ORGN0_SHIFT) |

| #define TCR_ORGN0_NM_WTC (0x02 << TCR_ORGN0_SHIFT) |

| #define TCR_PS_16TB (0x4 << TCR_PS_SHIFT) |

| #define TCR_PS_1TB (0x2 << TCR_PS_SHIFT) |

| #define TCR_PS_256TB (0x5 << TCR_PS_SHIFT) |

| #define TCR_PS_4GB (0x0 << TCR_PS_SHIFT) |

| #define TCR_PS_4TB (0x3 << TCR_PS_SHIFT) |

| #define TCR_PS_64GB (0x1 << TCR_PS_SHIFT) |

| #define TCR_SH0_IS (0x3 << TCR_SH0_SHIFT) |

| #define TCR_SH0_NC (0x0 << TCR_SH0_SHIFT) |

| #define TCR_SH0_OS (0x2 << TCR_SH0_SHIFT) |

| #define TCR_TBI_IGNORED (0x1 << TCR_TBI_SHIFT) |

| #define TCR_TBI_USED (0x0 << TCR_TBI_SHIFT) |

| #define TCR_TG0_16KB (0x2 << TCR_TG0_SHIFT) |

| #define TCR_TG0_4KB (0x0 << TCR_TG0_SHIFT) |

| #define TCR_TG0_64KB (0x1 << TCR_TG0_SHIFT) |

| #define TCR_TOSZ (64 - BITS_PER_VA) |

| #define XLAT_ADDR_MASK ((1UL << BITS_PER_VA) - GRANULE_SIZE) |

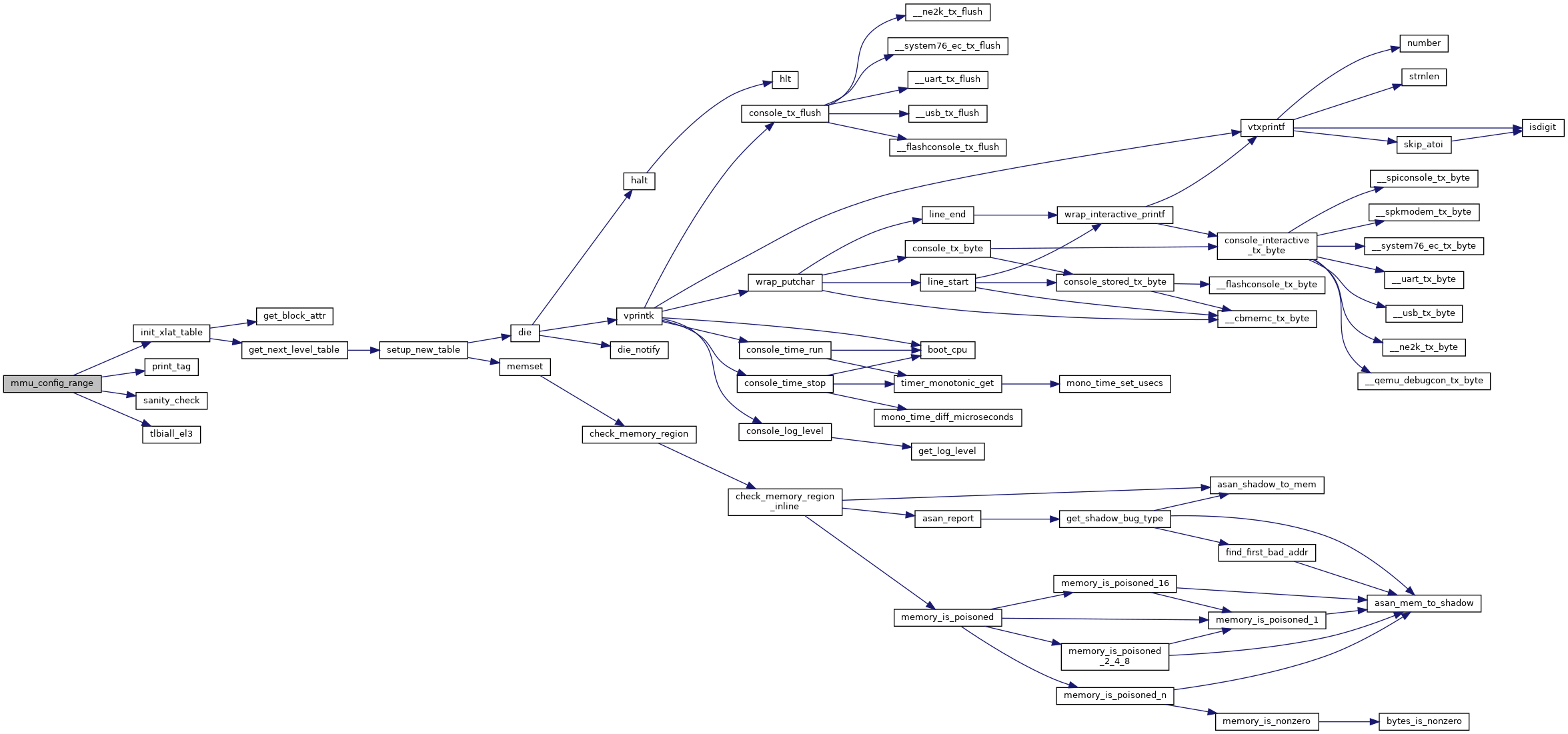

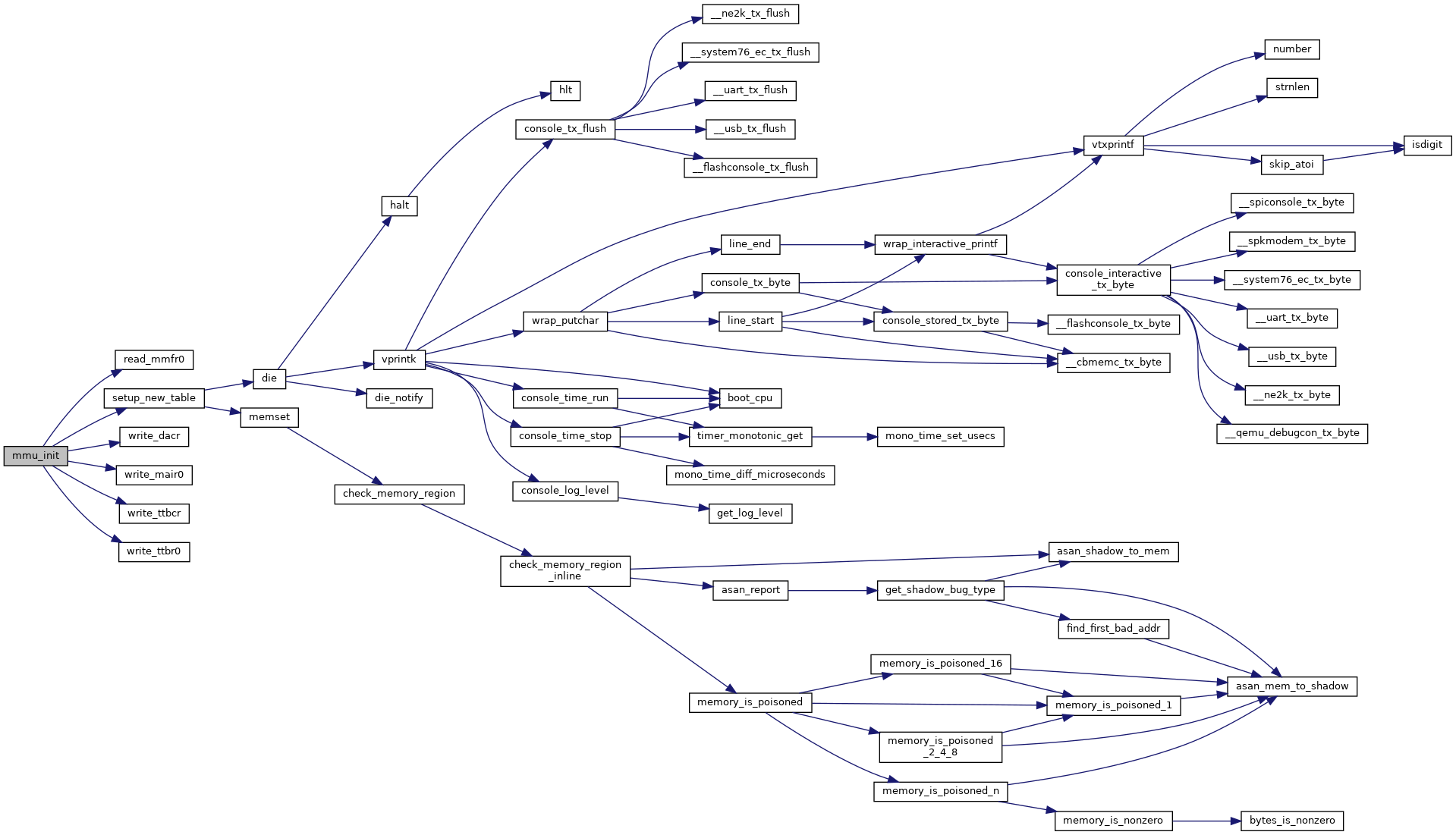

Definition at line 210 of file mmu.c.

References BIOS_INFO, dsb, init_xlat_table(), isb, print_tag(), printk, sanity_check(), and tlbiall_el3().

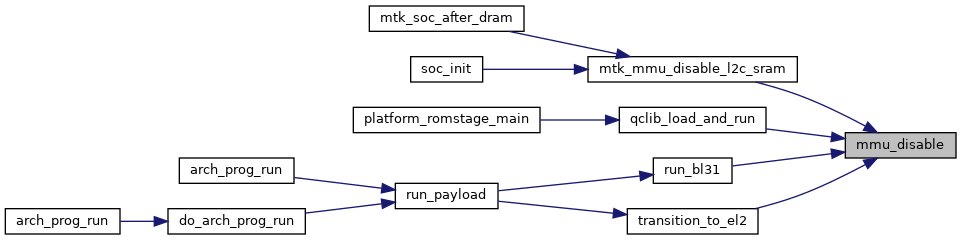

Referenced by mtk_mmu_disable_l2c_sram(), qclib_load_and_run(), run_bl31(), and transition_to_el2().

Definition at line 293 of file mmu.c.

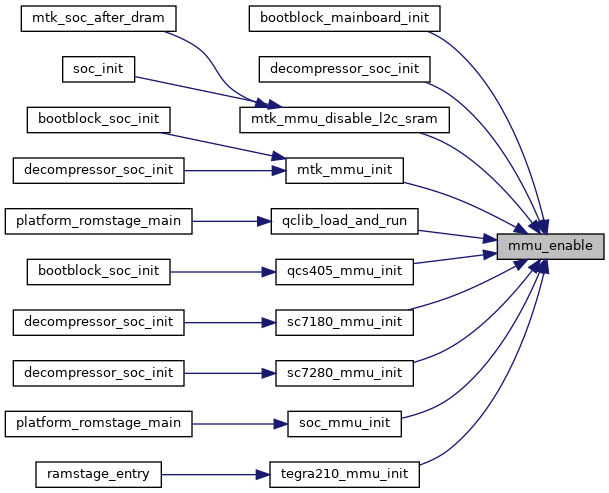

References assert_correct_ttb_mapping(), isb, SCTLR_C, SCTLR_I, and SCTLR_M.

Referenced by bootblock_mainboard_init(), decompressor_soc_init(), mtk_mmu_disable_l2c_sram(), mtk_mmu_init(), qclib_load_and_run(), qcs405_mmu_init(), sc7180_mmu_init(), sc7280_mmu_init(), soc_mmu_init(), and tegra210_mmu_init().

Definition at line 242 of file mmu.c.

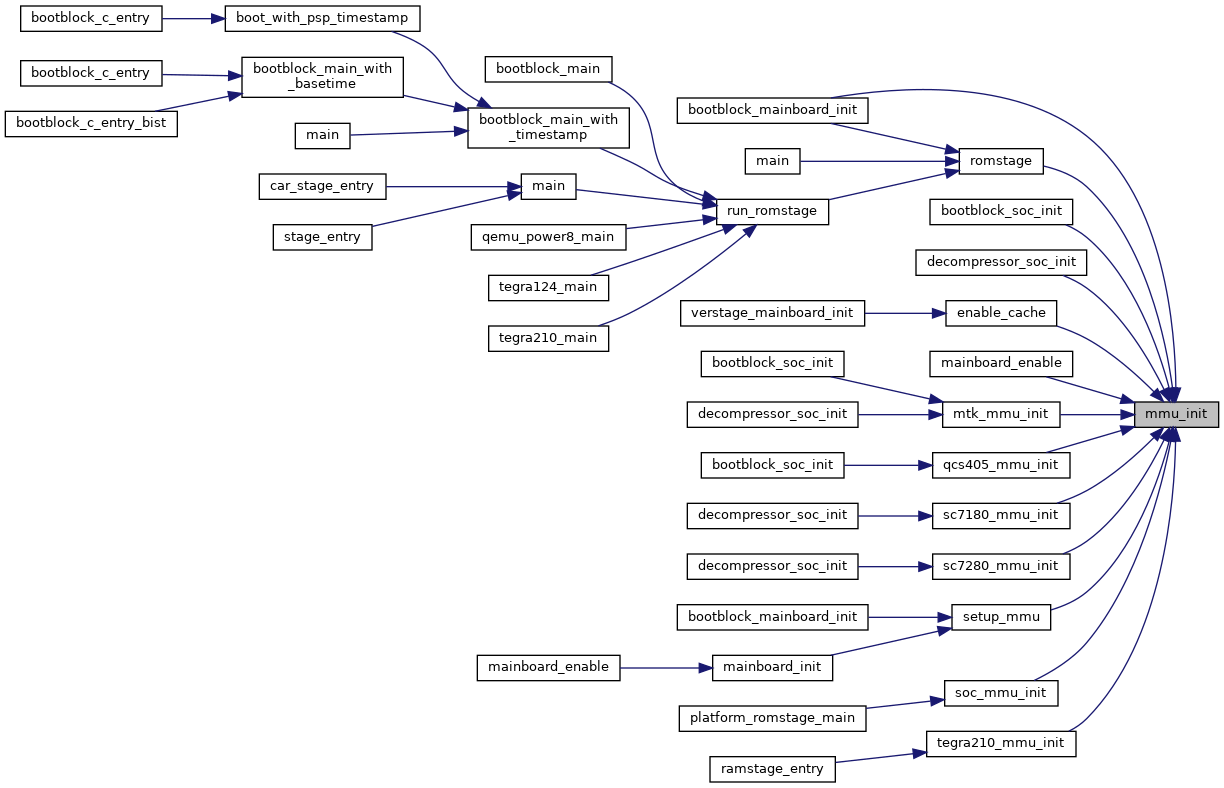

References assert, ASSERT, ATTR_NEXTLEVEL, ATTR_UNUSED, BIOS_DEBUG, BLOCK_SIZE, CONFIG, GRANULE_SIZE, INVALID_DESC, KiB, L0_XLAT_SIZE, MAIR_ATTRIBUTES, MAIR_INDX_NC, MAIR_INDX_WB, MAIR_INDX_WT, NEXTLEVEL_MASK, PAGE_SIZE, printk, read_mmfr0(), setup_new_table(), SUBTABLE_PTES, TCR_IRGN0_NM_WBWAC, TCR_ORGN0_NM_WBWAC, TCR_PS_256TB, TCR_SH0_IS, TCR_TBI_USED, TCR_TG0_4KB, TCR_TOSZ, ttb_buff, UNUSED_DESC, write_dacr(), write_mair0(), write_ttbcr(), and write_ttbr0().

Referenced by bootblock_mainboard_init(), bootblock_soc_init(), decompressor_soc_init(), enable_cache(), mainboard_enable(), mtk_mmu_init(), qcs405_mmu_init(), romstage(), sc7180_mmu_init(), sc7280_mmu_init(), setup_mmu(), soc_mmu_init(), and tegra210_mmu_init().

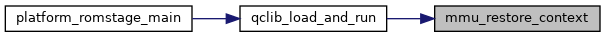

| void mmu_restore_context | ( | const struct mmu_context * | mmu_context | ) |

Definition at line 276 of file mmu.c.

References assert, mmu_context::mair, mmu_context::tcr, and tlb_invalidate_all().

Referenced by qclib_load_and_run().

| void mmu_save_context | ( | struct mmu_context * | mmu_context | ) |

Definition at line 262 of file mmu.c.

References assert, mmu_context::mair, and mmu_context::tcr.

Referenced by qclib_load_and_run().