|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

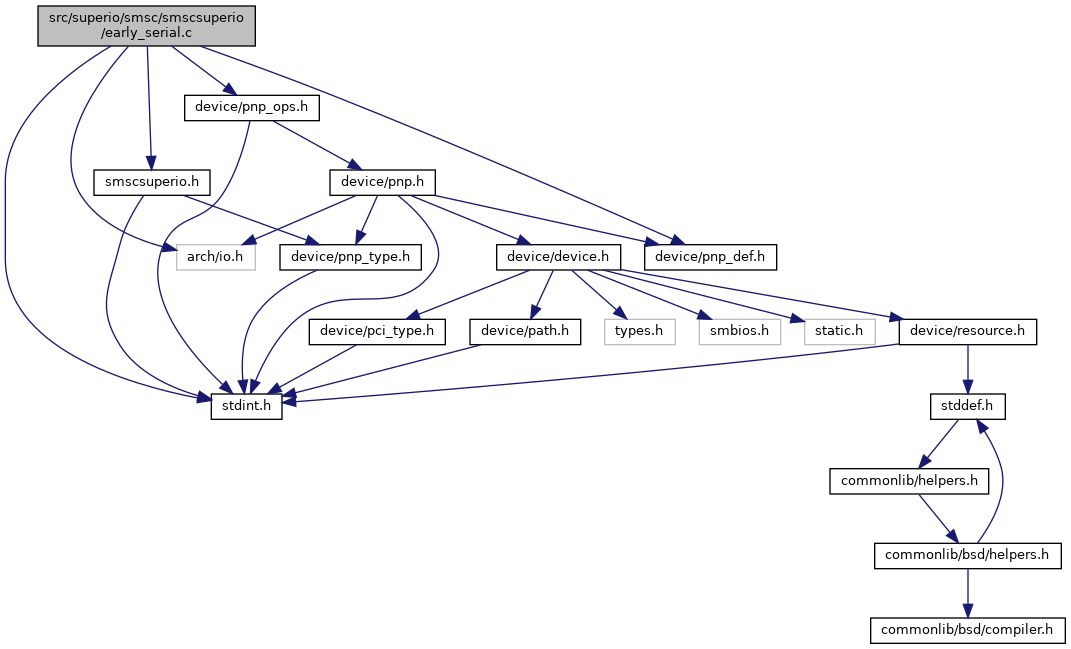

#include <arch/io.h>#include <device/pnp_ops.h>#include <device/pnp_def.h>#include <stdint.h>#include "smscsuperio.h"

Go to the source code of this file.

Macros | |

| #define | SMSC_ENTRY_KEY 0x55 |

| #define | SMSC_EXIT_KEY 0xAA |

Functions | |

| static void | pnp_enter_conf_state (pnp_devfn_t dev) |

| static void | pnp_exit_conf_state (pnp_devfn_t dev) |

| void | smscsuperio_enable_serial (pnp_devfn_t dev, u16 iobase) |

| Enable the specified serial port. More... | |

| #define SMSC_ENTRY_KEY 0x55 |

Definition at line 10 of file early_serial.c.

| #define SMSC_EXIT_KEY 0xAA |

Definition at line 11 of file early_serial.c.

|

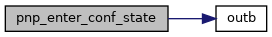

static |

Definition at line 14 of file early_serial.c.

References outb(), and SMSC_ENTRY_KEY.

|

static |

Definition at line 21 of file early_serial.c.

References outb(), and SMSC_EXIT_KEY.

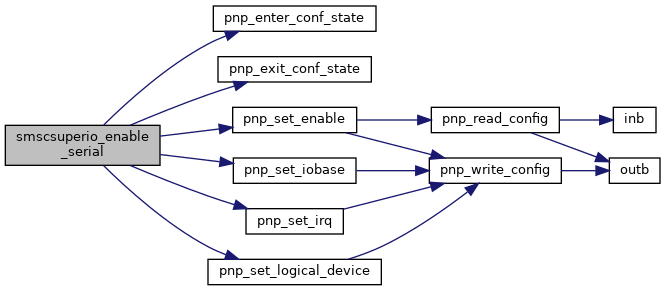

| void smscsuperio_enable_serial | ( | pnp_devfn_t | dev, |

| u16 | iobase | ||

| ) |

Enable the specified serial port.

| dev | The device to use. |

| iobase | The I/O base of the serial port (usually 0x3f8/0x2f8). |

Definition at line 33 of file early_serial.c.

References pnp_enter_conf_state(), pnp_exit_conf_state(), PNP_IDX_IO0, PNP_IDX_IRQ0, pnp_set_enable(), pnp_set_iobase(), pnp_set_irq(), and pnp_set_logical_device().

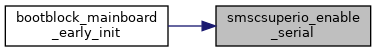

Referenced by bootblock_mainboard_early_init().