|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

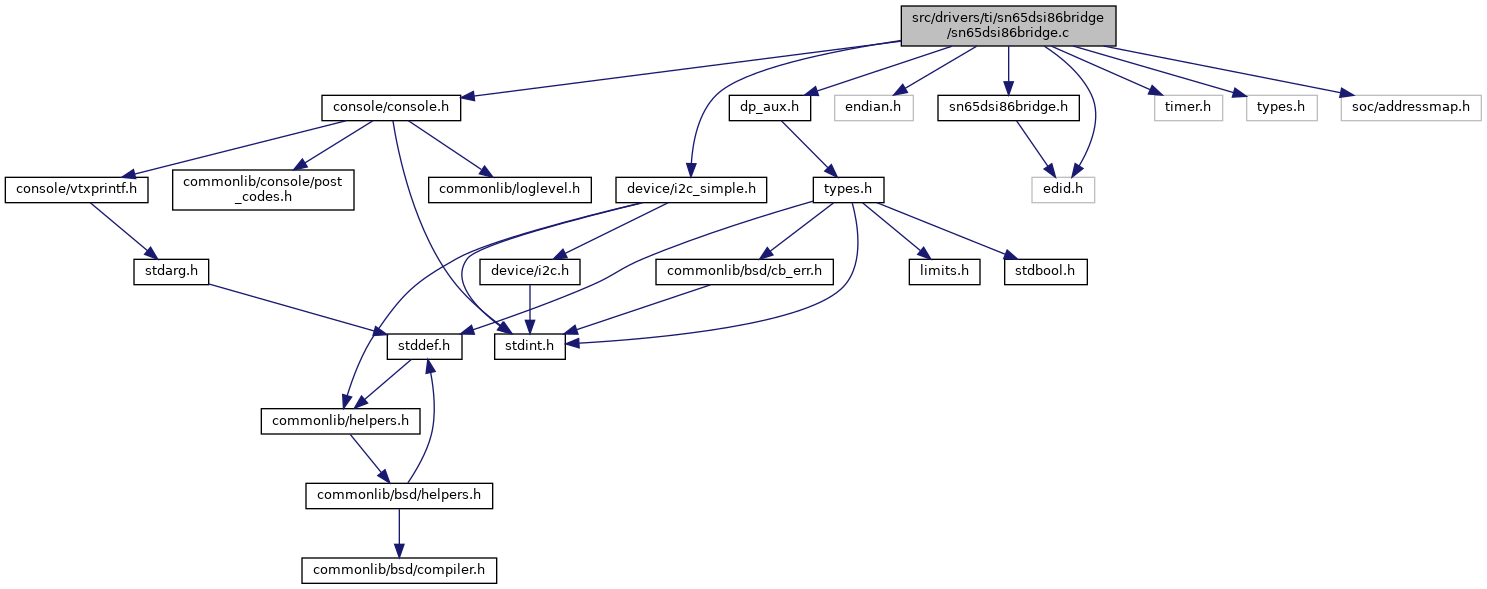

#include <console/console.h>#include <endian.h>#include <device/i2c_simple.h>#include <dp_aux.h>#include <edid.h>#include <timer.h>#include <types.h>#include <soc/addressmap.h>#include "sn65dsi86bridge.h"

Go to the source code of this file.

Macros | |

| #define | BRIDGE_GETHIGHERBYTE(x) ((uint8_t)((x & 0xff00) >> 8)) |

| #define | BRIDGE_GETLOWERBYTE(x) ((uint8_t)(x & 0x00ff)) |

| #define | DP_CLK_FUDGE_NUM 10 |

| #define | DP_CLK_FUDGE_DEN 8 |

| #define | DP_BRIDGE_DPCD_REV 0x700 |

| #define | DP_BRIDGE_11 0x00 |

| #define | DP_BRIDGE_12 0x01 |

| #define | DP_BRIDGE_13 0x02 |

| #define | DP_BRIDGE_14 0x03 |

| #define | DP_BRIDGE_CONFIGURATION_SET 0x10a |

| #define | DP_MAX_LINK_RATE 0x001 |

| #define | DP_MAX_LANE_COUNT 0x002 |

| #define | DP_SUPPORTED_LINK_RATES 0x010 /* eDP 1.4 */ |

| #define | DP_MAX_LINK_RATE 0x001 |

| #define | DP_MAX_SUPPORTED_RATES 8 /* 16-bit little-endian */ |

| #define | DP_LANE_COUNT_MASK 0xf |

| #define | DP_LINK_BW_SET 0x100 |

| #define | DP_LINK_BW_1_62 0x06 |

| #define | DP_LINK_BW_2_7 0x0a |

| #define | DP_LINK_BW_5_4 0x14 |

| #define | AUX_CMD_SEND 0x1 |

| #define | MIN_DSI_CLK_FREQ_MHZ 40 |

| #define | MAX_DSI_CLK_FREQ_MHZ 750 |

Variables | |

| static const unsigned int | sn65dsi86_bridge_dp_rate_lut [] |

| #define AUX_CMD_SEND 0x1 |

Definition at line 40 of file sn65dsi86bridge.c.

Definition at line 13 of file sn65dsi86bridge.c.

Definition at line 14 of file sn65dsi86bridge.c.

| #define DP_BRIDGE_11 0x00 |

Definition at line 22 of file sn65dsi86bridge.c.

| #define DP_BRIDGE_12 0x01 |

Definition at line 23 of file sn65dsi86bridge.c.

| #define DP_BRIDGE_13 0x02 |

Definition at line 24 of file sn65dsi86bridge.c.

| #define DP_BRIDGE_14 0x03 |

Definition at line 25 of file sn65dsi86bridge.c.

| #define DP_BRIDGE_CONFIGURATION_SET 0x10a |

Definition at line 26 of file sn65dsi86bridge.c.

| #define DP_BRIDGE_DPCD_REV 0x700 |

Definition at line 21 of file sn65dsi86bridge.c.

| #define DP_CLK_FUDGE_DEN 8 |

Definition at line 18 of file sn65dsi86bridge.c.

| #define DP_CLK_FUDGE_NUM 10 |

Definition at line 17 of file sn65dsi86bridge.c.

| #define DP_LANE_COUNT_MASK 0xf |

Definition at line 32 of file sn65dsi86bridge.c.

| #define DP_LINK_BW_1_62 0x06 |

Definition at line 36 of file sn65dsi86bridge.c.

| #define DP_LINK_BW_2_7 0x0a |

Definition at line 37 of file sn65dsi86bridge.c.

| #define DP_LINK_BW_5_4 0x14 |

Definition at line 38 of file sn65dsi86bridge.c.

| #define DP_LINK_BW_SET 0x100 |

Definition at line 35 of file sn65dsi86bridge.c.

| #define DP_MAX_LANE_COUNT 0x002 |

Definition at line 28 of file sn65dsi86bridge.c.

| #define DP_MAX_LINK_RATE 0x001 |

Definition at line 30 of file sn65dsi86bridge.c.

| #define DP_MAX_LINK_RATE 0x001 |

Definition at line 30 of file sn65dsi86bridge.c.

| #define DP_MAX_SUPPORTED_RATES 8 /* 16-bit little-endian */ |

Definition at line 31 of file sn65dsi86bridge.c.

| #define DP_SUPPORTED_LINK_RATES 0x010 /* eDP 1.4 */ |

Definition at line 29 of file sn65dsi86bridge.c.

| #define MAX_DSI_CLK_FREQ_MHZ 750 |

Definition at line 42 of file sn65dsi86bridge.c.

| #define MIN_DSI_CLK_FREQ_MHZ 40 |

Definition at line 41 of file sn65dsi86bridge.c.

| anonymous enum |

| Enumerator | |

|---|---|

| HPD_ENABLE | |

| HPD_DISABLE | |

Definition at line 109 of file sn65dsi86bridge.c.

| anonymous enum |

| Enumerator | |

|---|---|

| SOT_ERR_TOL_DSI | |

| CHB_DSI_LANES | |

| CHA_DSI_LANES | |

| DSI_CHANNEL_MODE | |

| LEFT_RIGHT_PIXELS | |

Definition at line 114 of file sn65dsi86bridge.c.

| enum aux_cmd_status |

| Enumerator | |

|---|---|

| NAT_I2C_FAIL | |

| AUX_SHORT | |

| AUX_DFER | |

| AUX_RPLY_TOUT | |

| SEND_INT | |

Definition at line 127 of file sn65dsi86bridge.c.

| enum bridge_regs |

Definition at line 44 of file sn65dsi86bridge.c.

| enum ml_tx_mode |

Definition at line 135 of file sn65dsi86bridge.c.

| enum vstream_config |

| Enumerator | |

|---|---|

| VSTREAM_DISABLE | |

| VSTREAM_ENABLE | |

Definition at line 122 of file sn65dsi86bridge.c.

Definition at line 439 of file sn65dsi86bridge.c.

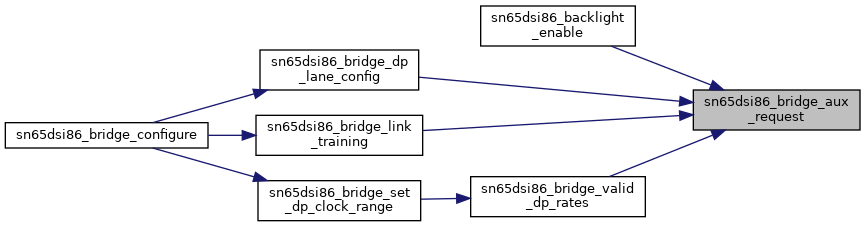

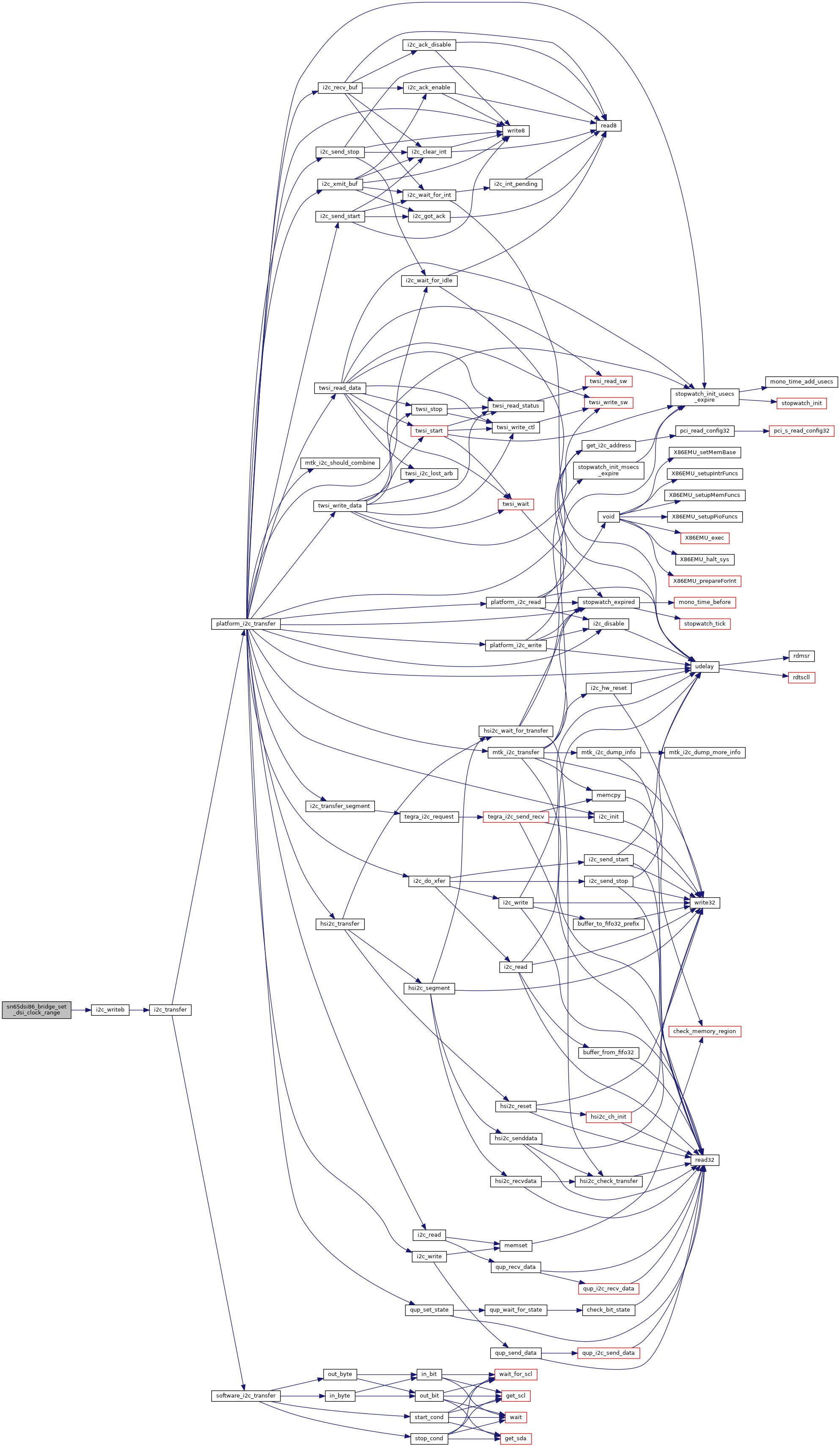

References chip, DP_BACKLIGHT_BRIGHTNESS_MSB, DP_BACKLIGHT_CONTROL_MODE_DPCD, DP_BACKLIGHT_ENABLE, DP_BACKLIGHT_MODE_SET, DP_DISPLAY_CONTROL_REGISTER, DPCD_WRITE, sn65dsi86_bridge_aux_request(), and val.

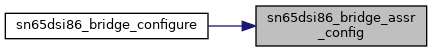

Definition at line 453 of file sn65dsi86bridge.c.

References chip, i2c_write_field(), SN_ENH_FRAME_REG, VSTREAM_DISABLE, and VSTREAM_ENABLE.

Referenced by sn65dsi86_bridge_configure().

|

static |

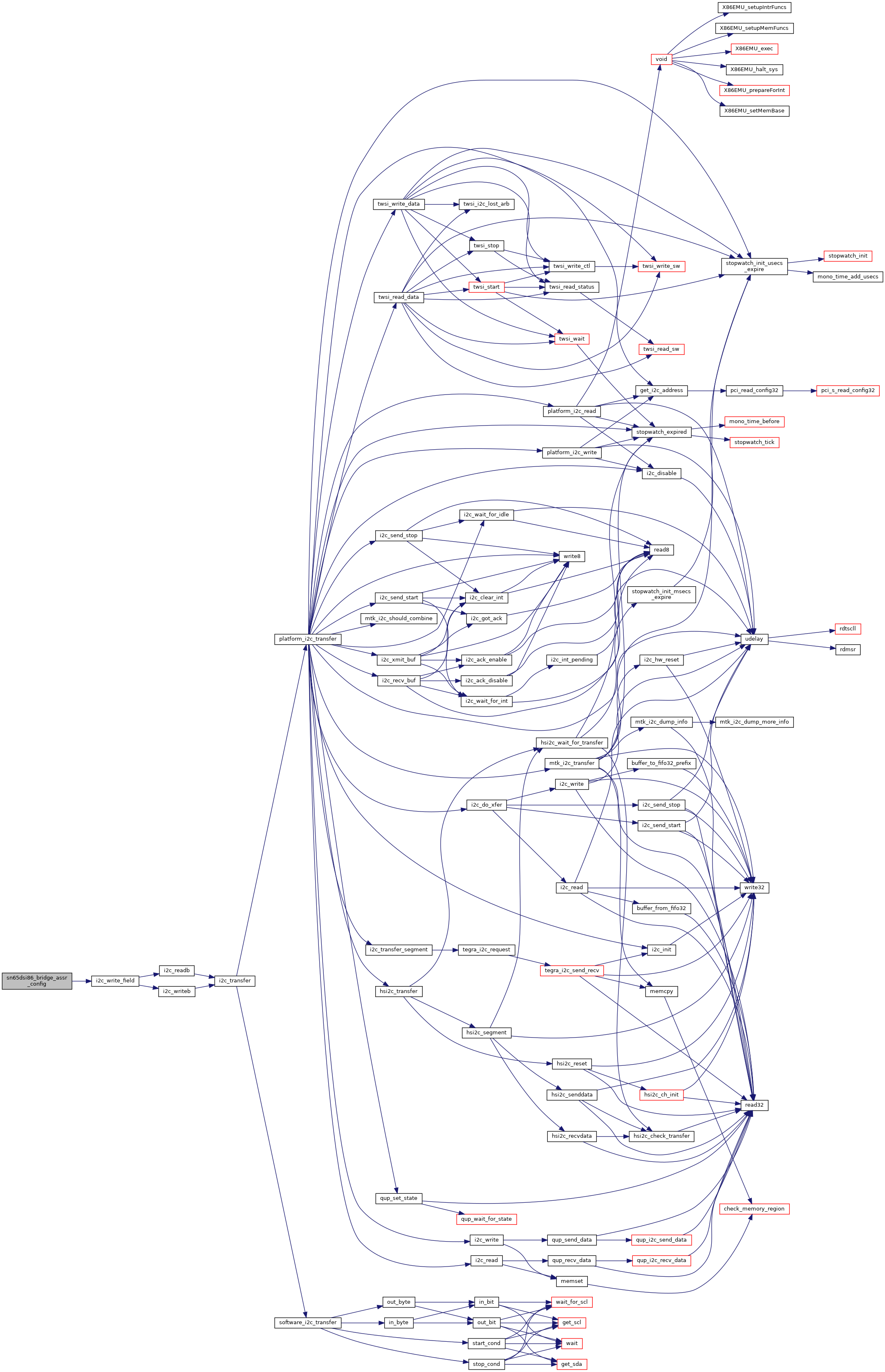

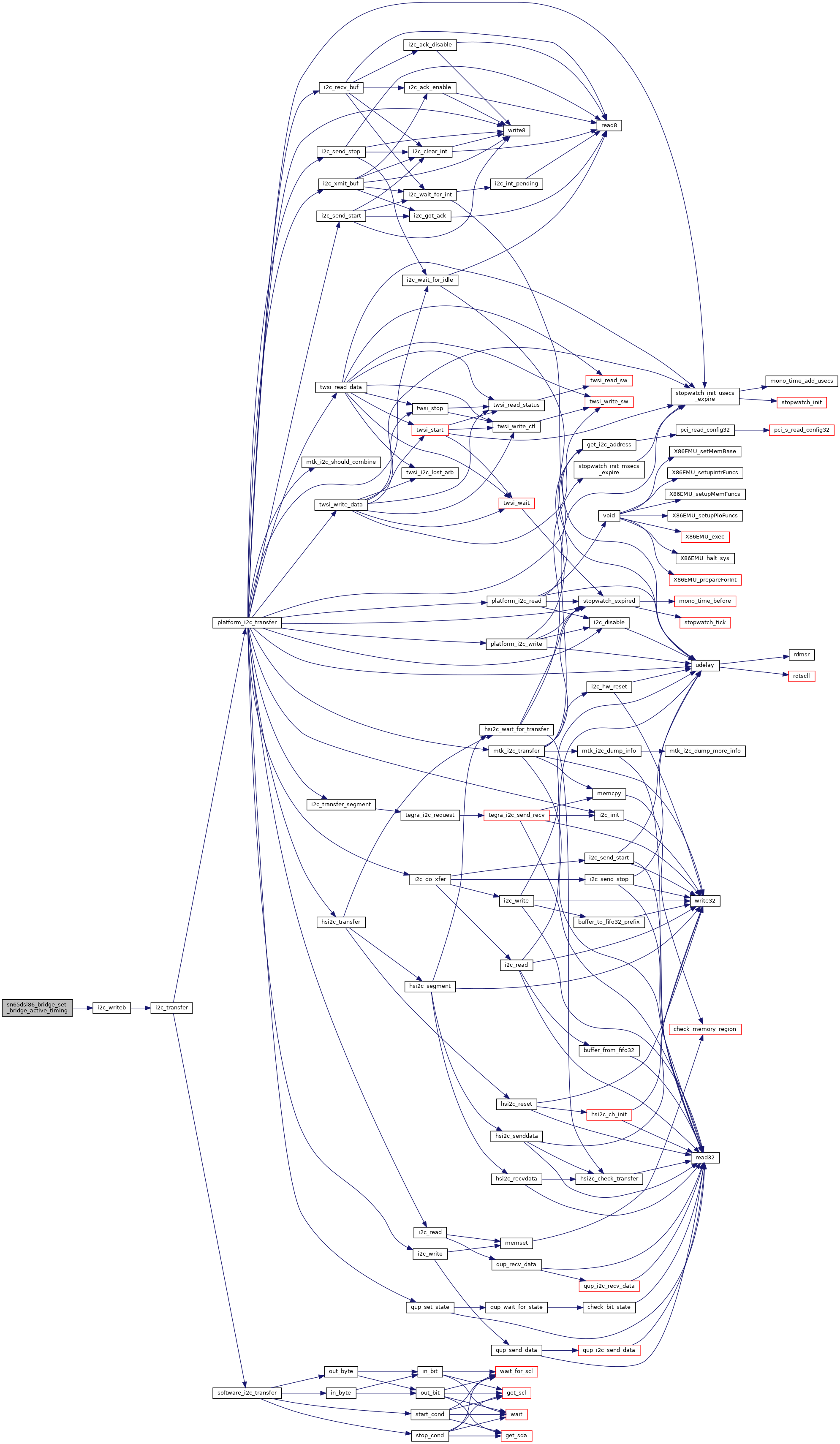

Definition at line 154 of file sn65dsi86bridge.c.

Referenced by sn65dsi86_backlight_enable(), sn65dsi86_bridge_dp_lane_config(), sn65dsi86_bridge_link_training(), and sn65dsi86_bridge_valid_dp_rates().

| void sn65dsi86_bridge_configure | ( | uint8_t | bus, |

| uint8_t | chip, | ||

| struct edid * | edid, | ||

| uint32_t | num_of_lanes, | ||

| uint32_t | dsi_bpp | ||

| ) |

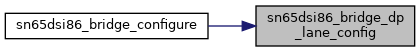

Definition at line 481 of file sn65dsi86bridge.c.

References chip, i2c_write_field(), i2c_writeb(), sn65dsi86_bridge_assr_config(), sn65dsi86_bridge_dp_lane_config(), sn65dsi86_bridge_link_training(), sn65dsi86_bridge_set_bridge_active_timing(), sn65dsi86_bridge_set_dp_clock_range(), sn65dsi86_bridge_set_dsi_clock_range(), SN_COLOR_BAR_REG, SN_DATA_FORMAT_REG, and SN_DSI_LANES_REG.

Definition at line 461 of file sn65dsi86bridge.c.

References chip, DP_LANE_COUNT_MASK, DP_MAX_LANE_COUNT, DPCD_READ, i2c_write_field(), MIN, sn65dsi86_bridge_aux_request(), and SN_SSC_CONFIG_REG.

Referenced by sn65dsi86_bridge_configure().

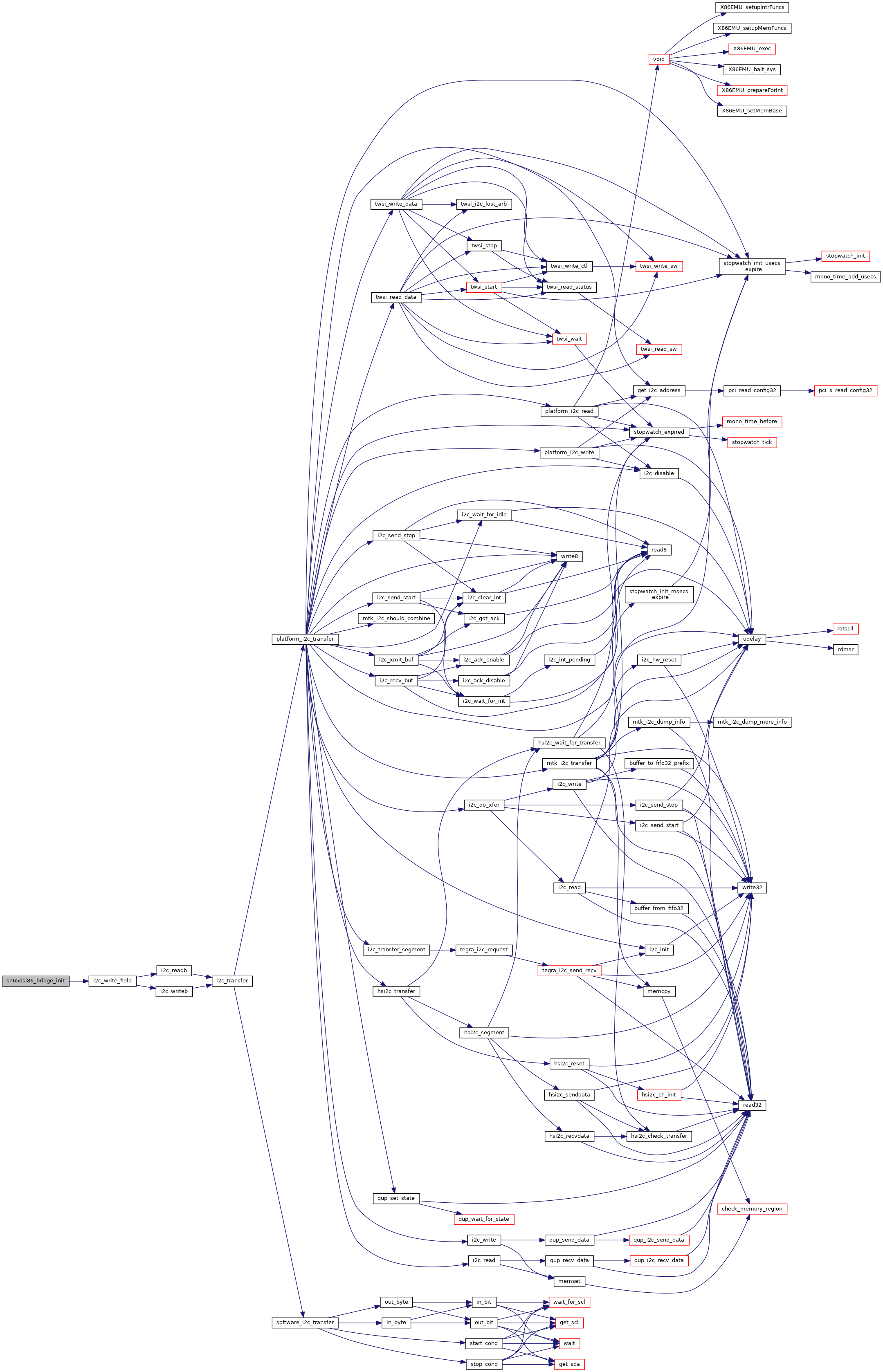

| void sn65dsi86_bridge_init | ( | uint8_t | bus, |

| uint8_t | chip, | ||

| enum dp_pll_clk_src | ref_clk | ||

| ) |

Definition at line 472 of file sn65dsi86bridge.c.

References chip, HPD_DISABLE, i2c_write_field(), SN_DPPLL_SRC_REG, and SN_HPD_DISABLE_REG.

Referenced by display_startup().

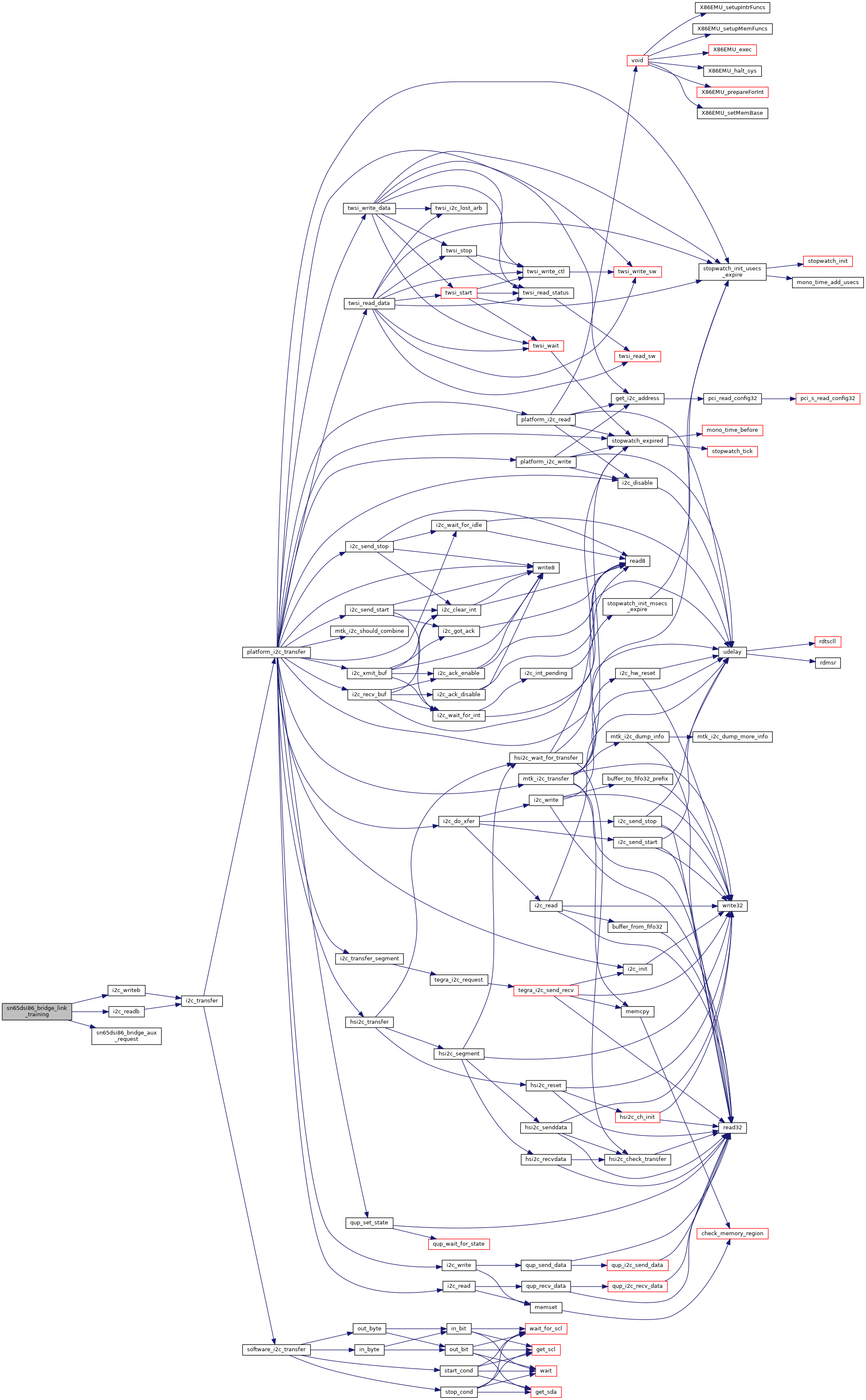

Definition at line 400 of file sn65dsi86bridge.c.

References BIOS_ERR, BIT, buf, chip, DP_BRIDGE_CONFIGURATION_SET, DPCD_WRITE, i2c_readb(), i2c_writeb(), MAIN_LINK_OFF, NORMAL_MODE, printk, SEMI_AUTO_LINK_TRAINING, sn65dsi86_bridge_aux_request(), SN_DPPLL_SRC_REG, SN_ML_TX_MODE_REG, SN_PLL_ENABLE_REG, and wait_ms.

Referenced by sn65dsi86_bridge_configure().

Definition at line 154 of file sn65dsi86bridge.c.

Referenced by display_startup().

|

static |

Definition at line 370 of file sn65dsi86bridge.c.

References BRIDGE_GETHIGHERBYTE, BRIDGE_GETLOWERBYTE, chip, edid_mode::ha, edid_mode::hbl, edid_mode::hso, edid_mode::hspw, i2c_writeb(), edid::mode, SN_CHA_ACTIVE_LINE_LENGTH_HIGH_REG, SN_CHA_ACTIVE_LINE_LENGTH_LOW_REG, SN_CHA_HORIZONTAL_BACK_PORCH_REG, SN_CHA_HORIZONTAL_FRONT_PORCH_REG, SN_CHA_HSYNC_PULSE_WIDTH_HIGH_REG, SN_CHA_HSYNC_PULSE_WIDTH_LOW_REG, SN_CHA_VERTICAL_BACK_PORCH_REG, SN_CHA_VERTICAL_DISPLAY_SIZE_HIGH_REG, SN_CHA_VERTICAL_DISPLAY_SIZE_LOW_REG, SN_CHA_VERTICAL_FRONT_PORCH_REG, SN_CHA_VSYNC_PULSE_WIDTH_HIGH_REG, SN_CHA_VSYNC_PULSE_WIDTH_LOW_REG, edid_mode::va, edid_mode::vbl, edid_mode::vso, and edid_mode::vspw.

Referenced by sn65dsi86_bridge_configure().

|

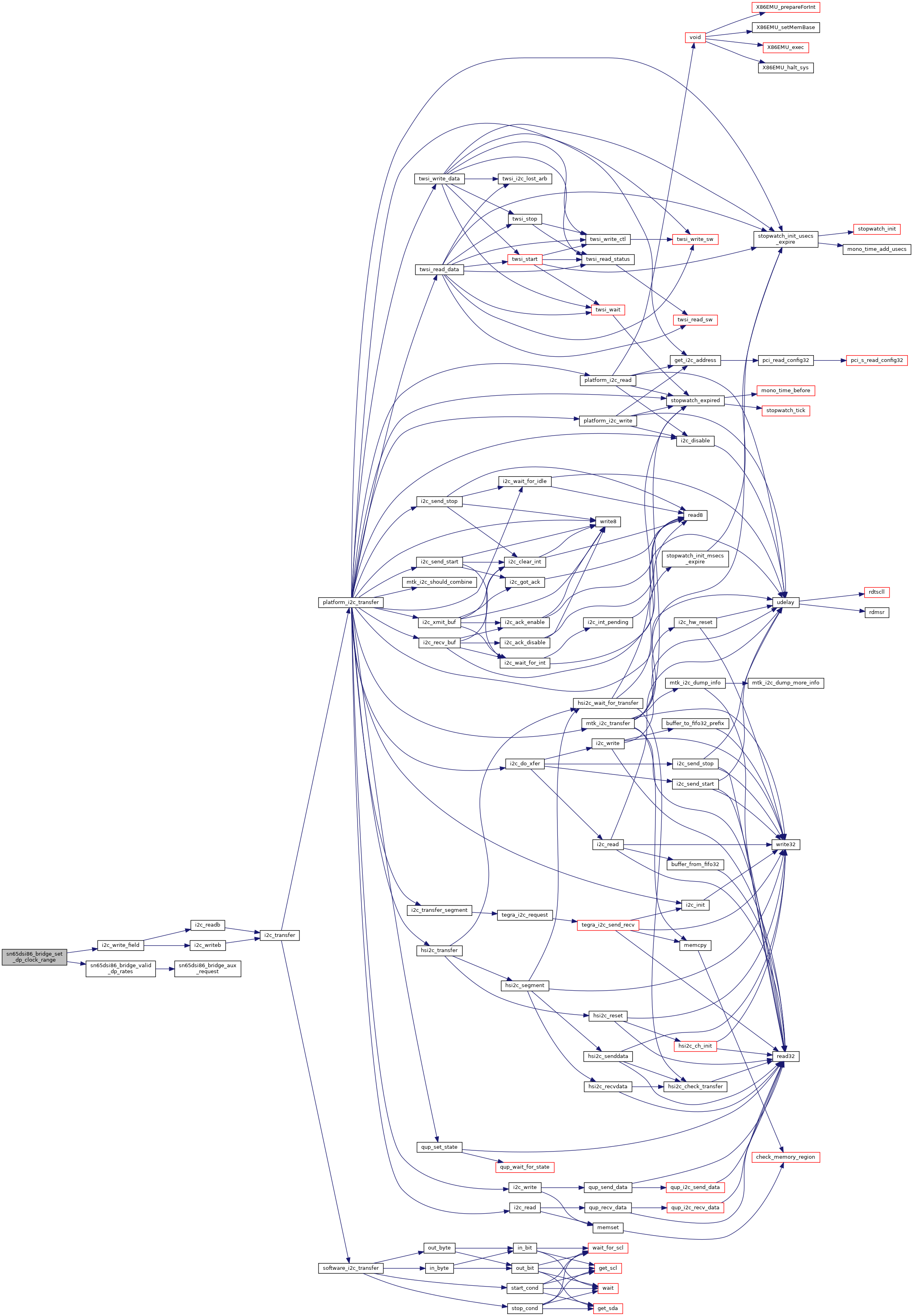

static |

Definition at line 337 of file sn65dsi86bridge.c.

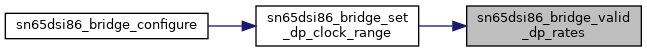

References ARRAY_SIZE, BIOS_ERR, chip, DIV_ROUND_UP, DP_CLK_FUDGE_DEN, DP_CLK_FUDGE_NUM, i2c_write_field(), KHz, edid::mode, edid_mode::pixel_clock, printk, sn65dsi86_bridge_dp_rate_lut, sn65dsi86_bridge_valid_dp_rates(), and SN_DATARATE_CONFIG_REG.

Referenced by sn65dsi86_bridge_configure().

|

static |

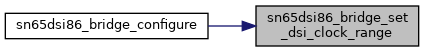

Definition at line 317 of file sn65dsi86bridge.c.

References chip, i2c_writeb(), KHz, MAX, MAX_DSI_CLK_FREQ_MHZ, MHz, MIN, MIN_DSI_CLK_FREQ_MHZ, edid::mode, edid_mode::pixel_clock, and SN_DSIA_CLK_FREQ_REG.

Referenced by sn65dsi86_bridge_configure().

Definition at line 259 of file sn65dsi86bridge.c.

References __fallthrough, ARRAY_SIZE, BIOS_ERR, chip, DP_BRIDGE_14, DP_BRIDGE_DPCD_REV, DP_LINK_BW_1_62, DP_LINK_BW_2_7, DP_LINK_BW_5_4, DP_MAX_LINK_RATE, DP_MAX_SUPPORTED_RATES, DP_SUPPORTED_LINK_RATES, DPCD_READ, KHz, MHz, printk, sn65dsi86_bridge_aux_request(), and sn65dsi86_bridge_dp_rate_lut.

Referenced by sn65dsi86_bridge_set_dp_clock_range().

|

static |

Definition at line 154 of file sn65dsi86bridge.c.

Referenced by sn65dsi86_bridge_set_dp_clock_range(), and sn65dsi86_bridge_valid_dp_rates().