|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

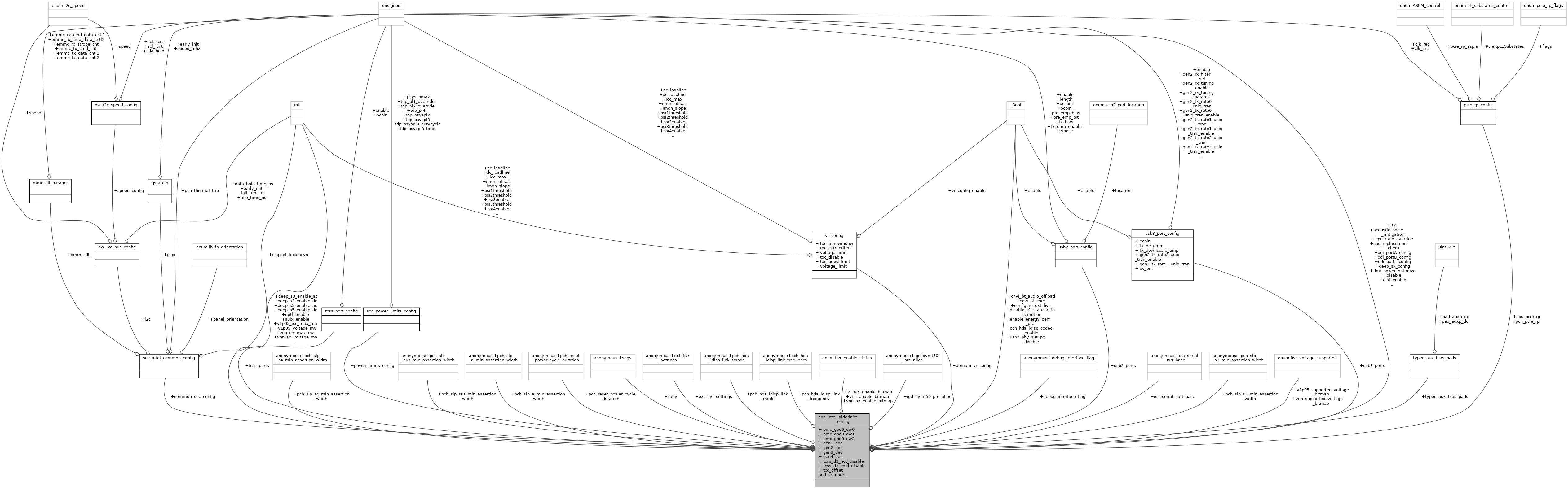

#include <chip.h>

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| uint8_t soc_intel_alderlake_config::acoustic_noise_mitigation |

| struct soc_intel_common_config soc_intel_alderlake_config::common_soc_config |

| struct pcie_rp_config soc_intel_alderlake_config::cpu_pcie_rp[CONFIG_MAX_CPU_ROOT_PORTS] |

| uint8_t soc_intel_alderlake_config::ddi_ports_config[DDI_PORT_COUNT] |

| enum { ... } soc_intel_alderlake_config::debug_interface_flag |

| bool soc_intel_alderlake_config::disable_c1_state_auto_demotion |

| uint8_t soc_intel_alderlake_config::dmi_power_optimize_disable |

| struct vr_config soc_intel_alderlake_config::domain_vr_config[NUM_VR_DOMAINS] |

| struct { ... } soc_intel_alderlake_config::ext_fivr_settings |

| uint8_t soc_intel_alderlake_config::fast_pkg_c_ramp_disable[NUM_VR_DOMAINS] |

| uint8_t soc_intel_alderlake_config::gpio_pm[TOTAL_GPIO_COMM] |

| enum { ... } soc_intel_alderlake_config::igd_dvmt50_pre_alloc |

| enum { ... } soc_intel_alderlake_config::isa_serial_uart_base |

| enum { ... } soc_intel_alderlake_config::pch_hda_idisp_link_frequency |

| enum { ... } soc_intel_alderlake_config::pch_hda_idisp_link_tmode |

| struct pcie_rp_config soc_intel_alderlake_config::pch_pcie_rp[CONFIG_MAX_PCH_ROOT_PORTS] |

| enum { ... } soc_intel_alderlake_config::pch_reset_power_cycle_duration |

| enum { ... } soc_intel_alderlake_config::pch_slp_a_min_assertion_width |

| enum { ... } soc_intel_alderlake_config::pch_slp_s3_min_assertion_width |

| enum { ... } soc_intel_alderlake_config::pch_slp_s4_min_assertion_width |

| enum { ... } soc_intel_alderlake_config::pch_slp_sus_min_assertion_width |

| uint8_t soc_intel_alderlake_config::pcie_clk_config_flag[CONFIG_MAX_PCIE_CLOCK_SRC] |

| struct soc_power_limits_config soc_intel_alderlake_config::power_limits_config[ADL_POWER_LIMITS_COUNT] |

| enum { ... } soc_intel_alderlake_config::sagv |

| uint8_t soc_intel_alderlake_config::sata_ports_enable_dito_config[8] |

| uint8_t soc_intel_alderlake_config::sata_pwr_optimize_disable |

| uint8_t soc_intel_alderlake_config::serial_io_gspi_cs_mode[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_alderlake_config::serial_io_gspi_cs_state[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_alderlake_config::serial_io_gspi_mode[CONFIG_SOC_INTEL_COMMON_BLOCK_GSPI_MAX] |

| uint8_t soc_intel_alderlake_config::serial_io_i2c_mode[CONFIG_SOC_INTEL_I2C_DEV_MAX] |

| uint8_t soc_intel_alderlake_config::serial_io_uart_mode[CONFIG_SOC_INTEL_UART_DEV_MAX] |

| uint8_t soc_intel_alderlake_config::slow_slew_rate[NUM_VR_DOMAINS] |

| struct tcss_port_config soc_intel_alderlake_config::tcss_ports[MAX_TYPE_C_PORTS] |

| struct typec_aux_bias_pads soc_intel_alderlake_config::typec_aux_bias_pads[MAX_TYPE_C_PORTS] |

| struct usb2_port_config soc_intel_alderlake_config::usb2_ports[16] |

| struct usb3_port_config soc_intel_alderlake_config::usb3_ports[10] |

| enum fivr_enable_states soc_intel_alderlake_config::v1p05_enable_bitmap |

| enum fivr_voltage_supported soc_intel_alderlake_config::v1p05_supported_voltage_bitmap |

| enum fivr_enable_states soc_intel_alderlake_config::vnn_enable_bitmap |

| enum fivr_voltage_supported soc_intel_alderlake_config::vnn_supported_voltage_bitmap |

| enum fivr_enable_states soc_intel_alderlake_config::vnn_sx_enable_bitmap |