|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

#include <raminit_common.h>

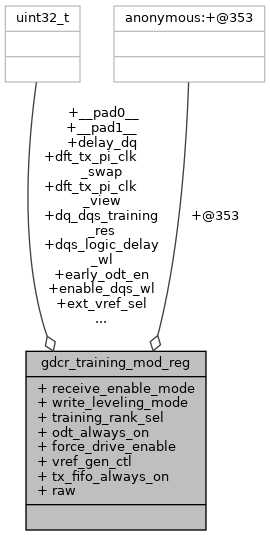

Data Fields | |

| struct { | |

| u32 receive_enable_mode: 1 | |

| u32 write_leveling_mode: 1 | |

| u32 training_rank_sel: 2 | |

| u32 enable_dqs_wl: 4 | |

| u32 dqs_logic_delay_wl: 1 | |

| u32 dq_dqs_training_res: 1 | |

| u32 __pad0__: 4 | |

| u32 delay_dq: 1 | |

| u32 odt_always_on: 1 | |

| u32 __pad1__: 4 | |

| u32 force_drive_enable: 1 | |

| u32 dft_tx_pi_clk_view: 1 | |

| u32 dft_tx_pi_clk_swap: 1 | |

| u32 early_odt_en: 1 | |

| u32 vref_gen_ctl: 6 | |

| u32 ext_vref_sel: 1 | |

| u32 tx_fifo_always_on: 1 | |

| }; | |

| u32 | raw |

Definition at line 136 of file raminit_common.h.

| struct { ... } |

| u32 gdcr_training_mod_reg::__pad0__ |

Definition at line 144 of file raminit_common.h.

| u32 gdcr_training_mod_reg::__pad1__ |

Definition at line 147 of file raminit_common.h.

| u32 gdcr_training_mod_reg::delay_dq |

Definition at line 145 of file raminit_common.h.

| u32 gdcr_training_mod_reg::dft_tx_pi_clk_swap |

Definition at line 150 of file raminit_common.h.

| u32 gdcr_training_mod_reg::dft_tx_pi_clk_view |

Definition at line 149 of file raminit_common.h.

| u32 gdcr_training_mod_reg::dq_dqs_training_res |

Definition at line 143 of file raminit_common.h.

Referenced by train_write_flyby().

| u32 gdcr_training_mod_reg::dqs_logic_delay_wl |

Definition at line 142 of file raminit_common.h.

| u32 gdcr_training_mod_reg::early_odt_en |

Definition at line 151 of file raminit_common.h.

| u32 gdcr_training_mod_reg::enable_dqs_wl |

Definition at line 141 of file raminit_common.h.

| u32 gdcr_training_mod_reg::ext_vref_sel |

Definition at line 153 of file raminit_common.h.

| u32 gdcr_training_mod_reg::force_drive_enable |

Definition at line 148 of file raminit_common.h.

| u32 gdcr_training_mod_reg::odt_always_on |

Definition at line 146 of file raminit_common.h.

| u32 gdcr_training_mod_reg::raw |

Definition at line 156 of file raminit_common.h.

Referenced by find_agrsv_read_margin(), jedec_write_leveling(), receive_enable_calibration(), train_write_flyby(), and write_level_rank().

| u32 gdcr_training_mod_reg::receive_enable_mode |

Definition at line 138 of file raminit_common.h.

Referenced by receive_enable_calibration().

| u32 gdcr_training_mod_reg::training_rank_sel |

Definition at line 140 of file raminit_common.h.

| u32 gdcr_training_mod_reg::tx_fifo_always_on |

Definition at line 154 of file raminit_common.h.

| u32 gdcr_training_mod_reg::vref_gen_ctl |

Definition at line 152 of file raminit_common.h.

Referenced by find_agrsv_read_margin().

| u32 gdcr_training_mod_reg::write_leveling_mode |

Definition at line 139 of file raminit_common.h.

Referenced by jedec_write_leveling(), and write_level_rank().