|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

Go to the source code of this file.

Macros | |

| #define | NB_IOAPIC_INDEX 0xf8 |

| #define | NB_IOAPIC_DATA 0xfc |

| #define | NB_IOAPIC_FEATURE_CTRL 0x00 |

| #define | NB_IOAPIC_ADDRESS_LOW 0x01 |

| #define | NB_IOAPIC_ADDRESS_HIGH 0x02 |

| #define | NB_IOAPIC_GBIF_IRR 0x0f |

| #define | NB_IOAPIC_BR0_IRR 0x10 |

| #define | NB_IOAPIC_BR1_IRR 0x11 |

| #define | NB_IOAPIC_BR2_IRR 0x12 |

| #define | NB_IOAPIC_BR3_IRR 0x13 |

| #define | NB_IOAPIC_BR4_IRR 0x14 |

| #define | NB_IOAPIC_APG_IRR 0x2f |

| #define | NB_IOAPIC_SPG_IRR 0x30 |

| #define | NB_IOAPIC_SER_IRQ_IRR 0x31 |

| #define | NB_IOAPIC_SCRATCH0 0x3e |

| #define | NB_IOAPIC_SCRATCH1 0x3f |

| #define | HDA_DEV_CTRL_STATUS 0x60 |

| #define | HDA_NO_SNOOP_EN BIT(11) |

| #define | D18F0_NODE_ID 0x60 |

| #define | D18F0_CPU_CNT 0x62 /* BKDG defines as a field in DWORD 0x60 */ |

| #define | CPU_CNT_MASK 0x1f /* CpuCnt + 1 = no. CPUs */ |

| #define | HT_INIT_CONTROL 0x6c |

| #define | HTIC_BIOSR_DETECT ((1 << 5) | (1 << 9) | (1 << 10)) |

| #define | HTIC_COLD_RST_DET BIT(4) |

| #define | D18F1_MMIO_BASE0_LO 0x80 |

| #define | MMIO_WE (1 << 1) |

| #define | MMIO_RE (1 << 0) |

| #define | D18F1_MMIO_LIMIT0_LO 0x84 |

| #define | MMIO_NP (1 << 7) |

| #define | D18F1_IO_BASE0_LO 0xc0 |

| #define | D18F1_IO_BASE1_LO 0xc8 |

| #define | D18F1_IO_BASE2_LO 0xd0 |

| #define | D18F1_IO_BASE3_LO 0xd8 |

| #define | D18F1_MMIO_BASE7_LO 0xb8 |

| #define | D18F1_MMIO_BASELIM0_HI 0x180 |

| #define | D18F1_MMIO_BASE8_LO 0x1a0 |

| #define | D18F1_MMIO_LIMIT8_LO 0x1a4 |

| #define | D18F1_MMIO_BASE11_LO 0x1b8 |

| #define | D18F1_MMIO_BASELIM8_HI 0x1c0 |

| #define | NB_MMIO_BASE_LO(reg) |

| #define | NB_MMIO_LIMIT_LO(reg) (NB_MMIO_BASE_LO(reg) + sizeof(uint32_t)) |

| #define | NB_MMIO_BASELIM_HI(reg) |

| #define | D18F1_IO_BASE0 0xc0 |

| #define | IO_WE (1 << 1) |

| #define | IO_RE (1 << 0) |

| #define | D18F1_IO_LIMIT0 0xc4 |

| #define | NB_IO_BASE(reg) ((reg) * 2 * sizeof(uint32_t) + D18F1_IO_BASE0) |

| #define | NB_IO_LIMIT(reg) (NB_IO_BASE(reg) + sizeof(uint32_t)) |

| #define | D18F1_DRAM_HOLE 0xf0 |

| #define | DRAM_HOIST_VALID (1 << 1) |

| #define | DRAM_HOLE_VALID (1 << 0) |

| #define | D18F1_VGAEN 0xf4 |

| #define | VGA_ADDR_ENABLE (1 << 0) |

| #define | NB_CAPABILITIES2 0x84 |

| #define | CMP_CAP_MASK 0xff |

Functions | |

| void | domain_enable_resources (struct device *dev) |

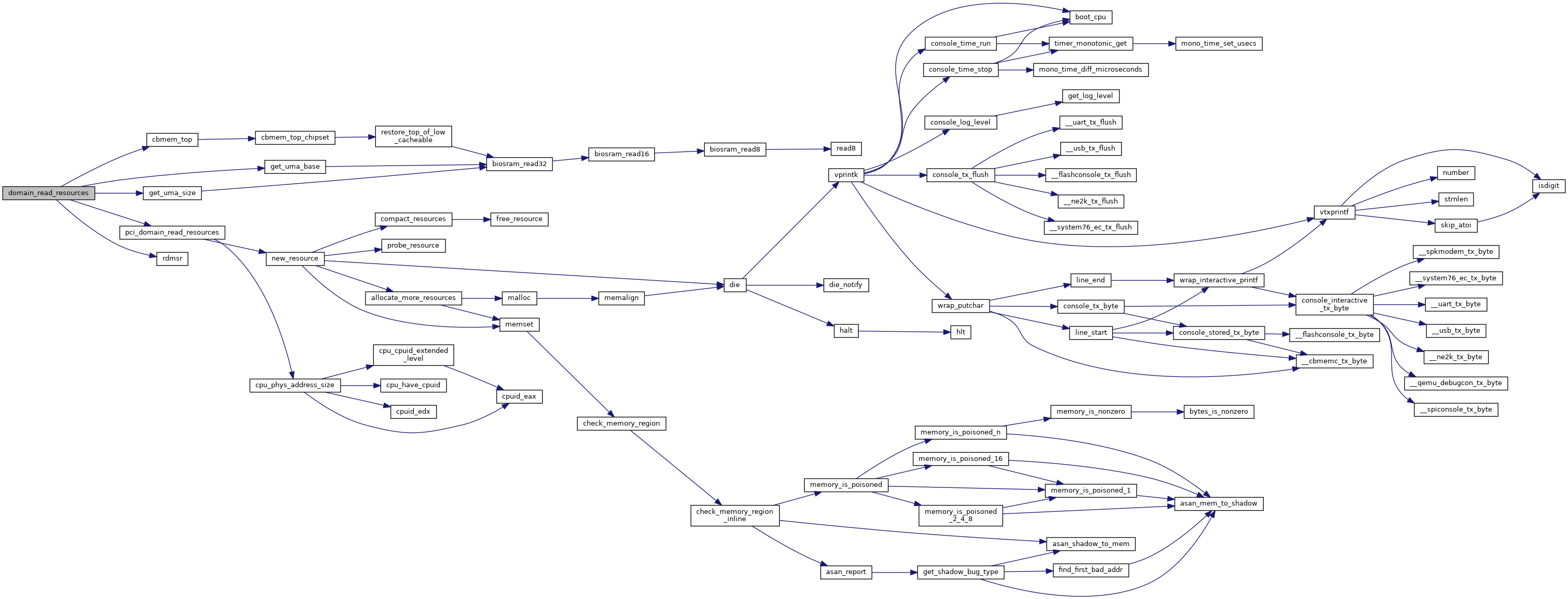

| void | domain_read_resources (struct device *dev) |

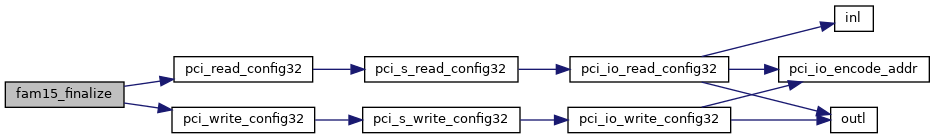

| void | fam15_finalize (void *chip_info) |

| #define CMP_CAP_MASK 0xff |

Definition at line 84 of file northbridge.h.

| #define CPU_CNT_MASK 0x1f /* CpuCnt + 1 = no. CPUs */ |

Definition at line 36 of file northbridge.h.

| #define D18F0_CPU_CNT 0x62 /* BKDG defines as a field in DWORD 0x60 */ |

Definition at line 35 of file northbridge.h.

| #define D18F0_NODE_ID 0x60 |

Definition at line 34 of file northbridge.h.

| #define D18F1_DRAM_HOLE 0xf0 |

Definition at line 76 of file northbridge.h.

| #define D18F1_IO_BASE0 0xc0 |

Definition at line 69 of file northbridge.h.

| #define D18F1_IO_BASE0_LO 0xc0 |

Definition at line 49 of file northbridge.h.

| #define D18F1_IO_BASE1_LO 0xc8 |

Definition at line 50 of file northbridge.h.

| #define D18F1_IO_BASE2_LO 0xd0 |

Definition at line 51 of file northbridge.h.

| #define D18F1_IO_BASE3_LO 0xd8 |

Definition at line 52 of file northbridge.h.

| #define D18F1_IO_LIMIT0 0xc4 |

Definition at line 72 of file northbridge.h.

| #define D18F1_MMIO_BASE0_LO 0x80 |

Definition at line 44 of file northbridge.h.

| #define D18F1_MMIO_BASE11_LO 0x1b8 |

Definition at line 57 of file northbridge.h.

| #define D18F1_MMIO_BASE7_LO 0xb8 |

Definition at line 53 of file northbridge.h.

| #define D18F1_MMIO_BASE8_LO 0x1a0 |

Definition at line 55 of file northbridge.h.

| #define D18F1_MMIO_BASELIM0_HI 0x180 |

Definition at line 54 of file northbridge.h.

| #define D18F1_MMIO_BASELIM8_HI 0x1c0 |

Definition at line 58 of file northbridge.h.

| #define D18F1_MMIO_LIMIT0_LO 0x84 |

Definition at line 47 of file northbridge.h.

| #define D18F1_MMIO_LIMIT8_LO 0x1a4 |

Definition at line 56 of file northbridge.h.

| #define D18F1_VGAEN 0xf4 |

Definition at line 79 of file northbridge.h.

| #define DRAM_HOIST_VALID (1 << 1) |

Definition at line 77 of file northbridge.h.

| #define DRAM_HOLE_VALID (1 << 0) |

Definition at line 78 of file northbridge.h.

| #define HDA_DEV_CTRL_STATUS 0x60 |

Definition at line 30 of file northbridge.h.

| #define HDA_NO_SNOOP_EN BIT(11) |

Definition at line 31 of file northbridge.h.

| #define HT_INIT_CONTROL 0x6c |

Definition at line 37 of file northbridge.h.

| #define HTIC_BIOSR_DETECT ((1 << 5) | (1 << 9) | (1 << 10)) |

Definition at line 38 of file northbridge.h.

| #define HTIC_COLD_RST_DET BIT(4) |

Definition at line 39 of file northbridge.h.

| #define IO_RE (1 << 0) |

Definition at line 71 of file northbridge.h.

| #define IO_WE (1 << 1) |

Definition at line 70 of file northbridge.h.

| #define MMIO_NP (1 << 7) |

Definition at line 48 of file northbridge.h.

| #define MMIO_RE (1 << 0) |

Definition at line 46 of file northbridge.h.

| #define MMIO_WE (1 << 1) |

Definition at line 45 of file northbridge.h.

| #define NB_CAPABILITIES2 0x84 |

Definition at line 83 of file northbridge.h.

| #define NB_IO_BASE | ( | reg | ) | ((reg) * 2 * sizeof(uint32_t) + D18F1_IO_BASE0) |

Definition at line 73 of file northbridge.h.

| #define NB_IO_LIMIT | ( | reg | ) | (NB_IO_BASE(reg) + sizeof(uint32_t)) |

Definition at line 74 of file northbridge.h.

| #define NB_IOAPIC_ADDRESS_HIGH 0x02 |

Definition at line 16 of file northbridge.h.

| #define NB_IOAPIC_ADDRESS_LOW 0x01 |

Definition at line 15 of file northbridge.h.

| #define NB_IOAPIC_APG_IRR 0x2f |

Definition at line 23 of file northbridge.h.

| #define NB_IOAPIC_BR0_IRR 0x10 |

Definition at line 18 of file northbridge.h.

| #define NB_IOAPIC_BR1_IRR 0x11 |

Definition at line 19 of file northbridge.h.

| #define NB_IOAPIC_BR2_IRR 0x12 |

Definition at line 20 of file northbridge.h.

| #define NB_IOAPIC_BR3_IRR 0x13 |

Definition at line 21 of file northbridge.h.

| #define NB_IOAPIC_BR4_IRR 0x14 |

Definition at line 22 of file northbridge.h.

| #define NB_IOAPIC_DATA 0xfc |

Definition at line 13 of file northbridge.h.

| #define NB_IOAPIC_FEATURE_CTRL 0x00 |

Definition at line 14 of file northbridge.h.

| #define NB_IOAPIC_GBIF_IRR 0x0f |

Definition at line 17 of file northbridge.h.

| #define NB_IOAPIC_INDEX 0xf8 |

Definition at line 12 of file northbridge.h.

| #define NB_IOAPIC_SCRATCH0 0x3e |

Definition at line 26 of file northbridge.h.

| #define NB_IOAPIC_SCRATCH1 0x3f |

Definition at line 27 of file northbridge.h.

| #define NB_IOAPIC_SER_IRQ_IRR 0x31 |

Definition at line 25 of file northbridge.h.

| #define NB_IOAPIC_SPG_IRR 0x30 |

Definition at line 24 of file northbridge.h.

| #define NB_MMIO_BASE_LO | ( | reg | ) |

Definition at line 59 of file northbridge.h.

| #define NB_MMIO_BASELIM_HI | ( | reg | ) |

Definition at line 64 of file northbridge.h.

| #define NB_MMIO_LIMIT_LO | ( | reg | ) | (NB_MMIO_BASE_LO(reg) + sizeof(uint32_t)) |

Definition at line 63 of file northbridge.h.

| #define VGA_ADDR_ENABLE (1 << 0) |

Definition at line 80 of file northbridge.h.

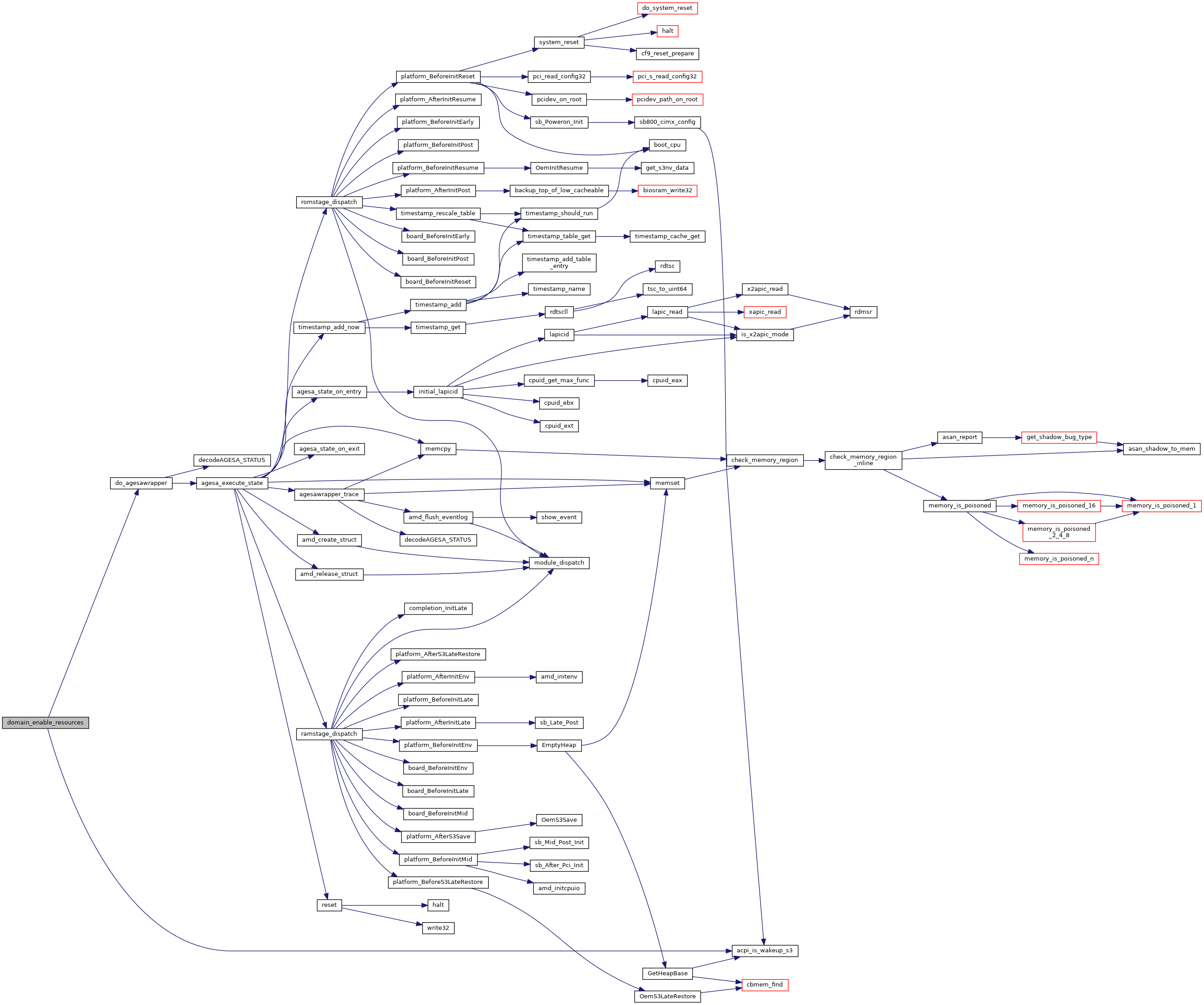

Definition at line 379 of file northbridge.c.

References acpi_is_wakeup_s3(), and do_agesawrapper().

Definition at line 386 of file northbridge.c.

References cbmem_top(), get_uma_base(), get_uma_size(), GiB, msr_struct::hi, KiB, msr_struct::lo, MiB, mmio_resource, pci_domain_read_resources(), ram_resource, rdmsr(), reserved_ram_resource, TOP_MEM, and TOP_MEM2.

Definition at line 365 of file northbridge.c.

References HDA_DEV_CTRL_STATUS, HDA_NO_SNOOP_EN, NB_IOAPIC_DATA, NB_IOAPIC_INDEX, pci_read_config32(), pci_write_config32(), SOC_GNB_DEV, SOC_HDA0_DEV, and value.