|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

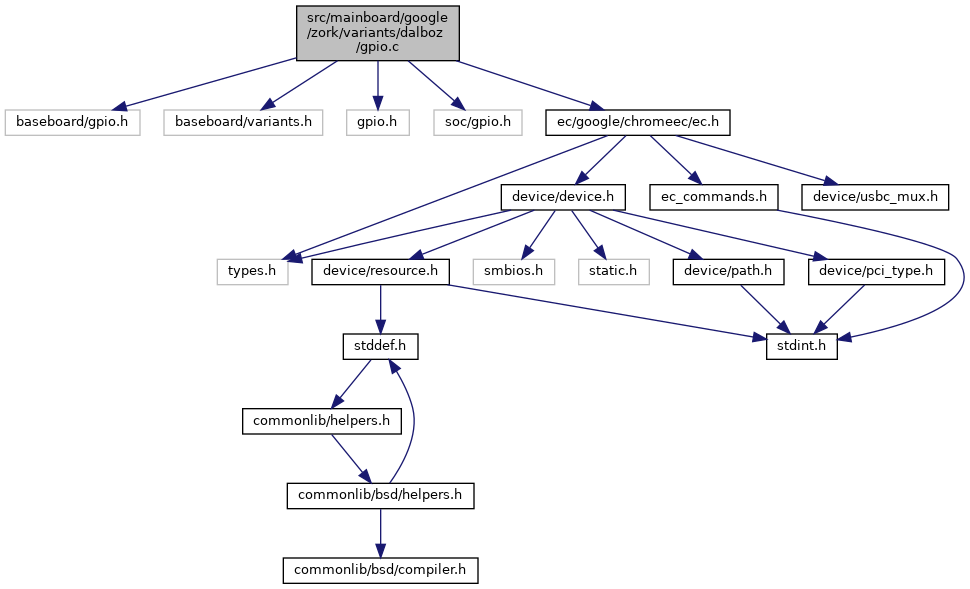

#include <baseboard/gpio.h>#include <baseboard/variants.h>#include <gpio.h>#include <soc/gpio.h>#include <ec/google/chromeec/ec.h>

Go to the source code of this file.

Functions | |

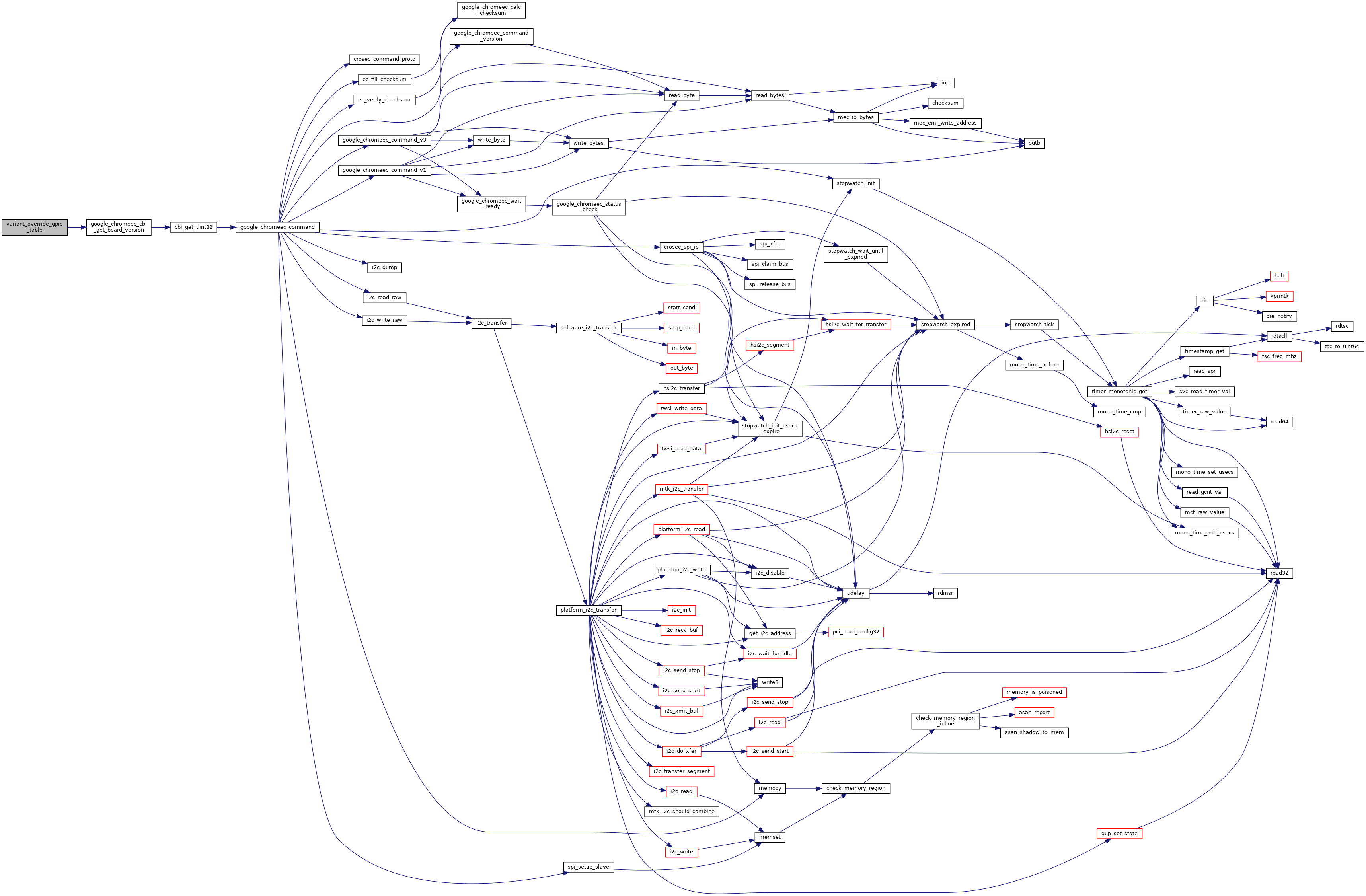

| const struct soc_amd_gpio * | variant_override_gpio_table (size_t *size) |

Variables | |

| static const struct soc_amd_gpio | bid_1_gpio_set_stage_ram [] |

| static const struct soc_amd_gpio | bid_2_gpio_set_stage_ram [] |

| const struct soc_amd_gpio* variant_override_gpio_table | ( | size_t * | size | ) |

Definition at line 40 of file gpio.c.

References ARRAY_SIZE, bid_1_gpio_set_stage_ram, bid_2_gpio_set_stage_ram, google_chromeec_cbi_get_board_version(), and NULL.

|

static |

Definition at line 1 of file gpio.c.

Referenced by variant_override_gpio_table().