|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

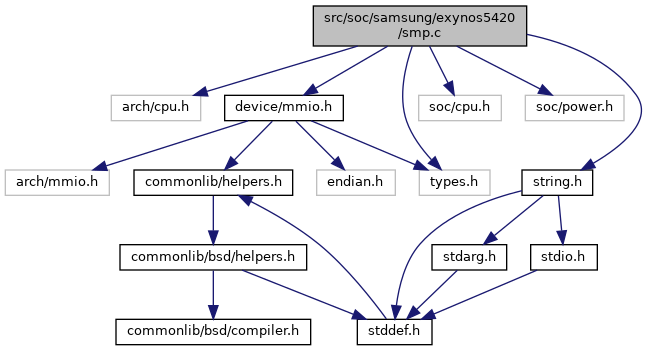

#include <arch/cpu.h>#include <device/mmio.h>#include <soc/cpu.h>#include <soc/power.h>#include <string.h>#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | exynos5420_cpu_states |

Macros | |

| #define | ACTLR_SMP (1 << 6) |

| #define | L2CTLR_ECC_PARITY (1 << 21) |

| #define | L2CTLR_DATA_RAM_LATENCY_MASK (7 << 0) |

| #define | L2CTLR_TAG_RAM_LATENCY_MASK (7 << 6) |

| #define | L2CTLR_DATA_RAM_LATENCY_CYCLES_3 (2 << 0) |

| #define | L2CTLR_TAG_RAM_LATENCY_CYCLES_3 (2 << 6) |

| #define | L2ACTLR_DISABLE_CLEAN_EVICT_PUSH_EXTERNAL (1 << 3) |

| #define | L2ACTLR_ENABLE_HAZARD_DETECT_TIMEOUT (1 << 7) |

| #define | L2ACTLR_FORCE_L2_LOGIC_CLOCK_ENABLE_ACTIVE (1 << 27) |

| #define | PART_NUMBER_CORTEX_A15 (0xc0f) |

| #define | CORE_STATE_RESET (1 << 0) |

| #define | CORE_STATE_SECONDARY_RESET (1 << 1) |

| #define | CORE_STATE_SWITCH_CLUSTER (1 << 4) |

| #define | CORE_RESET_INIT_ADDRESS ((void *)0x00000000) |

| #define | VECTOR_CORE_SEV_HANDLER ((void *)(intptr_t)0x02020004) |

| #define | VECTOR_LOW_POWER_FLAG ((void *)(intptr_t)0x02020028) |

| #define | VECTOR_LOW_POWER_ADDRESS ((void *)(intptr_t)0x0202002C) |

Functions | |

| static void | jump_bx (void *address) |

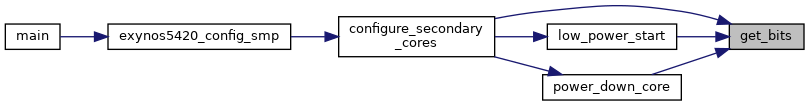

| static uint32_t | get_bits (uint32_t value, uint32_t start, uint32_t len) |

| static void | wait_and_jump (volatile uint32_t *reference) |

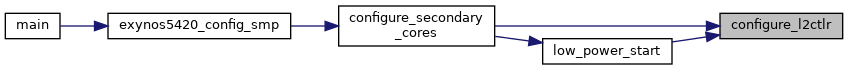

| static void | configure_l2ctlr (void) |

| static void | configure_l2actlr (void) |

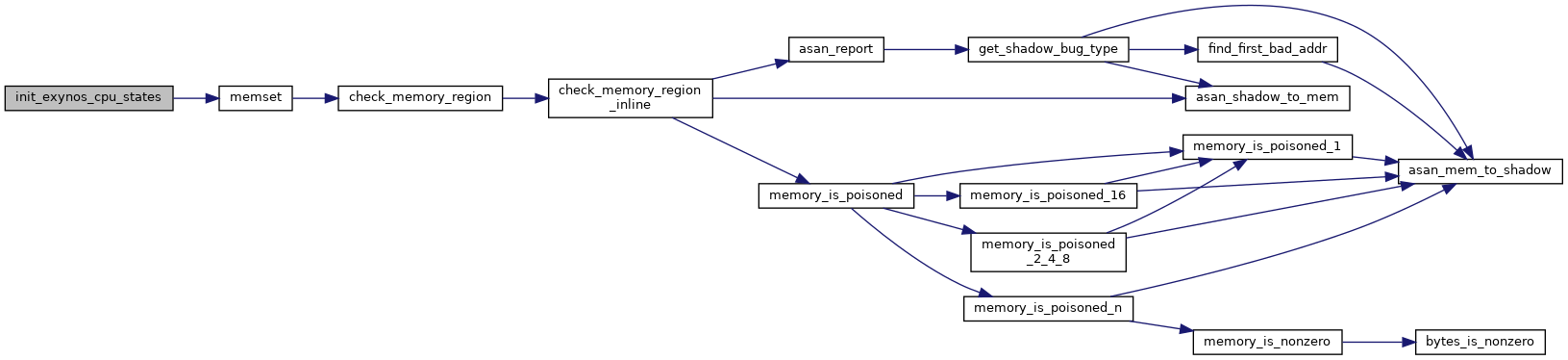

| static void | init_exynos_cpu_states (void) |

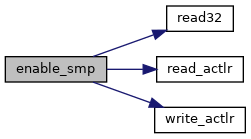

| static void | enable_smp (void) |

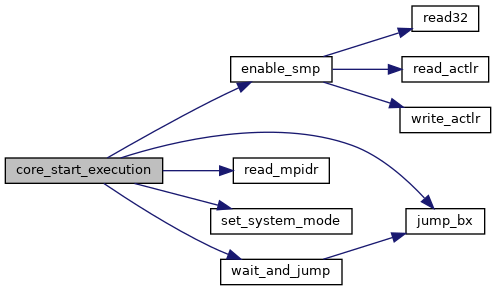

| static void | core_start_execution (void) |

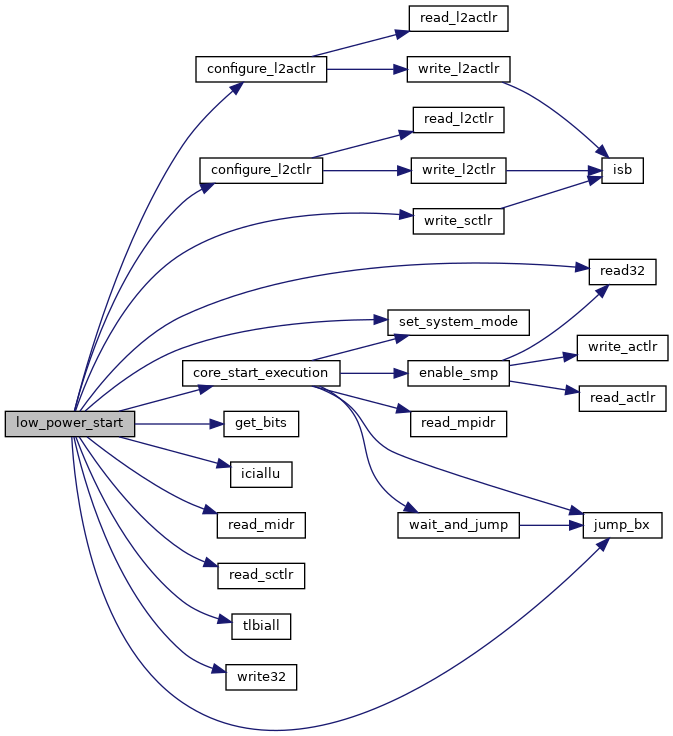

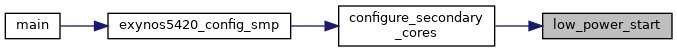

| static void | low_power_start (void) |

| static void | power_down_core (void) |

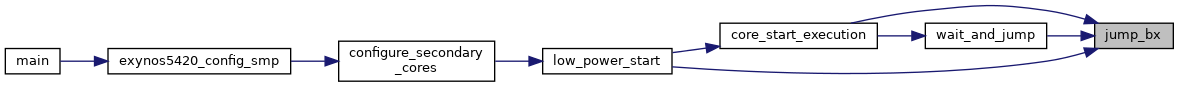

| static void | configure_secondary_cores (void) |

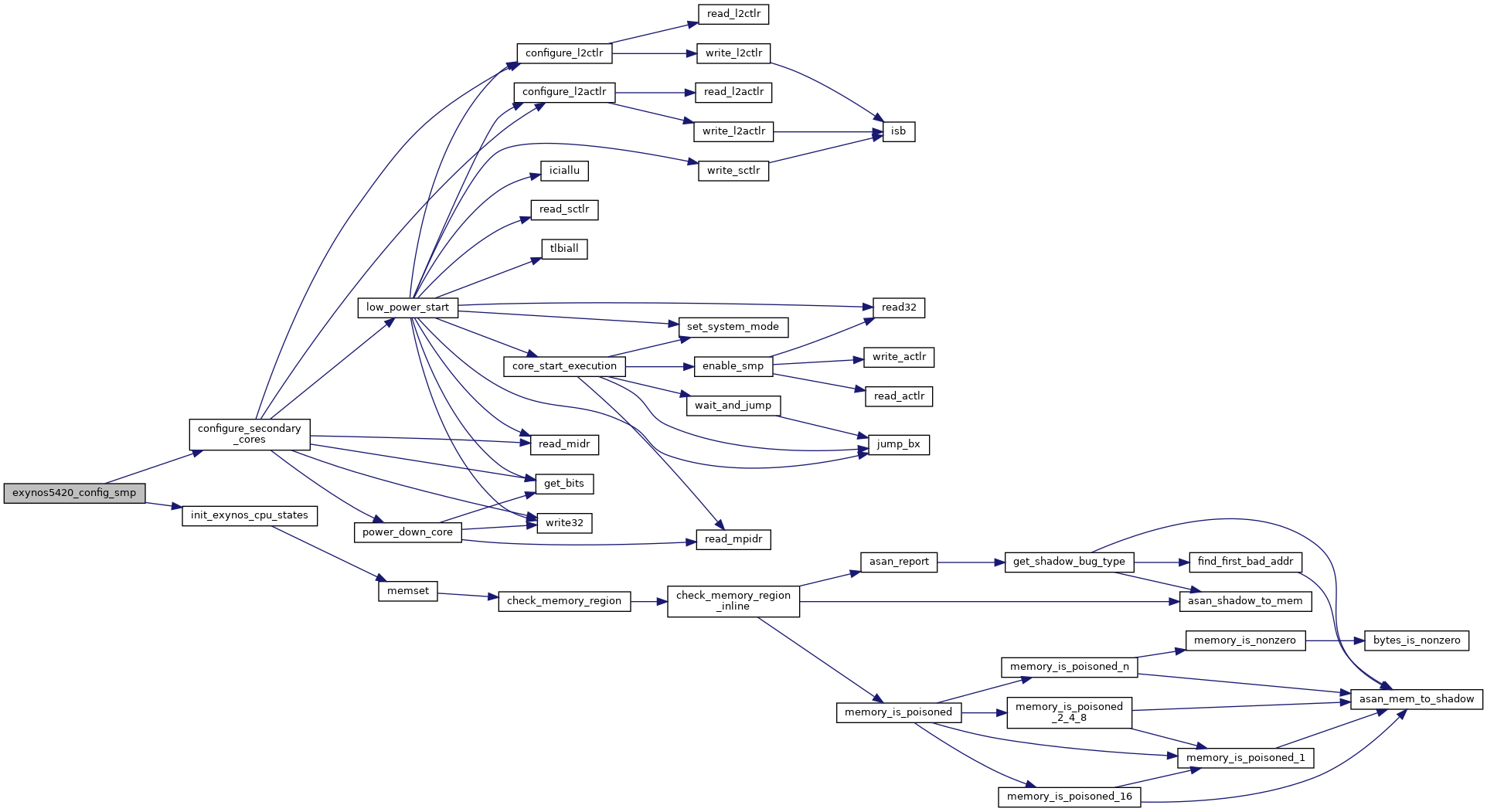

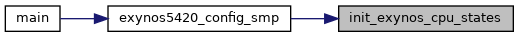

| void | exynos5420_config_smp (void) |

Variables | |

| volatile struct exynos5420_cpu_states * | exynos_cpu_states = (volatile struct exynos5420_cpu_states*)0x02073000 |

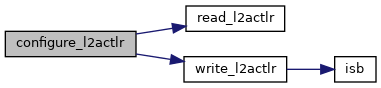

Definition at line 102 of file smp.c.

References L2ACTLR_DISABLE_CLEAN_EVICT_PUSH_EXTERNAL, L2ACTLR_ENABLE_HAZARD_DETECT_TIMEOUT, L2ACTLR_FORCE_L2_LOGIC_CLOCK_ENABLE_ACTIVE, read_l2actlr(), val, and write_l2actlr().

Referenced by configure_secondary_cores(), and low_power_start().

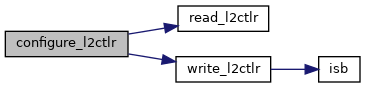

Definition at line 90 of file smp.c.

References L2CTLR_DATA_RAM_LATENCY_CYCLES_3, L2CTLR_DATA_RAM_LATENCY_MASK, L2CTLR_ECC_PARITY, L2CTLR_TAG_RAM_LATENCY_CYCLES_3, L2CTLR_TAG_RAM_LATENCY_MASK, read_l2ctlr(), val, and write_l2ctlr().

Referenced by configure_secondary_cores(), and low_power_start().

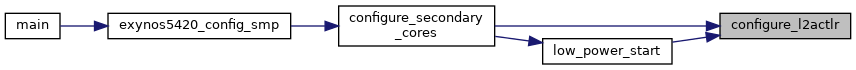

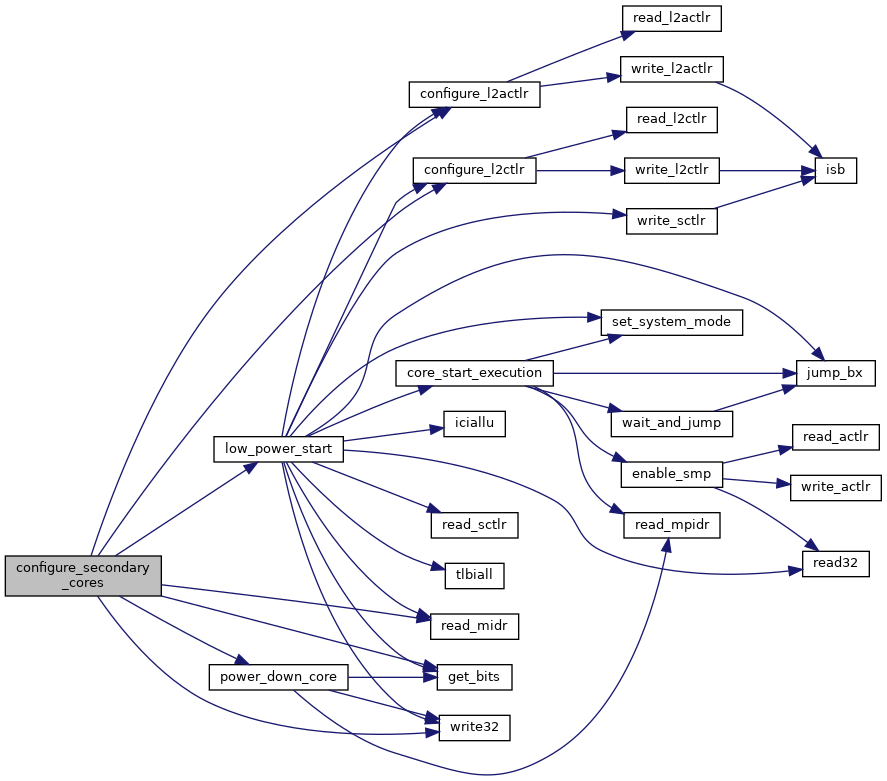

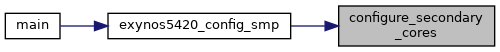

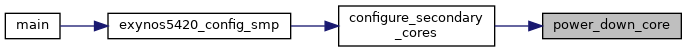

Definition at line 251 of file smp.c.

References configure_l2actlr(), configure_l2ctlr(), dsb, exynos_cpu_states, exynos_power, get_bits(), exynos5420_cpu_states::hotplug_address, low_power_start(), PART_NUMBER_CORTEX_A15, power_down_core(), read_midr(), RST_FLAG_VAL, sev, exynos5_power::spare0, VECTOR_CORE_SEV_HANDLER, VECTOR_LOW_POWER_ADDRESS, VECTOR_LOW_POWER_FLAG, and write32().

Referenced by exynos5420_config_smp().

Definition at line 146 of file smp.c.

References CORE_STATE_RESET, CORE_STATE_SWITCH_CLUSTER, cpu_id, exynos5420_cpu_states::cpu_states, enable_smp(), exynos_cpu_states, exynos_power, exynos5420_cpu_states::hotplug_address, exynos5_power::inform0, exynos5_power::inform1, jump_bx(), read_mpidr(), set_system_mode(), exynos5420_cpu_states::switch_address, and wait_and_jump().

Referenced by low_power_start().

Definition at line 127 of file smp.c.

References ACTLR_SMP, dsb, exynos_power, exynos5_power::inform0, isb, read32(), read_actlr(), val, and write_actlr().

Referenced by core_start_execution().

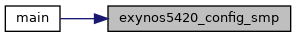

Definition at line 282 of file smp.c.

References configure_secondary_cores(), and init_exynos_cpu_states().

Referenced by main().

Definition at line 74 of file smp.c.

References value.

Referenced by configure_secondary_cores(), low_power_start(), and power_down_core().

Definition at line 114 of file smp.c.

References CORE_STATE_RESET, CORE_STATE_SECONDARY_RESET, exynos5420_cpu_states::cpu_states, exynos_cpu_states, and memset().

Referenced by exynos5420_config_smp().

Definition at line 67 of file smp.c.

References address.

Referenced by core_start_execution(), low_power_start(), and wait_and_jump().

Definition at line 177 of file smp.c.

References configure_l2actlr(), configure_l2ctlr(), CORE_RESET_INIT_ADDRESS, core_start_execution(), dsb, exynos_power, get_bits(), iciallu(), jump_bx(), PART_NUMBER_CORTEX_A15, read32(), read_midr(), read_sctlr(), RST_FLAG_VAL, SCTLR_A, SCTLR_C, SCTLR_I, SCTLR_M, SCTLR_V, SCTLR_Z, set_system_mode(), sev, exynos5_power::spare0, tlbiall(), VECTOR_CORE_SEV_HANDLER, VECTOR_LOW_POWER_FLAG, wfi, write32(), and write_sctlr().

Referenced by configure_secondary_cores().

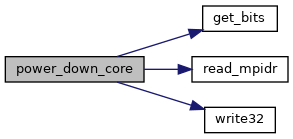

Definition at line 229 of file smp.c.

References exynos5_power::arm_core, exynos5_power::config, exynos_power, get_bits(), read_mpidr(), wfi, and write32().

Referenced by configure_secondary_cores().

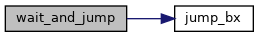

Definition at line 81 of file smp.c.

References jump_bx(), and wfe.

Referenced by core_start_execution().

| volatile struct exynos5420_cpu_states * exynos_cpu_states = (volatile struct exynos5420_cpu_states*)0x02073000 |

Referenced by configure_secondary_cores(), core_start_execution(), and init_exynos_cpu_states().