|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

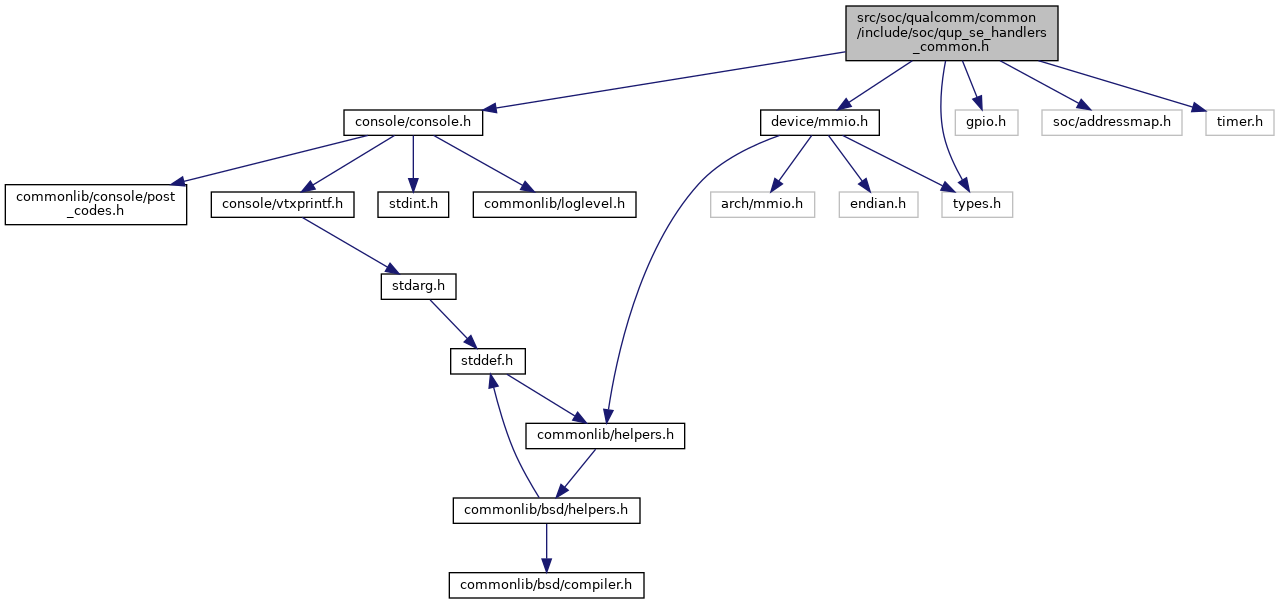

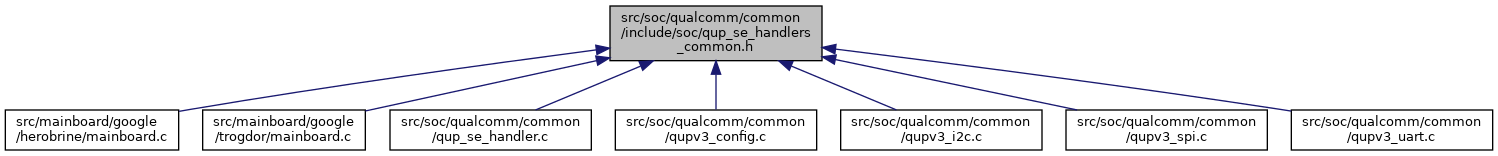

#include <console/console.h>#include <device/mmio.h>#include <gpio.h>#include <soc/addressmap.h>#include <timer.h>#include <types.h>

Go to the source code of this file.

Data Structures | |

| struct | qup_regs |

| struct | gsi_regs |

Enumerations | |

| enum | se_protocol { SE_PROTOCOL_SPI = 1 , SE_PROTOCOL_UART = 2 , SE_PROTOCOL_I2C = 3 , SE_PROTOCOL_I3C = 4 , SE_PROTOCOL_MAX = 5 } |

| enum | se_mode { NONE , GSI , FIFO , CPU_DMA , MIXED } |

Functions | |

| check_member (qup_regs, geni_clk_sel, 0x7C) | |

| check_member (qup_regs, geni_cfg_reg108, 0x2B0) | |

| check_member (qup_regs, geni_dma_mode_en, 0x258) | |

| check_member (qup_regs, geni_i3c_ibi_rd_data, 0xA84) | |

| check_member (qup_regs, dma_test_bus_ctrl, 0xE44) | |

| check_member (qup_regs, se_geni_cfg_ramn, 0x1010) | |

| check_member (qup_regs, se_geni_fw_multilock_sp, 0x2014) | |

| check_member (gsi_regs, gsi_manager_mcs_code_ver, 0x8) | |

| check_member (gsi_regs, gsi_zeros, 0x10) | |

| check_member (gsi_regs, gsi_periph_base_lsb, 0x18) | |

| check_member (gsi_regs, gsi_cgc_ctrl, 0x60) | |

| check_member (gsi_regs, ee_n_gsi_ee_generic_cmd, 0xF018) | |

| check_member (gsi_regs, gsi_ee_n_scratch_0_addr, 0xF400) | |

| check_member (gsi_regs, gsi_ee_n_scratch_1_addr, 0xF404) | |

| check_member (gsi_regs, gsi_inst_ramn, 0x4C000) | |

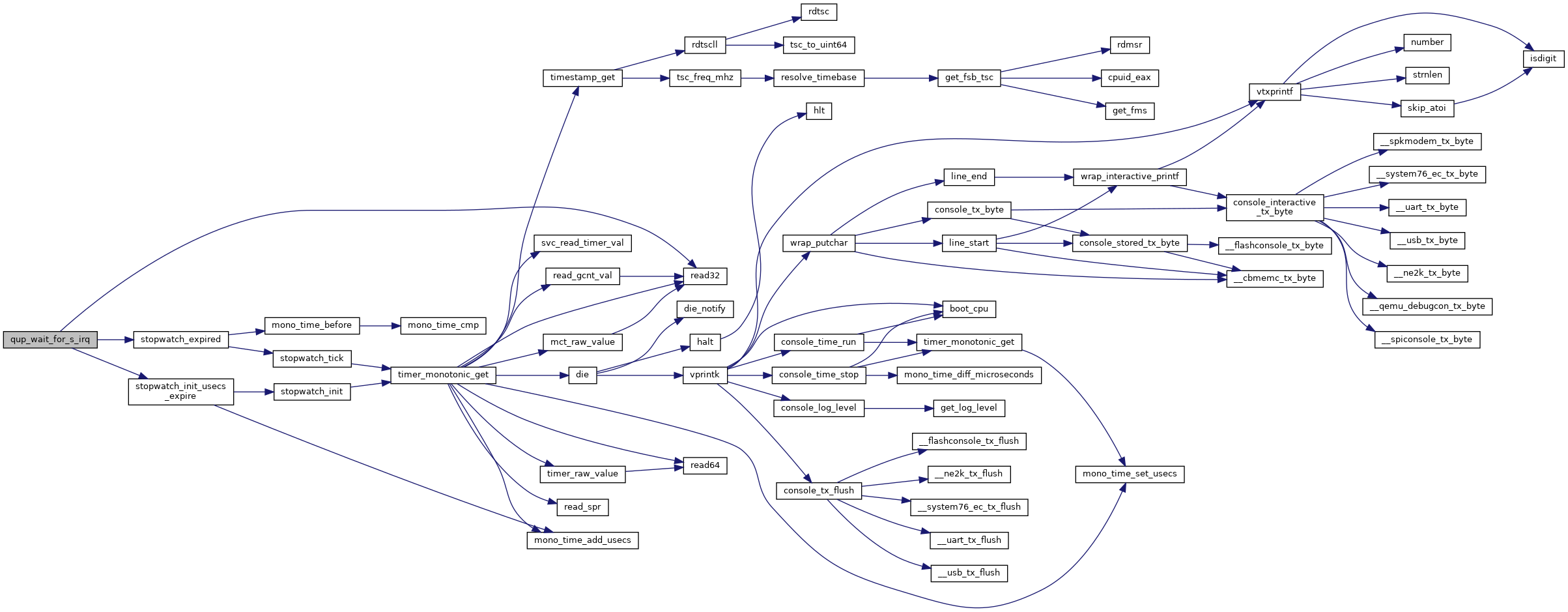

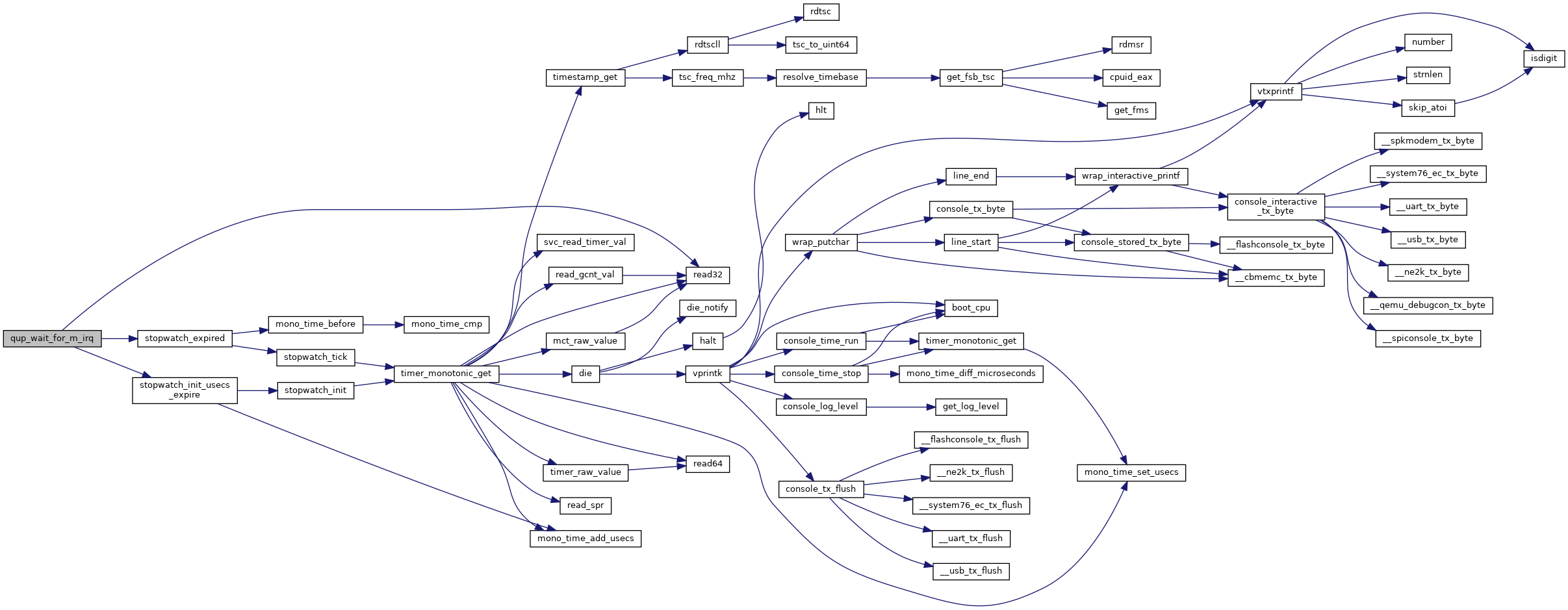

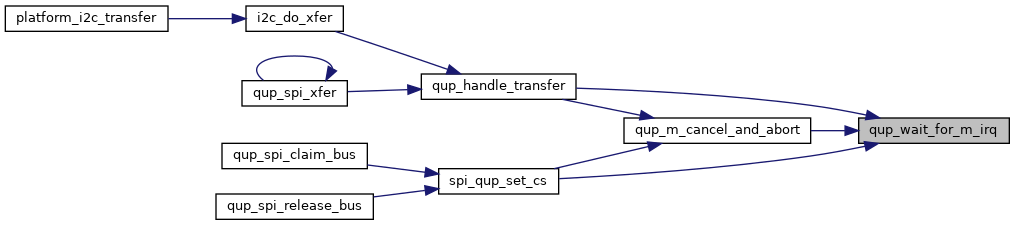

| u32 | qup_wait_for_m_irq (unsigned int bus) |

| u32 | qup_wait_for_s_irq (unsigned int bus) |

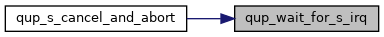

| void | qup_m_cancel_and_abort (unsigned int bus) |

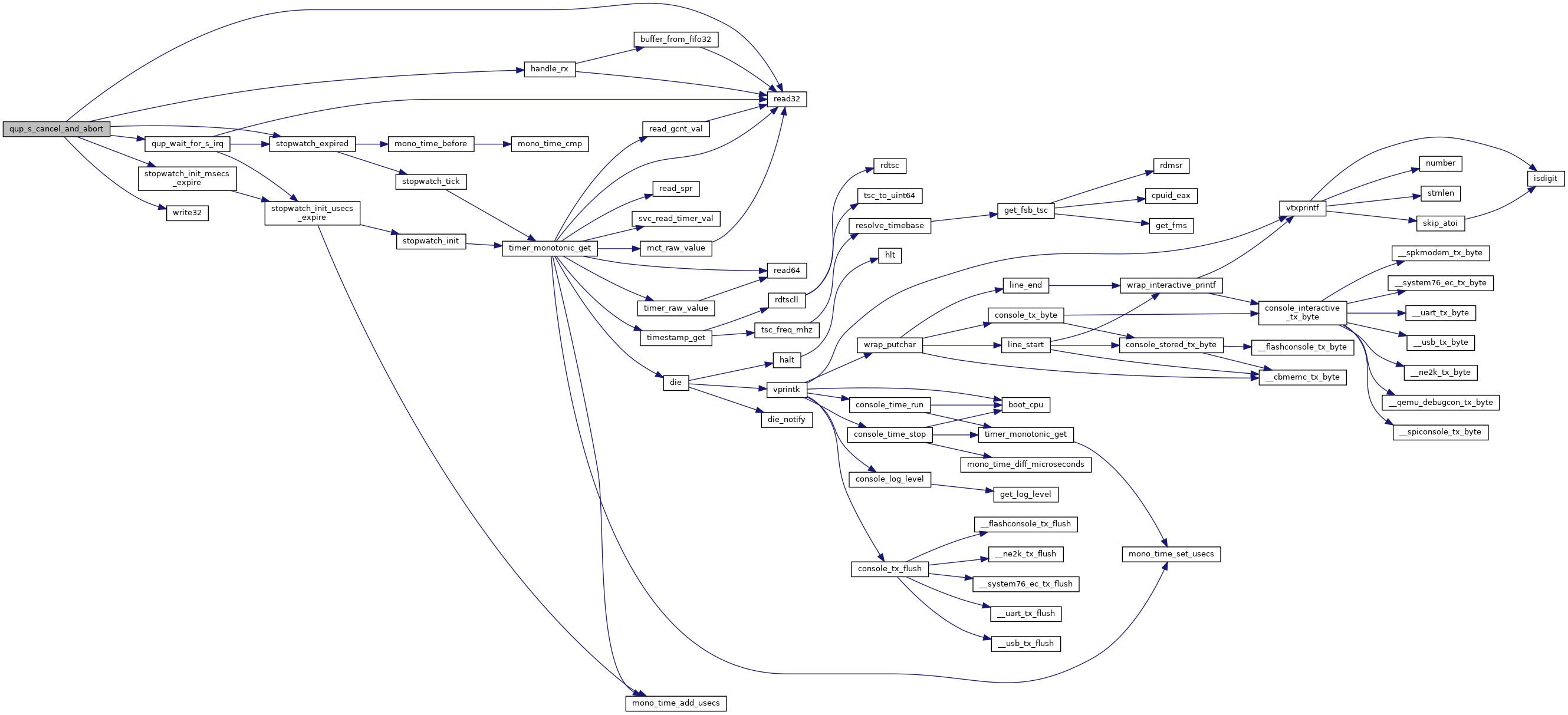

| void | qup_s_cancel_and_abort (unsigned int bus) |

| int | qup_handle_transfer (unsigned int bus, const void *dout, void *din, int size, struct stopwatch *timeout) |

| #define AHB_SEC_SLV_CLK_CGC_ON BIT(3) |

Definition at line 154 of file qup_se_handlers_common.h.

| #define BITS_PER_WORD 8 |

Definition at line 167 of file qup_se_handlers_common.h.

| #define BYTES_PER_FIFO_WORD 4 |

Definition at line 164 of file qup_se_handlers_common.h.

| #define CFG_AHB_CLK_CGC_ON BIT(0) |

Definition at line 25 of file qup_se_handlers_common.h.

| #define CFG_AHB_WR_ACLK_CGC_ON BIT(1) |

Definition at line 26 of file qup_se_handlers_common.h.

| #define CLK_DIV_MSK (0xFFF << CLK_DIV_SHFT) |

Definition at line 41 of file qup_se_handlers_common.h.

| #define CLK_DIV_SHFT 4 |

Definition at line 40 of file qup_se_handlers_common.h.

| #define CLK_SEL_MSK QC_GENMASK(2, 0) |

Definition at line 52 of file qup_se_handlers_common.h.

| #define DATA_AHB_CLK_CGC_ON BIT(2) |

Definition at line 27 of file qup_se_handlers_common.h.

| #define DEFAULT_CGC_EN |

Definition at line 34 of file qup_se_handlers_common.h.

| #define DEFAULT_IO_OUTPUT_CTRL_MSK QC_GENMASK(6, 0) |

Definition at line 16 of file qup_se_handlers_common.h.

| #define DEFAULT_SE_CLK (19200 * KHz) |

Definition at line 160 of file qup_se_handlers_common.h.

| #define DMA_AHB_SLV_CFG_ON BIT(2) |

Definition at line 153 of file qup_se_handlers_common.h.

| #define DMA_RX_CLK_CGC_ON BIT(0) |

Definition at line 151 of file qup_se_handlers_common.h.

| #define DMA_RX_IRQ_EN BIT(0) |

Definition at line 145 of file qup_se_handlers_common.h.

| #define DMA_TX_CLK_CGC_ON BIT(1) |

Definition at line 152 of file qup_se_handlers_common.h.

| #define DMA_TX_IRQ_EN BIT(1) |

Definition at line 146 of file qup_se_handlers_common.h.

| #define DUMMY_RX_NON_BUFFERABLE BIT(4) |

Definition at line 155 of file qup_se_handlers_common.h.

| #define EXT_CLK_CGC_ON BIT(6) |

Definition at line 31 of file qup_se_handlers_common.h.

| #define FIFO_DEPTH 16 |

Definition at line 166 of file qup_se_handlers_common.h.

| #define FIFO_IF_DISABLE BIT(0) |

Definition at line 44 of file qup_se_handlers_common.h.

| #define FIFO_WIDTH 32 |

Definition at line 165 of file qup_se_handlers_common.h.

| #define FORCE_DEFAULT BIT(0) |

Definition at line 19 of file qup_se_handlers_common.h.

| #define FW_REV_PROTOCOL_MSK QC_GENMASK(15, 8) |

Definition at line 47 of file qup_se_handlers_common.h.

| #define FW_REV_PROTOCOL_SHFT 8 |

Definition at line 48 of file qup_se_handlers_common.h.

| #define FW_REV_VERSION_SHFT 0 |

Definition at line 49 of file qup_se_handlers_common.h.

| #define GENI_DFS_IF_CFG_DFS_IF_EN_BMSK BIT(0) |

Definition at line 161 of file qup_se_handlers_common.h.

| #define GENI_DMA_MODE_EN BIT(0) |

Definition at line 55 of file qup_se_handlers_common.h.

| #define GENI_FW_REVISION_RO_PROTOCOL_MASK 0x0000FF00 |

Definition at line 21 of file qup_se_handlers_common.h.

| #define GENI_FW_REVISION_RO_PROTOCOL_SHIFT 0x00000008 |

Definition at line 22 of file qup_se_handlers_common.h.

| #define GENI_M_IRQ_EN BIT(2) |

Definition at line 147 of file qup_se_handlers_common.h.

| #define GENI_S_IRQ_EN BIT(3) |

Definition at line 148 of file qup_se_handlers_common.h.

| #define M_CMD_ABORT_EN BIT(5) |

Definition at line 83 of file qup_se_handlers_common.h.

| #define M_CMD_CANCEL_EN BIT(4) |

Definition at line 82 of file qup_se_handlers_common.h.

| #define M_CMD_DONE_EN BIT(0) |

Definition at line 78 of file qup_se_handlers_common.h.

| #define M_CMD_FAILURE_EN BIT(3) |

Definition at line 81 of file qup_se_handlers_common.h.

| #define M_CMD_OVERRUN_EN BIT(1) |

Definition at line 79 of file qup_se_handlers_common.h.

| #define M_COMMON_GENI_M_IRQ_EN |

Definition at line 103 of file qup_se_handlers_common.h.

| #define M_GENI_CMD_ABORT BIT(1) |

Definition at line 64 of file qup_se_handlers_common.h.

| #define M_GENI_CMD_CANCEL BIT(2) |

Definition at line 63 of file qup_se_handlers_common.h.

| #define M_GENI_DISABLE BIT(0) |

Definition at line 65 of file qup_se_handlers_common.h.

| #define M_GP_IRQ_0_EN BIT(9) |

Definition at line 87 of file qup_se_handlers_common.h.

| #define M_GP_IRQ_1_EN BIT(10) |

Definition at line 88 of file qup_se_handlers_common.h.

| #define M_GP_IRQ_2_EN BIT(11) |

Definition at line 89 of file qup_se_handlers_common.h.

| #define M_GP_IRQ_3_EN BIT(12) |

Definition at line 90 of file qup_se_handlers_common.h.

| #define M_GP_IRQ_4_EN BIT(13) |

Definition at line 91 of file qup_se_handlers_common.h.

| #define M_GP_IRQ_5_EN BIT(14) |

Definition at line 92 of file qup_se_handlers_common.h.

| #define M_GP_SYNC_IRQ_0_EN BIT(8) |

Definition at line 86 of file qup_se_handlers_common.h.

| #define M_ILLEGAL_CMD_EN BIT(2) |

Definition at line 80 of file qup_se_handlers_common.h.

| #define M_IO_DATA_ASSERT_EN BIT(23) |

Definition at line 94 of file qup_se_handlers_common.h.

| #define M_IO_DATA_DEASSERT_EN BIT(22) |

Definition at line 93 of file qup_se_handlers_common.h.

| #define M_OPCODE_MSK QC_GENMASK(31, 27) |

Definition at line 58 of file qup_se_handlers_common.h.

| #define M_OPCODE_SHFT 27 |

Definition at line 59 of file qup_se_handlers_common.h.

| #define M_PARAMS_MSK QC_GENMASK(26, 0) |

Definition at line 60 of file qup_se_handlers_common.h.

| #define M_RX_FIFO_LAST_EN BIT(27) |

Definition at line 98 of file qup_se_handlers_common.h.

| #define M_RX_FIFO_RD_ERR_EN BIT(24) |

Definition at line 95 of file qup_se_handlers_common.h.

| #define M_RX_FIFO_WATERMARK_EN BIT(26) |

Definition at line 97 of file qup_se_handlers_common.h.

| #define M_RX_FIFO_WR_ERR_EN BIT(25) |

Definition at line 96 of file qup_se_handlers_common.h.

| #define M_RX_IRQ_EN BIT(7) |

Definition at line 85 of file qup_se_handlers_common.h.

| #define M_SEC_IRQ_EN BIT(31) |

Definition at line 102 of file qup_se_handlers_common.h.

| #define M_TIMESTAMP_EN BIT(6) |

Definition at line 84 of file qup_se_handlers_common.h.

| #define M_TX_FIFO_RD_ERR_EN BIT(28) |

Definition at line 99 of file qup_se_handlers_common.h.

| #define M_TX_FIFO_WATERMARK_EN BIT(30) |

Definition at line 101 of file qup_se_handlers_common.h.

| #define M_TX_FIFO_WR_ERR_EN BIT(29) |

Definition at line 100 of file qup_se_handlers_common.h.

| #define PACK_VECTOR0 0x0FE |

Definition at line 179 of file qup_se_handlers_common.h.

| #define PACK_VECTOR1 0x1FE |

Definition at line 181 of file qup_se_handlers_common.h.

| #define PACK_VECTOR2 0x2FE |

Definition at line 183 of file qup_se_handlers_common.h.

| #define PACK_VECTOR3 0x3FF |

Definition at line 185 of file qup_se_handlers_common.h.

| #define PROG_RAM_HCLK_OFF BIT(8) |

Definition at line 32 of file qup_se_handlers_common.h.

| #define PROG_RAM_SCLK_OFF BIT(9) |

Definition at line 33 of file qup_se_handlers_common.h.

Definition at line 13 of file qup_se_handlers_common.h.

| #define RX_CLK_CGC_ON BIT(5) |

Definition at line 30 of file qup_se_handlers_common.h.

| #define RX_DMA_IRQ_DELAY_MSK QC_GENMASK(8, 6) |

Definition at line 157 of file qup_se_handlers_common.h.

| #define RX_DMA_IRQ_DELAY_SHFT 6 |

Definition at line 158 of file qup_se_handlers_common.h.

| #define RX_DMA_ZERO_PADDING_EN BIT(5) |

Definition at line 156 of file qup_se_handlers_common.h.

| #define RX_FIFO_WC_MSK QC_GENMASK(24, 0) |

Definition at line 142 of file qup_se_handlers_common.h.

| #define RX_LAST BIT(31) |

Definition at line 139 of file qup_se_handlers_common.h.

| #define RX_LAST_BYTE_VALID_MSK QC_GENMASK(30, 28) |

Definition at line 140 of file qup_se_handlers_common.h.

| #define RX_LAST_BYTE_VALID_SHFT 28 |

Definition at line 141 of file qup_se_handlers_common.h.

| #define S_CMD_ABORT_EN BIT(5) |

Definition at line 115 of file qup_se_handlers_common.h.

| #define S_CMD_CANCEL_EN BIT(4) |

Definition at line 114 of file qup_se_handlers_common.h.

| #define S_CMD_DONE_EN BIT(0) |

Definition at line 110 of file qup_se_handlers_common.h.

| #define S_CMD_FAILURE_EN BIT(3) |

Definition at line 113 of file qup_se_handlers_common.h.

| #define S_CMD_OVERRUN_EN BIT(1) |

Definition at line 111 of file qup_se_handlers_common.h.

| #define S_COMMON_GENI_S_IRQ_EN |

Definition at line 129 of file qup_se_handlers_common.h.

| #define S_GENI_CMD_ABORT BIT(1) |

Definition at line 74 of file qup_se_handlers_common.h.

| #define S_GENI_CMD_CANCEL BIT(2) |

Definition at line 73 of file qup_se_handlers_common.h.

| #define S_GENI_DISABLE BIT(0) |

Definition at line 75 of file qup_se_handlers_common.h.

| #define S_GP_IRQ_0_EN BIT(9) |

Definition at line 117 of file qup_se_handlers_common.h.

| #define S_GP_IRQ_1_EN BIT(10) |

Definition at line 118 of file qup_se_handlers_common.h.

| #define S_GP_IRQ_2_EN BIT(11) |

Definition at line 119 of file qup_se_handlers_common.h.

| #define S_GP_IRQ_3_EN BIT(12) |

Definition at line 120 of file qup_se_handlers_common.h.

| #define S_GP_IRQ_4_EN BIT(13) |

Definition at line 121 of file qup_se_handlers_common.h.

| #define S_GP_IRQ_5_EN BIT(14) |

Definition at line 122 of file qup_se_handlers_common.h.

| #define S_GP_SYNC_IRQ_0_EN BIT(8) |

Definition at line 116 of file qup_se_handlers_common.h.

| #define S_ILLEGAL_CMD_EN BIT(2) |

Definition at line 112 of file qup_se_handlers_common.h.

| #define S_IO_DATA_ASSERT_EN BIT(23) |

Definition at line 124 of file qup_se_handlers_common.h.

| #define S_IO_DATA_DEASSERT_EN BIT(22) |

Definition at line 123 of file qup_se_handlers_common.h.

| #define S_OPCODE_MSK QC_GENMASK(31, 27) |

Definition at line 68 of file qup_se_handlers_common.h.

| #define S_OPCODE_SHFT 27 |

Definition at line 69 of file qup_se_handlers_common.h.

| #define S_PARAMS_MSK QC_GENMASK(26, 0) |

Definition at line 70 of file qup_se_handlers_common.h.

| #define S_RX_FIFO_LAST_EN BIT(27) |

Definition at line 128 of file qup_se_handlers_common.h.

| #define S_RX_FIFO_RD_ERR_EN BIT(24) |

Definition at line 125 of file qup_se_handlers_common.h.

| #define S_RX_FIFO_WATERMARK_EN BIT(26) |

Definition at line 127 of file qup_se_handlers_common.h.

| #define S_RX_FIFO_WR_ERR_EN BIT(25) |

Definition at line 126 of file qup_se_handlers_common.h.

| #define SCLK_CGC_ON BIT(3) |

Definition at line 28 of file qup_se_handlers_common.h.

| #define SER_CLK_EN BIT(0) |

Definition at line 39 of file qup_se_handlers_common.h.

| #define TX_CLK_CGC_ON BIT(4) |

Definition at line 29 of file qup_se_handlers_common.h.

| #define TX_FIFO_WC QC_GENMASK(27, 0) |

Definition at line 136 of file qup_se_handlers_common.h.

| #define TX_WATERMARK 1 |

Definition at line 168 of file qup_se_handlers_common.h.

| #define WATERMARK_MSK QC_GENMASK(5, 0) |

Definition at line 133 of file qup_se_handlers_common.h.

| enum se_mode |

| Enumerator | |

|---|---|

| NONE | |

| GSI | |

| FIFO | |

| CPU_DMA | |

| MIXED | |

Definition at line 195 of file qup_se_handlers_common.h.

| enum se_protocol |

| Enumerator | |

|---|---|

| SE_PROTOCOL_SPI | |

| SE_PROTOCOL_UART | |

| SE_PROTOCOL_I2C | |

| SE_PROTOCOL_I3C | |

| SE_PROTOCOL_MAX | |

Definition at line 187 of file qup_se_handlers_common.h.

| check_member | ( | gsi_regs | , |

| ee_n_gsi_ee_generic_cmd | , | ||

| 0xF018 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_cgc_ctrl | , | ||

| 0x60 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_ee_n_scratch_0_addr | , | ||

| 0xF400 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_ee_n_scratch_1_addr | , | ||

| 0xF404 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_inst_ramn | , | ||

| 0x4C000 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_manager_mcs_code_ver | , | ||

| 0x8 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_periph_base_lsb | , | ||

| 0x18 | |||

| ) |

| check_member | ( | gsi_regs | , |

| gsi_zeros | , | ||

| 0x10 | |||

| ) |

| check_member | ( | qup_regs | , |

| dma_test_bus_ctrl | , | ||

| 0xE44 | |||

| ) |

| check_member | ( | qup_regs | , |

| geni_cfg_reg108 | , | ||

| 0x2B0 | |||

| ) |

| check_member | ( | qup_regs | , |

| geni_clk_sel | , | ||

| 0x7C | |||

| ) |

| check_member | ( | qup_regs | , |

| geni_dma_mode_en | , | ||

| 0x258 | |||

| ) |

| check_member | ( | qup_regs | , |

| geni_i3c_ibi_rd_data | , | ||

| 0xA84 | |||

| ) |

| check_member | ( | qup_regs | , |

| se_geni_cfg_ramn | , | ||

| 0x1010 | |||

| ) |

| check_member | ( | qup_regs | , |

| se_geni_fw_multilock_sp | , | ||

| 0x2014 | |||

| ) |

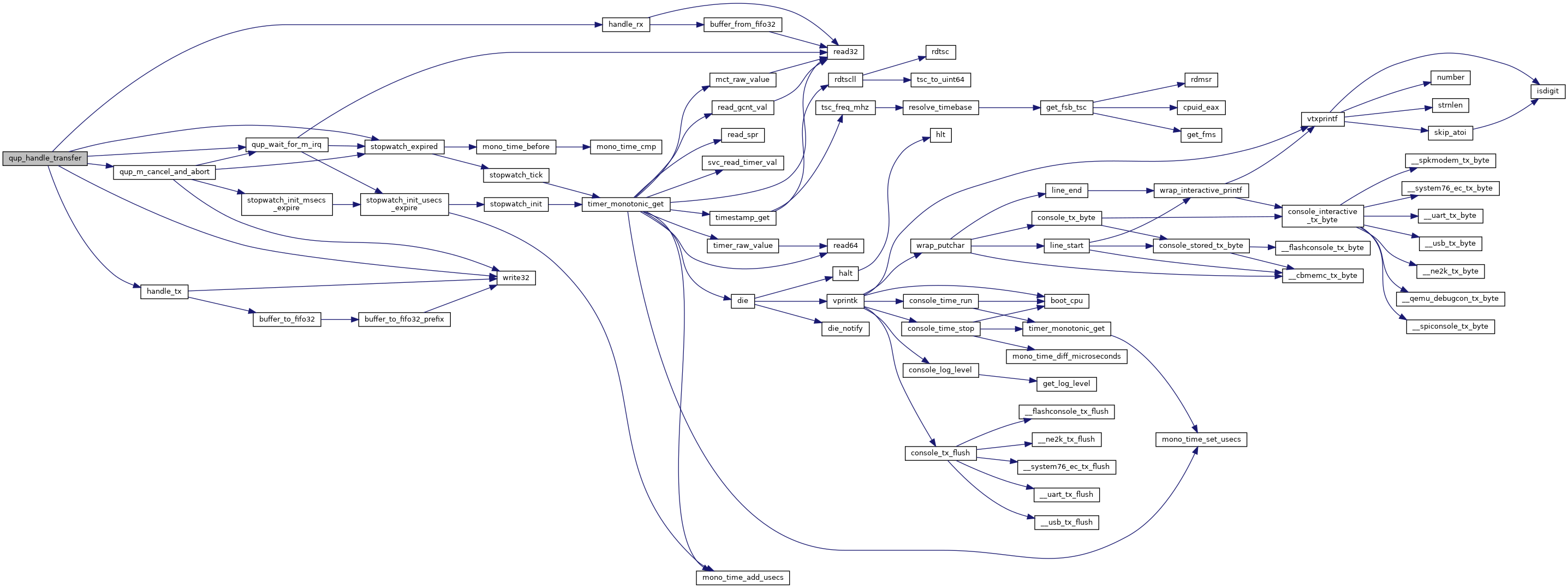

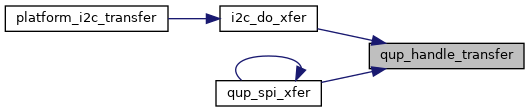

| int qup_handle_transfer | ( | unsigned int | bus, |

| const void * | dout, | ||

| void * | din, | ||

| int | size, | ||

| struct stopwatch * | timeout | ||

| ) |

Definition at line 152 of file qup_se_handler.c.

References BIOS_INFO, handle_rx(), handle_tx(), M_CMD_DONE_EN, M_RX_FIFO_LAST_EN, M_RX_FIFO_WATERMARK_EN, M_TX_FIFO_WATERMARK_EN, printk, qup_m_cancel_and_abort(), qup_wait_for_m_irq(), qup::regs, stopwatch_expired(), and write32().

Referenced by i2c_do_xfer(), and qup_spi_xfer().

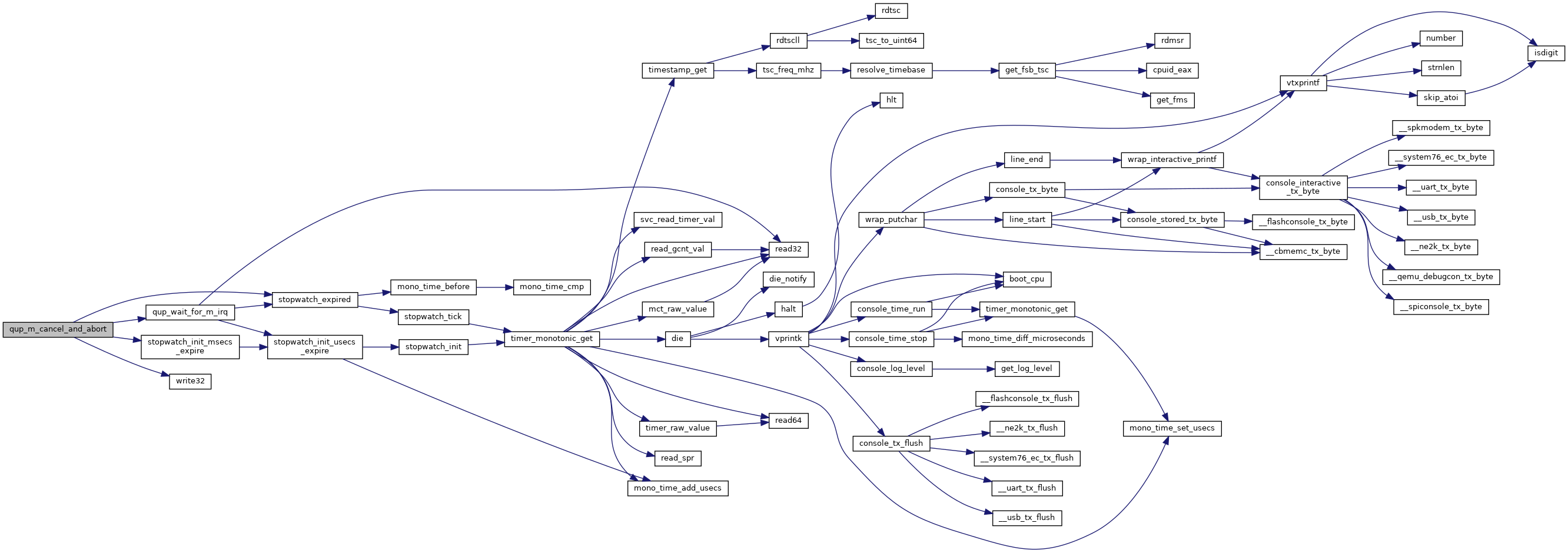

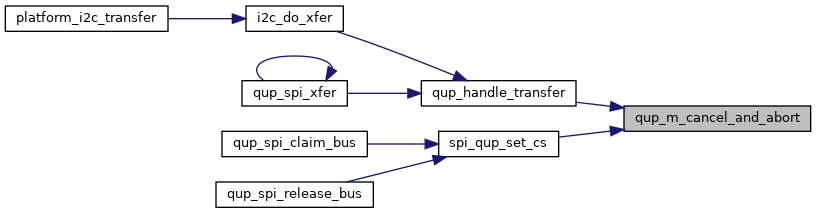

Definition at line 68 of file qup_se_handler.c.

References BIOS_INFO, M_CMD_ABORT_EN, M_CMD_CANCEL_EN, M_GENI_CMD_ABORT, M_GENI_CMD_CANCEL, printk, qup_wait_for_m_irq(), qup::regs, stopwatch_expired(), stopwatch_init_msecs_expire(), and write32().

Referenced by qup_handle_transfer(), and spi_qup_set_cs().

Definition at line 107 of file qup_se_handler.c.

References BIOS_INFO, buf, handle_rx(), printk, qup_wait_for_s_irq(), read32(), qup::regs, RX_LAST, S_CMD_ABORT_EN, S_CMD_CANCEL_EN, S_GENI_CMD_ABORT, S_GENI_CMD_CANCEL, stopwatch_expired(), stopwatch_init_msecs_expire(), and write32().

Definition at line 7 of file qup_se_handler.c.

References read32(), qup::regs, stopwatch_expired(), and stopwatch_init_usecs_expire().

Referenced by qup_handle_transfer(), qup_m_cancel_and_abort(), and spi_qup_set_cs().

Definition at line 22 of file qup_se_handler.c.

References read32(), qup::regs, stopwatch_expired(), and stopwatch_init_usecs_expire().

Referenced by qup_s_cancel_and_abort().