|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

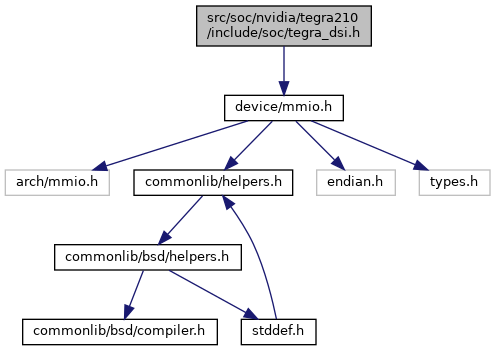

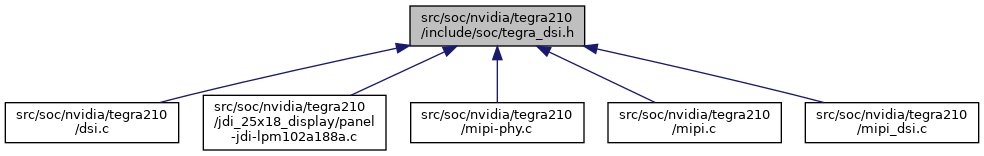

#include <device/mmio.h>

Go to the source code of this file.

Data Structures | |

| struct | tegra_dsi |

Macros | |

| #define | DSI_INCR_SYNCPT 0x00 |

| #define | DSI_INCR_SYNCPT_CONTROL 0x01 |

| #define | DSI_INCR_SYNCPT_ERROR 0x02 |

| #define | DSI_CTXSW 0x08 |

| #define | DSI_RD_DATA 0x09 |

| #define | DSI_WR_DATA 0x0a |

| #define | DSI_POWER_CONTROL 0x0b |

| #define | DSI_POWER_CONTROL_ENABLE (1 << 0) |

| #define | DSI_INT_ENABLE 0x0c |

| #define | DSI_INT_STATUS 0x0d |

| #define | DSI_INT_MASK 0x0e |

| #define | DSI_HOST_CONTROL 0x0f |

| #define | DSI_HOST_CONTROL_FIFO_RESET (1 << 21) |

| #define | DSI_HOST_CONTROL_CRC_RESET (1 << 20) |

| #define | DSI_HOST_CONTROL_TX_TRIG_SOL (0 << 12) |

| #define | DSI_HOST_CONTROL_TX_TRIG_FIFO (1 << 12) |

| #define | DSI_HOST_CONTROL_TX_TRIG_HOST (2 << 12) |

| #define | DSI_HOST_CONTROL_RAW (1 << 6) |

| #define | DSI_HOST_CONTROL_HS (1 << 5) |

| #define | DSI_HOST_CONTROL_FIFO_SEL (1 << 4) |

| #define | DSI_HOST_CONTROL_IMM_BTA (1 << 3) |

| #define | DSI_HOST_CONTROL_PKT_BTA (1 << 2) |

| #define | DSI_HOST_CONTROL_CS (1 << 1) |

| #define | DSI_HOST_CONTROL_ECC (1 << 0) |

| #define | DSI_CONTROL 0x10 |

| #define | DSI_CONTROL_HS_CLK_CTRL (1 << 20) |

| #define | DSI_CONTROL_CHANNEL(c) (((c) & 0x3) << 16) |

| #define | DSI_CONTROL_FORMAT(f) (((f) & 0x3) << 12) |

| #define | DSI_CONTROL_TX_TRIG(x) (((x) & 0x3) << 8) |

| #define | DSI_CONTROL_LANES(n) (((n) & 0x3) << 4) |

| #define | DSI_CONTROL_DCS_ENABLE (1 << 3) |

| #define | DSI_CONTROL_SOURCE(s) (((s) & 0x1) << 2) |

| #define | DSI_CONTROL_VIDEO_ENABLE (1 << 1) |

| #define | DSI_CONTROL_HOST_ENABLE (1 << 0) |

| #define | DSI_SOL_DELAY 0x11 |

| #define | DSI_MAX_THRESHOLD 0x12 |

| #define | DSI_TRIGGER 0x13 |

| #define | DSI_TRIGGER_HOST (1 << 1) |

| #define | DSI_TRIGGER_VIDEO (1 << 0) |

| #define | DSI_TX_CRC 0x14 |

| #define | DSI_STATUS 0x15 |

| #define | DSI_STATUS_IDLE (1 << 10) |

| #define | DSI_STATUS_UNDERFLOW (1 << 9) |

| #define | DSI_STATUS_OVERFLOW (1 << 8) |

| #define | DSI_INIT_SEQ_CONTROL 0x1a |

| #define | DSI_INIT_SEQ_DATA_0 0x1b |

| #define | DSI_INIT_SEQ_DATA_1 0x1c |

| #define | DSI_INIT_SEQ_DATA_2 0x1d |

| #define | DSI_INIT_SEQ_DATA_3 0x1e |

| #define | DSI_INIT_SEQ_DATA_4 0x1f |

| #define | DSI_INIT_SEQ_DATA_5 0x20 |

| #define | DSI_INIT_SEQ_DATA_6 0x21 |

| #define | DSI_INIT_SEQ_DATA_7 0x22 |

| #define | DSI_PKT_SEQ_0_LO 0x23 |

| #define | DSI_PKT_SEQ_0_HI 0x24 |

| #define | DSI_PKT_SEQ_1_LO 0x25 |

| #define | DSI_PKT_SEQ_1_HI 0x26 |

| #define | DSI_PKT_SEQ_2_LO 0x27 |

| #define | DSI_PKT_SEQ_2_HI 0x28 |

| #define | DSI_PKT_SEQ_3_LO 0x29 |

| #define | DSI_PKT_SEQ_3_HI 0x2a |

| #define | DSI_PKT_SEQ_4_LO 0x2b |

| #define | DSI_PKT_SEQ_4_HI 0x2c |

| #define | DSI_PKT_SEQ_5_LO 0x2d |

| #define | DSI_PKT_SEQ_5_HI 0x2e |

| #define | DSI_DCS_CMDS 0x33 |

| #define | DSI_PKT_LEN_0_1 0x34 |

| #define | DSI_PKT_LEN_2_3 0x35 |

| #define | DSI_PKT_LEN_4_5 0x36 |

| #define | DSI_PKT_LEN_6_7 0x37 |

| #define | DSI_PHY_TIMING_0 0x3c |

| #define | DSI_PHY_TIMING_1 0x3d |

| #define | DSI_PHY_TIMING_2 0x3e |

| #define | DSI_BTA_TIMING 0x3f |

| #define | DSI_TIMING_FIELD(value, period, hwinc) ((DIV_ROUND_CLOSEST(value, period) - (hwinc)) & 0xff) |

| #define | DSI_TIMEOUT_0 0x44 |

| #define | DSI_TIMEOUT_LRX(x) (((x) & 0xffff) << 16) |

| #define | DSI_TIMEOUT_HTX(x) (((x) & 0xffff) << 0) |

| #define | DSI_TIMEOUT_1 0x45 |

| #define | DSI_TIMEOUT_PR(x) (((x) & 0xffff) << 16) |

| #define | DSI_TIMEOUT_TA(x) (((x) & 0xffff) << 0) |

| #define | DSI_TO_TALLY 0x46 |

| #define | DSI_TALLY_TA(x) (((x) & 0xff) << 16) |

| #define | DSI_TALLY_LRX(x) (((x) & 0xff) << 8) |

| #define | DSI_TALLY_HTX(x) (((x) & 0xff) << 0) |

| #define | DSI_PAD_CONTROL_0 0x4b |

| #define | DSI_PAD_CONTROL_VS1_PDIO(x) (((x) & 0xf) << 0) |

| #define | DSI_PAD_CONTROL_VS1_PDIO_CLK (1 << 8) |

| #define | DSI_PAD_CONTROL_VS1_PULLDN(x) (((x) & 0xf) << 16) |

| #define | DSI_PAD_CONTROL_VS1_PULLDN_CLK (1 << 24) |

| #define | DSI_PAD_CONTROL_CD 0x4c |

| #define | DSI_PAD_CD_STATUS 0x4d |

| #define | DSI_VIDEO_MODE_CONTROL 0x4e |

| #define | DSI_PAD_CONTROL_1 0x4f |

| #define | DSI_PAD_CONTROL_2 0x50 |

| #define | DSI_PAD_OUT_CLK(x) (((x) & 0x7) << 0) |

| #define | DSI_PAD_LP_DN(x) (((x) & 0x7) << 4) |

| #define | DSI_PAD_LP_UP(x) (((x) & 0x7) << 8) |

| #define | DSI_PAD_SLEW_DN(x) (((x) & 0x7) << 12) |

| #define | DSI_PAD_SLEW_UP(x) (((x) & 0x7) << 16) |

| #define | DSI_PAD_CONTROL_3 0x51 |

| #define | DSI_PAD_PREEMP_PD_CLK(x) (((x) & 0x3) << 12) |

| #define | DSI_PAD_PREEMP_PU_CLK(x) (((x) & 0x3) << 8) |

| #define | DSI_PAD_PREEMP_PD(x) (((x) & 0x3) << 4) |

| #define | DSI_PAD_PREEMP_PU(x) (((x) & 0x3) << 0) |

| #define | DSI_PAD_CONTROL_4 0x52 |

| #define | DSI_GANGED_MODE_CONTROL 0x53 |

| #define | DSI_GANGED_MODE_CONTROL_ENABLE (1 << 0) |

| #define | DSI_GANGED_MODE_START 0x54 |

| #define | DSI_GANGED_MODE_SIZE 0x55 |

| #define | DSI_RAW_DATA_BYTE_COUNT 0x56 |

| #define | DSI_ULTRA_LOW_POWER_CONTROL 0x57 |

| #define | DSI_INIT_SEQ_DATA_8 0x58 |

| #define | DSI_INIT_SEQ_DATA_9 0x59 |

| #define | DSI_INIT_SEQ_DATA_10 0x5a |

| #define | DSI_INIT_SEQ_DATA_11 0x5b |

| #define | DSI_INIT_SEQ_DATA_12 0x5c |

| #define | DSI_INIT_SEQ_DATA_13 0x5d |

| #define | DSI_INIT_SEQ_DATA_14 0x5e |

| #define | DSI_INIT_SEQ_DATA_15 0x5f |

| #define | PKT_ID0(id) ((((id) & 0x3f) << 3) | (1 << 9)) |

| #define | PKT_LEN0(len) (((len) & 0x07) << 0) |

| #define | PKT_ID1(id) ((((id) & 0x3f) << 13) | (1 << 19)) |

| #define | PKT_LEN1(len) (((len) & 0x07) << 10) |

| #define | PKT_ID2(id) ((((id) & 0x3f) << 23) | (1 << 29)) |

| #define | PKT_LEN2(len) (((len) & 0x07) << 20) |

| #define | PKT_LP (1 << 30) |

| #define | NUM_PKT_SEQ 12 |

| #define | APB_MISC_GP_MIPI_PAD_CTRL_0 (TEGRA_APB_MISC_GP_BASE + 0x20) |

| #define | DSIB_MODE_SHIFT 1 |

| #define | DSIB_MODE_CSI (0 << DSIB_MODE_SHIFT) |

| #define | DSIB_MODE_DSI (1 << DSIB_MODE_SHIFT) |

| #define | MAX_DSI_VIDEO_FIFO_DEPTH 96 |

| #define | MAX_DSI_HOST_FIFO_DEPTH 64 |

Enumerations | |

| enum | tegra_dsi_format { TEGRA_DSI_FORMAT_16P , TEGRA_DSI_FORMAT_18NP , TEGRA_DSI_FORMAT_18P , TEGRA_DSI_FORMAT_24P } |

| enum | dsi_dev { DSI_A = 0 , DSI_B , NUM_DSI } |

Functions | |

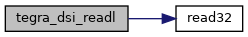

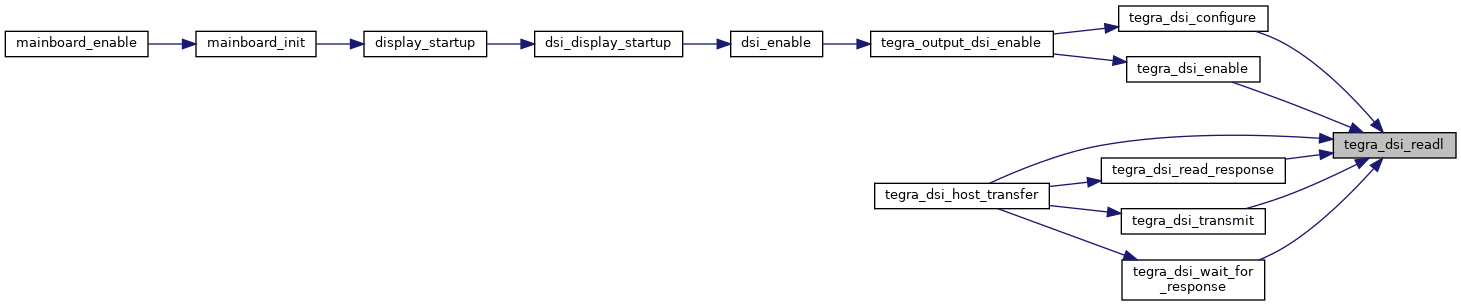

| static unsigned long | tegra_dsi_readl (struct tegra_dsi *dsi, unsigned long reg) |

| static void | tegra_dsi_writel (struct tegra_dsi *dsi, unsigned long value, unsigned long reg) |

| #define APB_MISC_GP_MIPI_PAD_CTRL_0 (TEGRA_APB_MISC_GP_BASE + 0x20) |

Definition at line 141 of file tegra_dsi.h.

| #define DSI_BTA_TIMING 0x3f |

Definition at line 80 of file tegra_dsi.h.

| #define DSI_CONTROL 0x10 |

Definition at line 31 of file tegra_dsi.h.

Definition at line 33 of file tegra_dsi.h.

| #define DSI_CONTROL_DCS_ENABLE (1 << 3) |

Definition at line 37 of file tegra_dsi.h.

| #define DSI_CONTROL_FORMAT | ( | f | ) | (((f) & 0x3) << 12) |

Definition at line 34 of file tegra_dsi.h.

| #define DSI_CONTROL_HOST_ENABLE (1 << 0) |

Definition at line 40 of file tegra_dsi.h.

| #define DSI_CONTROL_HS_CLK_CTRL (1 << 20) |

Definition at line 32 of file tegra_dsi.h.

| #define DSI_CONTROL_LANES | ( | n | ) | (((n) & 0x3) << 4) |

Definition at line 36 of file tegra_dsi.h.

Definition at line 38 of file tegra_dsi.h.

Definition at line 35 of file tegra_dsi.h.

| #define DSI_CONTROL_VIDEO_ENABLE (1 << 1) |

Definition at line 39 of file tegra_dsi.h.

| #define DSI_CTXSW 0x08 |

Definition at line 10 of file tegra_dsi.h.

| #define DSI_DCS_CMDS 0x33 |

Definition at line 72 of file tegra_dsi.h.

| #define DSI_GANGED_MODE_CONTROL 0x53 |

Definition at line 116 of file tegra_dsi.h.

| #define DSI_GANGED_MODE_CONTROL_ENABLE (1 << 0) |

Definition at line 117 of file tegra_dsi.h.

| #define DSI_GANGED_MODE_SIZE 0x55 |

Definition at line 119 of file tegra_dsi.h.

| #define DSI_GANGED_MODE_START 0x54 |

Definition at line 118 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL 0x0f |

Definition at line 18 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_CRC_RESET (1 << 20) |

Definition at line 20 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_CS (1 << 1) |

Definition at line 29 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_ECC (1 << 0) |

Definition at line 30 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_FIFO_RESET (1 << 21) |

Definition at line 19 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_FIFO_SEL (1 << 4) |

Definition at line 26 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_HS (1 << 5) |

Definition at line 25 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_IMM_BTA (1 << 3) |

Definition at line 27 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_PKT_BTA (1 << 2) |

Definition at line 28 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_RAW (1 << 6) |

Definition at line 24 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_TX_TRIG_FIFO (1 << 12) |

Definition at line 22 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_TX_TRIG_HOST (2 << 12) |

Definition at line 23 of file tegra_dsi.h.

| #define DSI_HOST_CONTROL_TX_TRIG_SOL (0 << 12) |

Definition at line 21 of file tegra_dsi.h.

| #define DSI_INCR_SYNCPT 0x00 |

Definition at line 7 of file tegra_dsi.h.

| #define DSI_INCR_SYNCPT_CONTROL 0x01 |

Definition at line 8 of file tegra_dsi.h.

| #define DSI_INCR_SYNCPT_ERROR 0x02 |

Definition at line 9 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_CONTROL 0x1a |

Definition at line 51 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_0 0x1b |

Definition at line 52 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_1 0x1c |

Definition at line 53 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_10 0x5a |

Definition at line 124 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_11 0x5b |

Definition at line 125 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_12 0x5c |

Definition at line 126 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_13 0x5d |

Definition at line 127 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_14 0x5e |

Definition at line 128 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_15 0x5f |

Definition at line 129 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_2 0x1d |

Definition at line 54 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_3 0x1e |

Definition at line 55 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_4 0x1f |

Definition at line 56 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_5 0x20 |

Definition at line 57 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_6 0x21 |

Definition at line 58 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_7 0x22 |

Definition at line 59 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_8 0x58 |

Definition at line 122 of file tegra_dsi.h.

| #define DSI_INIT_SEQ_DATA_9 0x59 |

Definition at line 123 of file tegra_dsi.h.

| #define DSI_INT_ENABLE 0x0c |

Definition at line 15 of file tegra_dsi.h.

| #define DSI_INT_MASK 0x0e |

Definition at line 17 of file tegra_dsi.h.

| #define DSI_INT_STATUS 0x0d |

Definition at line 16 of file tegra_dsi.h.

| #define DSI_MAX_THRESHOLD 0x12 |

Definition at line 42 of file tegra_dsi.h.

| #define DSI_PAD_CD_STATUS 0x4d |

Definition at line 101 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_0 0x4b |

Definition at line 95 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_1 0x4f |

Definition at line 103 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_2 0x50 |

Definition at line 104 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_3 0x51 |

Definition at line 110 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_4 0x52 |

Definition at line 115 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_CD 0x4c |

Definition at line 100 of file tegra_dsi.h.

Definition at line 96 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_VS1_PDIO_CLK (1 << 8) |

Definition at line 97 of file tegra_dsi.h.

Definition at line 98 of file tegra_dsi.h.

| #define DSI_PAD_CONTROL_VS1_PULLDN_CLK (1 << 24) |

Definition at line 99 of file tegra_dsi.h.

Definition at line 106 of file tegra_dsi.h.

Definition at line 107 of file tegra_dsi.h.

Definition at line 105 of file tegra_dsi.h.

Definition at line 113 of file tegra_dsi.h.

Definition at line 111 of file tegra_dsi.h.

Definition at line 114 of file tegra_dsi.h.

Definition at line 112 of file tegra_dsi.h.

Definition at line 108 of file tegra_dsi.h.

Definition at line 109 of file tegra_dsi.h.

| #define DSI_PHY_TIMING_0 0x3c |

Definition at line 77 of file tegra_dsi.h.

| #define DSI_PHY_TIMING_1 0x3d |

Definition at line 78 of file tegra_dsi.h.

| #define DSI_PHY_TIMING_2 0x3e |

Definition at line 79 of file tegra_dsi.h.

| #define DSI_PKT_LEN_0_1 0x34 |

Definition at line 73 of file tegra_dsi.h.

| #define DSI_PKT_LEN_2_3 0x35 |

Definition at line 74 of file tegra_dsi.h.

| #define DSI_PKT_LEN_4_5 0x36 |

Definition at line 75 of file tegra_dsi.h.

| #define DSI_PKT_LEN_6_7 0x37 |

Definition at line 76 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_0_HI 0x24 |

Definition at line 61 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_0_LO 0x23 |

Definition at line 60 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_1_HI 0x26 |

Definition at line 63 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_1_LO 0x25 |

Definition at line 62 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_2_HI 0x28 |

Definition at line 65 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_2_LO 0x27 |

Definition at line 64 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_3_HI 0x2a |

Definition at line 67 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_3_LO 0x29 |

Definition at line 66 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_4_HI 0x2c |

Definition at line 69 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_4_LO 0x2b |

Definition at line 68 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_5_HI 0x2e |

Definition at line 71 of file tegra_dsi.h.

| #define DSI_PKT_SEQ_5_LO 0x2d |

Definition at line 70 of file tegra_dsi.h.

| #define DSI_POWER_CONTROL 0x0b |

Definition at line 13 of file tegra_dsi.h.

| #define DSI_POWER_CONTROL_ENABLE (1 << 0) |

Definition at line 14 of file tegra_dsi.h.

| #define DSI_RAW_DATA_BYTE_COUNT 0x56 |

Definition at line 120 of file tegra_dsi.h.

| #define DSI_RD_DATA 0x09 |

Definition at line 11 of file tegra_dsi.h.

| #define DSI_SOL_DELAY 0x11 |

Definition at line 41 of file tegra_dsi.h.

| #define DSI_STATUS 0x15 |

Definition at line 47 of file tegra_dsi.h.

| #define DSI_STATUS_IDLE (1 << 10) |

Definition at line 48 of file tegra_dsi.h.

| #define DSI_STATUS_OVERFLOW (1 << 8) |

Definition at line 50 of file tegra_dsi.h.

| #define DSI_STATUS_UNDERFLOW (1 << 9) |

Definition at line 49 of file tegra_dsi.h.

Definition at line 94 of file tegra_dsi.h.

Definition at line 93 of file tegra_dsi.h.

Definition at line 92 of file tegra_dsi.h.

| #define DSI_TIMEOUT_0 0x44 |

Definition at line 85 of file tegra_dsi.h.

| #define DSI_TIMEOUT_1 0x45 |

Definition at line 88 of file tegra_dsi.h.

Definition at line 87 of file tegra_dsi.h.

Definition at line 86 of file tegra_dsi.h.

Definition at line 89 of file tegra_dsi.h.

Definition at line 90 of file tegra_dsi.h.

| #define DSI_TIMING_FIELD | ( | value, | |

| period, | |||

| hwinc | |||

| ) | ((DIV_ROUND_CLOSEST(value, period) - (hwinc)) & 0xff) |

Definition at line 82 of file tegra_dsi.h.

| #define DSI_TO_TALLY 0x46 |

Definition at line 91 of file tegra_dsi.h.

| #define DSI_TRIGGER 0x13 |

Definition at line 43 of file tegra_dsi.h.

| #define DSI_TRIGGER_HOST (1 << 1) |

Definition at line 44 of file tegra_dsi.h.

| #define DSI_TRIGGER_VIDEO (1 << 0) |

Definition at line 45 of file tegra_dsi.h.

| #define DSI_TX_CRC 0x14 |

Definition at line 46 of file tegra_dsi.h.

| #define DSI_ULTRA_LOW_POWER_CONTROL 0x57 |

Definition at line 121 of file tegra_dsi.h.

| #define DSI_VIDEO_MODE_CONTROL 0x4e |

Definition at line 102 of file tegra_dsi.h.

| #define DSI_WR_DATA 0x0a |

Definition at line 12 of file tegra_dsi.h.

| #define DSIB_MODE_CSI (0 << DSIB_MODE_SHIFT) |

Definition at line 143 of file tegra_dsi.h.

| #define DSIB_MODE_DSI (1 << DSIB_MODE_SHIFT) |

Definition at line 144 of file tegra_dsi.h.

| #define DSIB_MODE_SHIFT 1 |

Definition at line 142 of file tegra_dsi.h.

| #define MAX_DSI_HOST_FIFO_DEPTH 64 |

Definition at line 168 of file tegra_dsi.h.

| #define MAX_DSI_VIDEO_FIFO_DEPTH 96 |

Definition at line 167 of file tegra_dsi.h.

| #define NUM_PKT_SEQ 12 |

Definition at line 139 of file tegra_dsi.h.

| #define PKT_ID0 | ( | id | ) | ((((id) & 0x3f) << 3) | (1 << 9)) |

Definition at line 131 of file tegra_dsi.h.

| #define PKT_ID1 | ( | id | ) | ((((id) & 0x3f) << 13) | (1 << 19)) |

Definition at line 133 of file tegra_dsi.h.

| #define PKT_ID2 | ( | id | ) | ((((id) & 0x3f) << 23) | (1 << 29)) |

Definition at line 135 of file tegra_dsi.h.

| #define PKT_LEN0 | ( | len | ) | (((len) & 0x07) << 0) |

Definition at line 132 of file tegra_dsi.h.

| #define PKT_LEN1 | ( | len | ) | (((len) & 0x07) << 10) |

Definition at line 134 of file tegra_dsi.h.

| #define PKT_LEN2 | ( | len | ) | (((len) & 0x07) << 20) |

Definition at line 136 of file tegra_dsi.h.

| #define PKT_LP (1 << 30) |

Definition at line 138 of file tegra_dsi.h.

| enum dsi_dev |

| Enumerator | |

|---|---|

| DSI_A | |

| DSI_B | |

| NUM_DSI | |

Definition at line 156 of file tegra_dsi.h.

| enum tegra_dsi_format |

| Enumerator | |

|---|---|

| TEGRA_DSI_FORMAT_16P | |

| TEGRA_DSI_FORMAT_18NP | |

| TEGRA_DSI_FORMAT_18P | |

| TEGRA_DSI_FORMAT_24P | |

Definition at line 149 of file tegra_dsi.h.

Definition at line 196 of file tegra_dsi.h.

References read32(), and tegra_dsi::regs.

Referenced by tegra_dsi_configure(), tegra_dsi_enable(), tegra_dsi_host_transfer(), tegra_dsi_read_response(), tegra_dsi_transmit(), and tegra_dsi_wait_for_response().

|

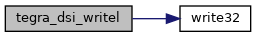

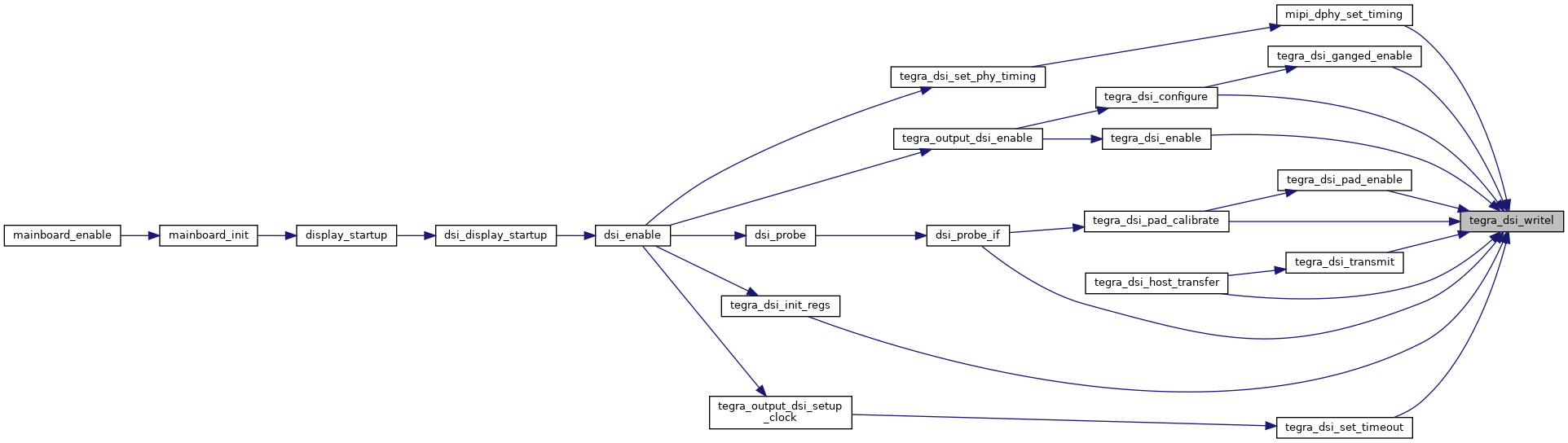

inlinestatic |

Definition at line 202 of file tegra_dsi.h.

References tegra_dsi::regs, value, and write32().

Referenced by dsi_probe_if(), mipi_dphy_set_timing(), tegra_dsi_configure(), tegra_dsi_enable(), tegra_dsi_ganged_enable(), tegra_dsi_host_transfer(), tegra_dsi_init_regs(), tegra_dsi_pad_calibrate(), tegra_dsi_pad_enable(), tegra_dsi_set_timeout(), and tegra_dsi_transmit().