|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

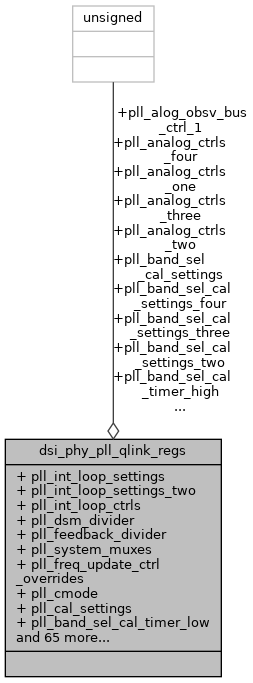

#include <mdssreg.h>

| uint32_t dsi_phy_pll_qlink_regs::pll_alog_obsv_bus_ctrl_1 |

Definition at line 209 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_analog_ctrls_four |

Definition at line 131 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_analog_ctrls_one |

Definition at line 126 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_analog_ctrls_three |

Definition at line 130 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_analog_ctrls_two |

Definition at line 127 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings |

Definition at line 141 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings_four |

Definition at line 148 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings_three |

Definition at line 147 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_cal_settings_two |

Definition at line 146 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_cal_timer_high |

Definition at line 140 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_cal_timer_low |

Definition at line 139 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_icode_high |

Definition at line 149 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_icode_low |

Definition at line 150 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_ifilt |

Definition at line 145 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_max |

Definition at line 143 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_min |

Definition at line 142 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_sel_pfilt |

Definition at line 144 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_band_set_rate[2] |

Definition at line 196 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_bias_ctrl_1 |

Definition at line 207 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_bias_ctrl_2 |

Definition at line 208 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_cal_settings |

Definition at line 138 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_clock_inverters |

Definition at line 205 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_cmode |

Definition at line 137 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_core_input_override |

Definition at line 168 of file mdssreg.h.

Referenced by dsi_pll_commit(), and dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_core_override |

Definition at line 167 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_dec_frac_muxes |

Definition at line 176 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_decimal_div_start_1 |

Definition at line 177 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_digital_timers |

Definition at line 170 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_digital_timers_two |

Definition at line 171 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_dsm_divider |

Definition at line 133 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_fastlock_ctrl |

Definition at line 164 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_feedback_divider |

Definition at line 134 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_fl_int_gain_pfilt_band[2] |

Definition at line 198 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_frac_div_start_high1 |

Definition at line 180 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_frac_div_start_low1 |

Definition at line 178 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_frac_div_start_mid1 |

Definition at line 179 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_freq_detect_settings_one |

Definition at line 151 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_freq_tune_accum_init_mux |

Definition at line 201 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_freq_update_ctrl_overrides |

Definition at line 136 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_gain_ifilt_band[2] |

Definition at line 197 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_icode_high |

Definition at line 161 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_icode_low |

Definition at line 160 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_ifilt |

Definition at line 158 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_int_loop_ctrls |

Definition at line 132 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_int_loop_settings |

Definition at line 128 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_int_loop_settings_two |

Definition at line 129 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_lock_delay |

Definition at line 203 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_lock_min_delay |

Definition at line 204 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_lock_override |

Definition at line 202 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_lockdet |

Definition at line 162 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_lockdet_rate[2] |

Definition at line 194 of file mdssreg.h.

Referenced by dsi_pll_commit().

| uint32_t dsi_phy_pll_qlink_regs::pll_mash_ctrl |

Definition at line 182 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_outdiv |

Definition at line 163 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_outdiv_rate |

Definition at line 193 of file mdssreg.h.

Referenced by dsi_phy_pll_calcandcommit().

| uint32_t dsi_phy_pll_qlink_regs::pll_pass_out_override_one |

Definition at line 165 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_pass_out_override_two |

Definition at line 166 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_pfilt |

Definition at line 157 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_pll_fastlock_en_band |

Definition at line 199 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_pll_gain |

Definition at line 159 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_prop_gain_rate[2] |

Definition at line 195 of file mdssreg.h.

Referenced by dsi_pll_config_hzindep_reg().

| uint32_t dsi_phy_pll_qlink_regs::pll_rate_change |

Definition at line 169 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_spare_and_jpc_overrides |

Definition at line 206 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_ssc_ctrl |

Definition at line 192 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_ssc_mux_ctrl |

Definition at line 184 of file mdssreg.h.

Referenced by dsi_pll_init_val().

| uint32_t dsi_phy_pll_qlink_regs::pll_system_muxes |

Definition at line 135 of file mdssreg.h.

Referenced by dsi_phy_pll_bias_enable().