|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

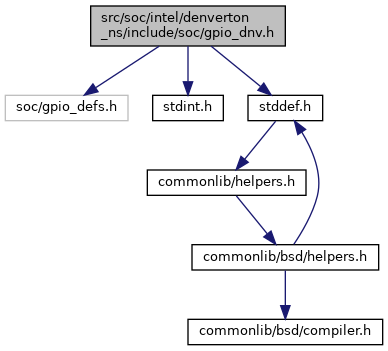

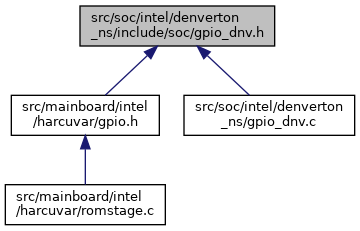

Go to the source code of this file.

Data Structures | |

| struct | GPIO_GROUP_INFO |

| struct | GPIO_CONFIG |

| GPIO configuration structure used for pin programming. More... | |

| struct | dnv_pad_config |

Macros | |

| #define | NO_REGISTER_FOR_PROPERTY (~0u) |

| #define | GPIO_CONF_PAD_MODE_MASK 0xF |

| #define | GPIO_CONF_PAD_MODE_BIT_POS 0 |

| #define | GPIO_CONF_HOST_OWN_MASK 0x3 |

| #define | GPIO_CONF_HOST_OWN_BIT_POS 0 |

| #define | GPIO_CONF_DIR_MASK 0x7 |

| #define | GPIO_CONF_DIR_BIT_POS 0 |

| #define | GPIO_CONF_INV_MASK 0x18 |

| #define | GPIO_CONF_INV_BIT_POS 3 |

| #define | GPIO_CONF_OUTPUT_MASK 0x3 |

| #define | GPIO_CONF_OUTPUT_BIT_POS 0 |

| #define | GPIO_CONF_INT_ROUTE_MASK 0x1F |

| #define | GPIO_CONF_INT_ROUTE_BIT_POS 0 |

| #define | GPIO_CONF_INT_TRIG_MASK 0xE0 |

| #define | GPIO_CONF_INT_TRIG_BIT_POS 5 |

| #define | GPIO_CONF_RESET_MASK 0x7 |

| #define | GPIO_CONF_RESET_BIT_POS 0 |

| #define | GPIO_CONF_TERM_MASK 0x1F |

| #define | GPIO_CONF_TERM_BIT_POS 0 |

| #define | GPIO_CONF_PADTOL_MASK 0x60 |

| #define | GPIO_CONF_PADTOL_BIT_POS 5 |

| #define | GPIO_CONF_LOCK_MASK 0x7 |

| #define | GPIO_CONF_LOCK_BIT_POS 0 |

| #define | GPIO_CONF_RXRAW_MASK 0x3 |

| #define | GPIO_CONF_RXRAW_BIT_POS 0 |

Typedefs | |

| typedef uint32_t | GPIO_PAD |

Enumerations | |

| enum | GPIO_HARDWARE_DEFAULT { GpioHardwareDefault = 0x0 } |

| enum | GPIO_PAD_MODE { GpioPadModeGpio = 0x1 , GpioPadModeNative1 = 0x3 , GpioPadModeNative2 = 0x5 , GpioPadModeNative3 = 0x7 , GpioPadModeNative4 = 0x9 } |

| GPIO Pad Mode. More... | |

| enum | GPIO_HOSTSW_OWN { GpioHostOwnDefault = 0x0 , GpioHostOwnAcpi = 0x1 , GpioHostOwnGpio = 0x3 } |

| Host Software Pad Ownership modes. More... | |

| enum | GPIO_DIRECTION { GpioDirDefault = 0x0 , GpioDirInOut , GpioDirInInvOut = (0x1 | (0x3 << 3)) , GpioDirIn = (0x3 | (0x1 << 3)) , GpioDirInInv = (0x3 | (0x3 << 3)) , GpioDirOut = 0x5 , GpioDirNone = 0x7 } |

| GPIO Direction. More... | |

| enum | GPIO_OUTPUT_STATE { GpioOutDefault = 0x0 , GpioOutLow = 0x1 , GpioOutHigh = 0x3 } |

| GPIO Output State. More... | |

| enum | GPIO_INT_CONFIG { GpioIntDefault = 0x0 , GpioIntDis = 0x1 , GpioIntNmi = 0x3 , GpioIntSmi = 0x5 , GpioIntSci = 0x9 , GpioIntApic = 0x11 , GpioIntLevel = (0x1 << 5) , GpioIntEdge = (0x3 << 5) , GpioIntLvlEdgDis = (0x5 << 5) , GpioIntBothEdge = (0x7 << 5) } |

| GPIO interrupt configuration This setting is applicable only if GPIO is in input mode. More... | |

| enum | GPIO_RESET_CONFIG { GpioResetDefault = 0x0 , GpioResetPwrGood = 0x1 , GpioResetDeep = 0x3 , GpioResetNormal = 0x5 , GpioResetResume = 0x7 } |

| GPIO Power Configuration GPIO_RESET_CONFIG allows to set GPIO Reset (used to reset the specified Pad Register fields). More... | |

| enum | GPIO_ELECTRICAL_CONFIG { GpioTermDefault = 0x0 , GpioTermNone = 0x1 , GpioTermWpd5K = 0x5 , GpioTermWpd20K = 0x9 , GpioTermWpu1K = 0x13 , GpioTermWpu2K = 0x17 , GpioTermWpu5K = 0x15 , GpioTermWpu20K = 0x19 , GpioTermWpu1K2K = 0x1B , GpioTermNative = 0x1F , GpioNoTolerance1v8 = (0x1 << 5) , GpioTolerance1v8 = (0x3 << 5) } |

| GPIO Electrical Configuration Set GPIO termination and Pad Tolerance (applicable only for some pads) Field from GpioTermDefault to GpioTermNative can be OR'ed with GpioTolerance1v8. More... | |

| enum | GPIO_LOCK_CONFIG { GpioLockDefault = 0x0 , GpioPadConfigLock = 0x3 , GpioOutputStateLock = 0x5 } |

| GPIO LockConfiguration Set GPIO configuration lock and output state lock GpioLockPadConfig and GpioLockOutputState can be OR'ed. More... | |

| enum | GPIO_OTHER_CONFIG { GpioRxRaw1Default = 0x0 , GpioRxRaw1Dis = 0x1 , GpioRxRaw1En = 0x3 } |

| Other GPIO Configuration GPIO_OTHER_CONFIG is used for less often settings and for future extensions Supported settings: More... | |

| enum | GPIO_PAD_OWN { GpioPadOwnHost = 0x0 , GpioPadOwnCsme = 0x1 , GpioPadOwnIsh = 0x2 } |

Functions | |

| void | gpio_configure_dnv_pads (const struct dnv_pad_config *gpio, size_t num) |

| #define GPIO_CONF_DIR_BIT_POS 0 |

Definition at line 48 of file gpio_dnv.h.

| #define GPIO_CONF_DIR_MASK 0x7 |

Definition at line 47 of file gpio_dnv.h.

| #define GPIO_CONF_HOST_OWN_BIT_POS 0 |

Definition at line 46 of file gpio_dnv.h.

| #define GPIO_CONF_HOST_OWN_MASK 0x3 |

Definition at line 45 of file gpio_dnv.h.

| #define GPIO_CONF_INT_ROUTE_BIT_POS 0 |

Definition at line 54 of file gpio_dnv.h.

| #define GPIO_CONF_INT_ROUTE_MASK 0x1F |

Definition at line 53 of file gpio_dnv.h.

| #define GPIO_CONF_INT_TRIG_BIT_POS 5 |

Definition at line 56 of file gpio_dnv.h.

| #define GPIO_CONF_INT_TRIG_MASK 0xE0 |

Definition at line 55 of file gpio_dnv.h.

| #define GPIO_CONF_INV_BIT_POS 3 |

Definition at line 50 of file gpio_dnv.h.

| #define GPIO_CONF_INV_MASK 0x18 |

Definition at line 49 of file gpio_dnv.h.

| #define GPIO_CONF_LOCK_BIT_POS 0 |

Definition at line 64 of file gpio_dnv.h.

| #define GPIO_CONF_LOCK_MASK 0x7 |

Definition at line 63 of file gpio_dnv.h.

| #define GPIO_CONF_OUTPUT_BIT_POS 0 |

Definition at line 52 of file gpio_dnv.h.

| #define GPIO_CONF_OUTPUT_MASK 0x3 |

Definition at line 51 of file gpio_dnv.h.

| #define GPIO_CONF_PAD_MODE_BIT_POS 0 |

Definition at line 44 of file gpio_dnv.h.

| #define GPIO_CONF_PAD_MODE_MASK 0xF |

Definition at line 43 of file gpio_dnv.h.

| #define GPIO_CONF_PADTOL_BIT_POS 5 |

Definition at line 62 of file gpio_dnv.h.

| #define GPIO_CONF_PADTOL_MASK 0x60 |

Definition at line 61 of file gpio_dnv.h.

| #define GPIO_CONF_RESET_BIT_POS 0 |

Definition at line 58 of file gpio_dnv.h.

| #define GPIO_CONF_RESET_MASK 0x7 |

Definition at line 57 of file gpio_dnv.h.

| #define GPIO_CONF_RXRAW_BIT_POS 0 |

Definition at line 66 of file gpio_dnv.h.

| #define GPIO_CONF_RXRAW_MASK 0x3 |

Definition at line 65 of file gpio_dnv.h.

| #define GPIO_CONF_TERM_BIT_POS 0 |

Definition at line 60 of file gpio_dnv.h.

| #define GPIO_CONF_TERM_MASK 0x1F |

Definition at line 59 of file gpio_dnv.h.

| #define NO_REGISTER_FOR_PROPERTY (~0u) |

Definition at line 38 of file gpio_dnv.h.

Definition at line 281 of file gpio_dnv.h.

| enum GPIO_DIRECTION |

GPIO Direction.

Definition at line 163 of file gpio_dnv.h.

GPIO Electrical Configuration Set GPIO termination and Pad Tolerance (applicable only for some pads) Field from GpioTermDefault to GpioTermNative can be OR'ed with GpioTolerance1v8.

Definition at line 230 of file gpio_dnv.h.

| Enumerator | |

|---|---|

| GpioHardwareDefault | |

Definition at line 138 of file gpio_dnv.h.

| enum GPIO_HOSTSW_OWN |

Host Software Pad Ownership modes.

| Enumerator | |

|---|---|

| GpioHostOwnDefault | Leave ownership value unmodified. |

| GpioHostOwnAcpi | Set HOST ownership to ACPI. |

| GpioHostOwnGpio | Set HOST ownership to GPIO. |

Definition at line 154 of file gpio_dnv.h.

| enum GPIO_INT_CONFIG |

GPIO interrupt configuration This setting is applicable only if GPIO is in input mode.

GPIO_INT_CONFIG allows to choose which interrupt is generated (IOxAPIC/SCI/SMI/NMI) and how it is triggered (edge or level). Field from GpioIntNmi to GpioIntApic can be OR'ed with GpioIntLevel to GpioIntBothEdgecan to describe an interrupt e.g. GpioIntApic | GpioIntLevel If GPIO is set to cause an SCI then also Gpe is enabled for this pad. Not all GPIO are capable of generating an SMI or NMI interrupt

Definition at line 197 of file gpio_dnv.h.

| enum GPIO_LOCK_CONFIG |

GPIO LockConfiguration Set GPIO configuration lock and output state lock GpioLockPadConfig and GpioLockOutputState can be OR'ed.

| Enumerator | |

|---|---|

| GpioLockDefault | Leave lock setting unmodified. |

| GpioPadConfigLock | Lock Pad Configuration. |

| GpioOutputStateLock | Lock GPIO pad output value. |

Definition at line 250 of file gpio_dnv.h.

| enum GPIO_OTHER_CONFIG |

Other GPIO Configuration GPIO_OTHER_CONFIG is used for less often settings and for future extensions Supported settings:

| Enumerator | |

|---|---|

| GpioRxRaw1Default | Use default input override value. |

| GpioRxRaw1Dis | Don't override input. |

| GpioRxRaw1En | Override input to '1'. |

Definition at line 266 of file gpio_dnv.h.

| enum GPIO_OUTPUT_STATE |

GPIO Output State.

| Enumerator | |

|---|---|

| GpioOutDefault | Leave output value unmodified. |

| GpioOutLow | Set output to low. |

| GpioOutHigh | Set output to high. |

Definition at line 178 of file gpio_dnv.h.

| enum GPIO_PAD_MODE |

GPIO Pad Mode.

| Enumerator | |

|---|---|

| GpioPadModeGpio | |

| GpioPadModeNative1 | |

| GpioPadModeNative2 | |

| GpioPadModeNative3 | |

| GpioPadModeNative4 | |

Definition at line 143 of file gpio_dnv.h.

| enum GPIO_PAD_OWN |

| Enumerator | |

|---|---|

| GpioPadOwnHost | |

| GpioPadOwnCsme | |

| GpioPadOwnIsh | |

Definition at line 275 of file gpio_dnv.h.

| enum GPIO_RESET_CONFIG |

GPIO Power Configuration GPIO_RESET_CONFIG allows to set GPIO Reset (used to reset the specified Pad Register fields).

Definition at line 216 of file gpio_dnv.h.

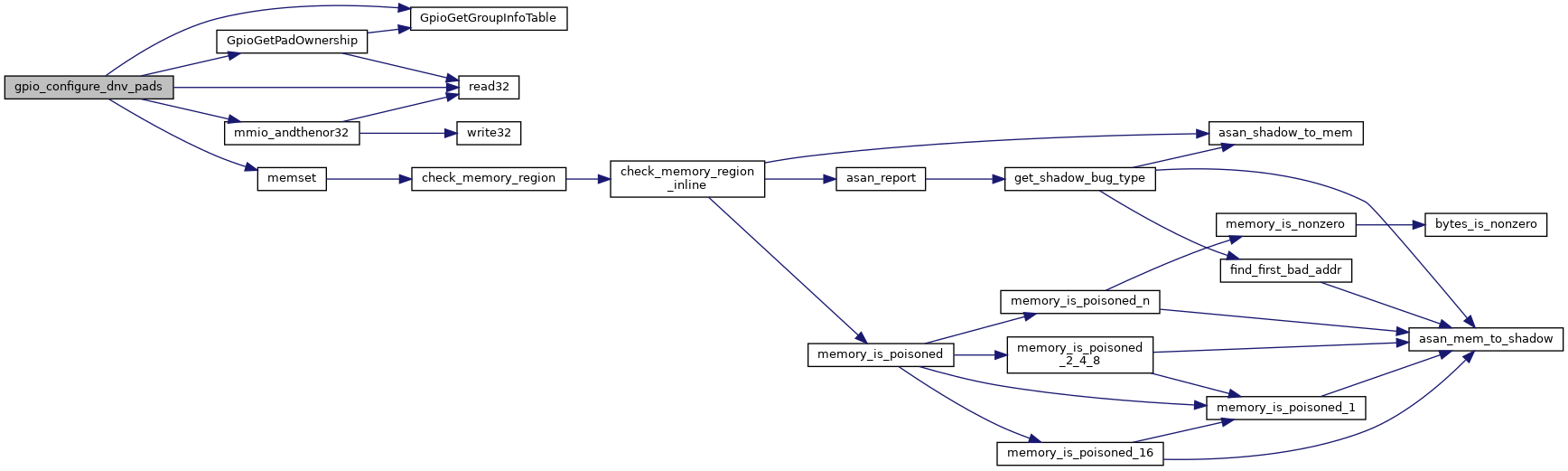

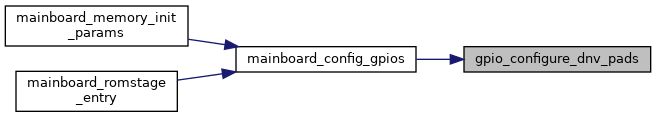

| void gpio_configure_dnv_pads | ( | const struct dnv_pad_config * | gpio, |

| size_t | num | ||

| ) |

Definition at line 120 of file gpio_dnv.c.

References B_PCH_GPIO_PAD_MODE, B_PCH_GPIO_PADTOL, B_PCH_GPIO_RST_CONF, B_PCH_GPIO_RX_APIC_ROUTE, B_PCH_GPIO_RX_LVL_EDG, B_PCH_GPIO_RX_NMI_ROUTE, B_PCH_GPIO_RX_RAW1, B_PCH_GPIO_RX_SCI_ROUTE, B_PCH_GPIO_RX_SMI_ROUTE, B_PCH_GPIO_RXDIS, B_PCH_GPIO_RXINV, B_PCH_GPIO_TERM, B_PCH_GPIO_TX_STATE, B_PCH_GPIO_TXDIS, BIOS_DEBUG, BIOS_ERR, GPIO_CONFIG::Direction, GPIO_CONFIG::ElectricalConfig, GPIO_CONF_DIR_BIT_POS, GPIO_CONF_DIR_MASK, GPIO_CONF_INT_ROUTE_BIT_POS, GPIO_CONF_INT_ROUTE_MASK, GPIO_CONF_INT_TRIG_BIT_POS, GPIO_CONF_INT_TRIG_MASK, GPIO_CONF_INV_BIT_POS, GPIO_CONF_INV_MASK, GPIO_CONF_OUTPUT_BIT_POS, GPIO_CONF_OUTPUT_MASK, GPIO_CONF_PAD_MODE_BIT_POS, GPIO_CONF_PAD_MODE_MASK, GPIO_CONF_PADTOL_BIT_POS, GPIO_CONF_PADTOL_MASK, GPIO_CONF_RESET_BIT_POS, GPIO_CONF_RESET_MASK, GPIO_CONF_RXRAW_BIT_POS, GPIO_CONF_RXRAW_MASK, GPIO_CONF_TERM_BIT_POS, GPIO_CONF_TERM_MASK, GPIO_DNV_GROUP_MIN, GPIO_GET_GROUP_FROM_PAD, GPIO_GET_GROUP_INDEX_FROM_PAD, GPIO_GET_PAD_NUMBER, dnv_pad_config::GpioConfig, GpioGetGroupInfoTable(), GpioGetPadOwnership(), GpioHardwareDefault, GpioIntSci, dnv_pad_config::GpioPad, GpioPadModeGpio, GpioPadOwnCsme, GpioPadOwnHost, GpioPadOwnIsh, GPIO_CONFIG::HostSoftPadOwn, GPIO_CONFIG::InterruptConfig, memset(), mmio_andthenor32(), N_PCH_GPIO_PAD_MODE, N_PCH_GPIO_PADTOL, N_PCH_GPIO_RST_CONF, N_PCH_GPIO_RX_LVL_EDG, N_PCH_GPIO_RX_NMI_ROUTE, N_PCH_GPIO_RX_RAW1, N_PCH_GPIO_RXINV, N_PCH_GPIO_TERM, N_PCH_GPIO_TX_STATE, N_PCH_GPIO_TXDIS, NO_REGISTER_FOR_PROPERTY, NULL, GPIO_CONFIG::OtherSettings, GPIO_CONFIG::OutputState, GPIO_GROUP_INFO::PadCfgOffset, GPIO_CONFIG::PadMode, PCH_PCR_ADDRESS, GPIO_CONFIG::PowerConfig, printk, read32(), and V_PCH_GPIO_GROUP_MAX.

Referenced by mainboard_config_gpios().