|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

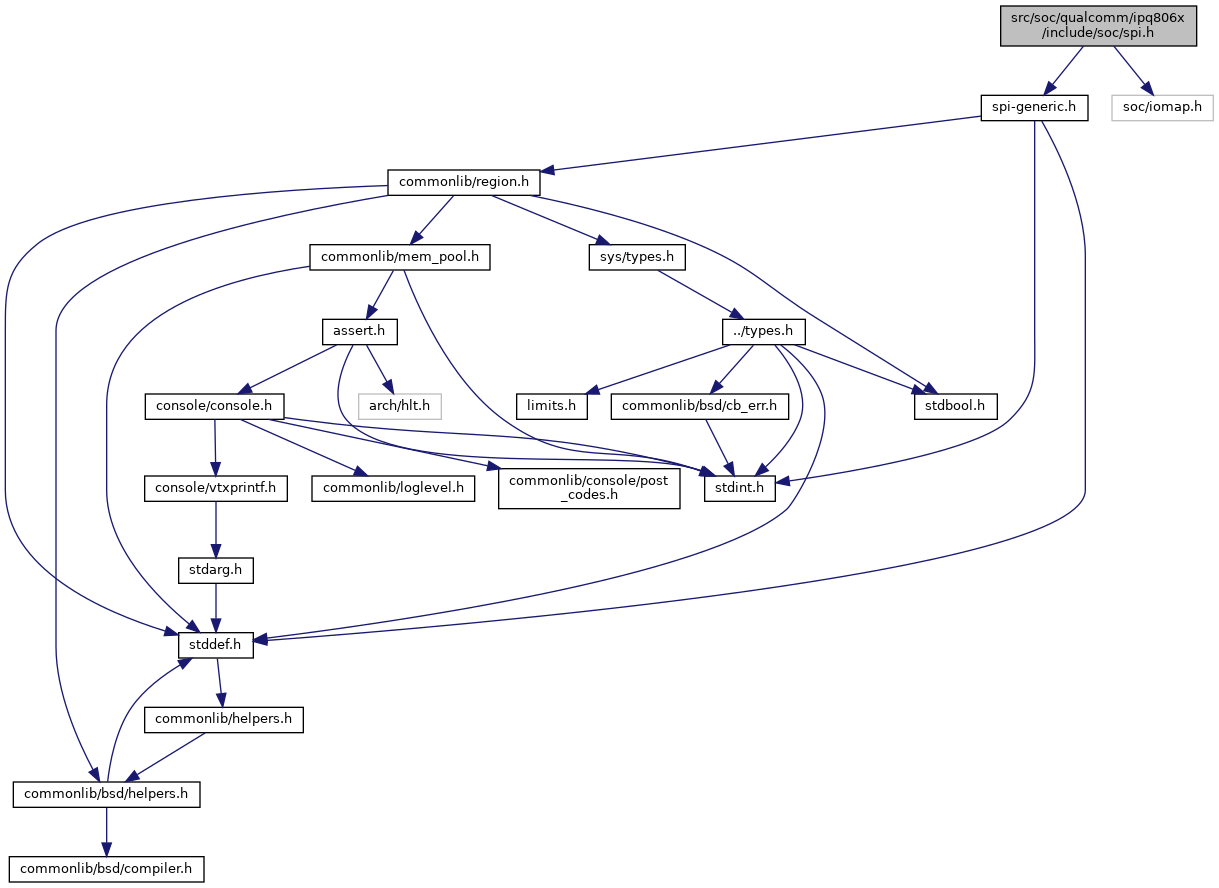

Go to the source code of this file.

Data Structures | |

| struct | gsbi_spi |

| struct | ipq_spi_slave |

| #define CFPB0_HCLK_CTL_REG (CLK_CTL_REG_BASE + 0x00002650) |

| #define CFPB2_HCLK_CTL_REG (CLK_CTL_REG_BASE + 0x00002658) |

| #define CFPB_CLK_NS_REG (CLK_CTL_REG_BASE + 0x0000264c) |

| #define CFPB_SPLITTER_HCLK_CTL_REG (CLK_CTL_REG_BASE + 0x000026e0) |

| #define CLK_HALT_CFPB_STATEB_REG (CLK_CTL_REG_BASE + 0x00002fd0) |

| #define GSBI5_GSBI_CTRL_REG_REG (GSBI5_REG_BASE + 0x00000000) |

| #define GSBI5_QUP_CONFIG_REG (GSBI5_QUP5_REG_BASE + 0x00000000) |

| #define GSBI5_QUP_ERROR_FLAGS_EN_REG (GSBI5_QUP5_REG_BASE + 0x00000020) |

| #define GSBI5_QUP_ERROR_FLAGS_REG (GSBI5_QUP5_REG_BASE + 0x0000001c) |

| #define GSBI5_QUP_IN_FIFO_WORD_CNT_REG (GSBI5_QUP5_REG_BASE + 0x00000214) |

| #define GSBI5_QUP_INPUT_FIFOc_REG | ( | c | ) | (GSBI5_QUP5_REG_BASE + 0x00000218 + 4 * (c)) |

| #define GSBI5_QUP_IO_MODES_REG (GSBI5_QUP5_REG_BASE + 0x00000008) |

| #define GSBI5_QUP_MX_INPUT_COUNT_REG (GSBI5_QUP5_REG_BASE + 0x00000200) |

| #define GSBI5_QUP_MX_OUTPUT_COUNT_REG (GSBI5_QUP5_REG_BASE + 0x00000100) |

| #define GSBI5_QUP_OPERATIONAL_REG (GSBI5_QUP5_REG_BASE + 0x00000018) |

| #define GSBI5_QUP_OUT_FIFO_WORD_CNT_REG (GSBI5_QUP5_REG_BASE + 0x0000010c) |

| #define GSBI5_QUP_OUTPUT_FIFOc_REG | ( | c | ) | (GSBI5_QUP5_REG_BASE + 0x00000110 + 4 * (c)) |

| #define GSBI5_QUP_STATE_REG (GSBI5_QUP5_REG_BASE + 0x00000004) |

| #define GSBI5_QUP_SW_RESET_REG (GSBI5_QUP5_REG_BASE + 0x0000000c) |

| #define GSBI5_REG_BASE ((uint32_t)(GSBI5_BASE + 0x00000000)) |

| #define GSBI5_SPI_CONFIG_REG (GSBI5_QUP5_REG_BASE + 0x00000300) |

| #define GSBI5_SPI_ERROR_FLAGS_EN_REG (GSBI5_QUP5_REG_BASE + 0x0000030c) |

| #define GSBI5_SPI_ERROR_FLAGS_REG (GSBI5_QUP5_REG_BASE + 0x00000308) |

| #define GSBI5_SPI_IO_CONTROL_REG (GSBI5_QUP5_REG_BASE + 0x00000304) |

| #define GSBI6_GSBI_CTRL_REG_REG (GSBI6_REG_BASE + 0x00000000) |

| #define GSBI6_QUP_CONFIG_REG (GSBI6_QUP6_REG_BASE + 0x00000000) |

| #define GSBI6_QUP_ERROR_FLAGS_EN_REG (GSBI6_QUP6_REG_BASE + 0x00000020) |

| #define GSBI6_QUP_ERROR_FLAGS_REG (GSBI6_QUP6_REG_BASE + 0x0000001c) |

| #define GSBI6_QUP_IN_FIFO_WORD_CNT_REG (GSBI6_QUP6_REG_BASE + 0x00000214) |

| #define GSBI6_QUP_INPUT_FIFOc_REG | ( | c | ) | (GSBI6_QUP6_REG_BASE + 0x00000218 + 4 * (c)) |

| #define GSBI6_QUP_IO_MODES_REG (GSBI6_QUP6_REG_BASE + 0x00000008) |

| #define GSBI6_QUP_MX_INPUT_COUNT_REG (GSBI6_QUP6_REG_BASE + 0x00000200) |

| #define GSBI6_QUP_MX_OUTPUT_COUNT_REG (GSBI6_QUP6_REG_BASE + 0x00000100) |

| #define GSBI6_QUP_OPERATIONAL_REG (GSBI6_QUP6_REG_BASE + 0x00000018) |

| #define GSBI6_QUP_OUT_FIFO_WORD_CNT_REG (GSBI6_QUP6_REG_BASE + 0x0000010c) |

| #define GSBI6_QUP_OUTPUT_FIFOc_REG | ( | c | ) | (GSBI6_QUP6_REG_BASE + 0x00000110 + 4 * (c)) |

| #define GSBI6_QUP_STATE_REG (GSBI6_QUP6_REG_BASE + 0x00000004) |

| #define GSBI6_QUP_SW_RESET_REG (GSBI6_QUP6_REG_BASE + 0x0000000c) |

| #define GSBI6_REG_BASE ((uint32_t)(GSBI6_BASE + 0x00000000)) |

| #define GSBI6_SPI_CONFIG_REG (GSBI6_QUP6_REG_BASE + 0x00000300) |

| #define GSBI6_SPI_ERROR_FLAGS_EN_REG (GSBI6_QUP6_REG_BASE + 0x0000030c) |

| #define GSBI6_SPI_ERROR_FLAGS_REG (GSBI6_QUP6_REG_BASE + 0x00000308) |

| #define GSBI6_SPI_IO_CONTROL_REG (GSBI6_QUP6_REG_BASE + 0x00000304) |

| #define GSBI7_GSBI_CTRL_REG_REG (GSBI7_REG_BASE + 0x00000000) |

| #define GSBI7_QUP_CONFIG_REG (GSBI7_QUP7_REG_BASE + 0x00000000) |

| #define GSBI7_QUP_ERROR_FLAGS_EN_REG (GSBI7_QUP7_REG_BASE + 0x00000020) |

| #define GSBI7_QUP_ERROR_FLAGS_REG (GSBI7_QUP7_REG_BASE + 0x0000001c) |

| #define GSBI7_QUP_IN_FIFO_WORD_CNT_REG (GSBI7_QUP7_REG_BASE + 0x00000214) |

| #define GSBI7_QUP_INPUT_FIFOc_REG | ( | c | ) | (GSBI7_QUP7_REG_BASE + 0x00000218 + 4 * (c)) |

| #define GSBI7_QUP_IO_MODES_REG (GSBI7_QUP7_REG_BASE + 0x00000008) |

| #define GSBI7_QUP_MX_INPUT_COUNT_REG (GSBI7_QUP7_REG_BASE + 0x00000200) |

| #define GSBI7_QUP_MX_OUTPUT_COUNT_REG (GSBI7_QUP7_REG_BASE + 0x00000100) |

| #define GSBI7_QUP_OPERATIONAL_REG (GSBI7_QUP7_REG_BASE + 0x00000018) |

| #define GSBI7_QUP_OUT_FIFO_WORD_CNT_REG (GSBI7_QUP7_REG_BASE + 0x0000010c) |

| #define GSBI7_QUP_OUTPUT_FIFOc_REG | ( | c | ) | (GSBI7_QUP7_REG_BASE + 0x00000110 + 4 * (c)) |

| #define GSBI7_QUP_STATE_REG (GSBI7_QUP7_REG_BASE + 0x00000004) |

| #define GSBI7_QUP_SW_RESET_REG (GSBI7_QUP7_REG_BASE + 0x0000000c) |

| #define GSBI7_REG_BASE ((uint32_t)(GSBI7_BASE + 0x00000000)) |

| #define GSBI7_SPI_CONFIG_REG (GSBI7_QUP7_REG_BASE + 0x00000300) |

| #define GSBI7_SPI_ERROR_FLAGS_EN_REG (GSBI7_QUP7_REG_BASE + 0x0000030c) |

| #define GSBI7_SPI_ERROR_FLAGS_REG (GSBI7_QUP7_REG_BASE + 0x00000308) |

| #define GSBI7_SPI_IO_CONTROL_REG (GSBI7_QUP7_REG_BASE + 0x00000304) |

| #define GSBIn_D_VAL_MSK (0xFF << GSBI_D_VAL_SHFT) |

| #define GSBIn_HCLK_CTL_REG | ( | n | ) | (CLK_CTL_REG_BASE + 0x000029c0 + 32 * ((n)-1)) |

| #define GSBIn_M_VAL_MSK (0xFF << GSBI_M_VAL_SHFT) |

| #define GSBIn_N_VAL_MSK (0xFF << GSBI_N_VAL_SHFT) |

| #define GSBIn_PRE_DIV_SEL_MSK (0x3 << GSBI_PRE_DIV_SEL_SHFT) |

| #define GSBIn_QUP_APPS_MD_REG | ( | n | ) | (CLK_CTL_REG_BASE + 0x000029c8 + 32 * ((n)-1)) |

| #define GSBIn_QUP_APPS_NS_REG | ( | n | ) | (CLK_CTL_REG_BASE + 0x000029cc + 32 * ((n)-1)) |

| #define GSBIn_RESET_REG | ( | n | ) | (CLK_CTL_REG_BASE + 0x000029dc + 32 * ((n)-1)) |

| #define QUP5_BASE ((uint32_t)GSBI_QUP5_BASE) |

| #define QUP6_BASE ((uint32_t)GSBI_QUP6_BASE) |

| #define QUP7_BASE ((uint32_t)GSBI_QUP7_BASE) |

| #define SFAB_AHB_S3_FCLK_CTL_REG (CLK_CTL_REG_BASE + 0x0000216c) |

| #define SFAB_CFPB_S_HCLK_CTL_REG (CLK_CTL_REG_BASE + 0x000026c0) |