|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

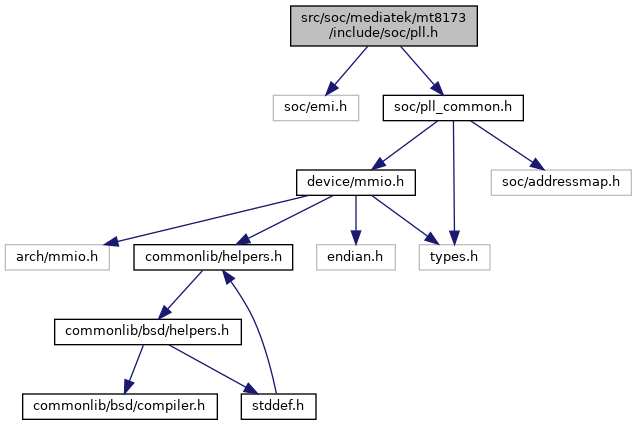

Go to the source code of this file.

Data Structures | |

| struct | mtk_topckgen_regs |

| struct | mtk_apmixed_regs |

Enumerations | |

| enum | { PLL_PWR_ON_DELAY = 5 , PLL_ISO_DELAY = 0 , PLL_EN_DELAY = 40 } |

| enum | { PCW_INTEGER_BITS = 7 } |

| enum | { ARMCA15PLL_HZ = 851500 * KHz , ARMCA7PLL_HZ = 1105 * MHz , MAINPLL_HZ = 1092 * MHz , UNIVPLL_HZ = 1248 * MHz , MMPLL_HZ = 455 * MHz , MSDCPLL_HZ = 800 * MHz , VENCPLL_HZ = 660 * MHz , TVDPLL_HZ = 1782 * MHz , MPLL_HZ = 1456 * MHz , VCODECPLL_HZ = 1104 * MHz , LVDSPLL_HZ = 150 * MHz , MSDCPLL2_HZ = 800 * MHz , APLL1_HZ = 180633600 , APLL2_HZ = 196608 * KHz } |

| enum | { AD_HDMITX_CLK_HZ = TVDPLL_HZ / 12 , AD_LVDSPLL_CK_HZ = LVDSPLL_HZ , APLL1_CK_HZ = APLL1_HZ , APLL2_CK_HZ = APLL2_HZ , CLK26M_HZ = 26 * MHz , CLKRTC_EXT_HZ = 32 * KHz , MMPLL_CK_HZ = MMPLL_HZ , MSDCPLL_D4_HZ = MSDCPLL_HZ / 4 , SYSPLL1_D2_HZ = MAINPLL_HZ / 4 , SYSPLL1_D4_HZ = MAINPLL_HZ / 8 , SYSPLL2_D2_HZ = MAINPLL_HZ / 6 , SYSPLL3_D2_HZ = MAINPLL_HZ / 10 , SYSPLL3_D4_HZ = MAINPLL_HZ / 20 , SYSPLL_D2_HZ = MAINPLL_HZ / 2 , TVDPLL_D2_HZ = TVDPLL_HZ / 2 , UNIVPLL1_D2_HZ = UNIVPLL_HZ / 4 , UNIVPLL1_D8_HZ = UNIVPLL_HZ / 16 , UNIVPLL2_D2_HZ = UNIVPLL_HZ / 6 , UNIVPLL2_D4_HZ = UNIVPLL_HZ / 12 , UNIVPLL3_D2_HZ = UNIVPLL_HZ / 10 , UNIVPLL_D52_HZ = UNIVPLL_HZ / 52 , VCODECPLL_CK_HZ = VCODECPLL_HZ / 3 , VENCPLL_D2_HZ = VENCPLL_HZ / 2 } |

| enum | { AXI_HZ = UNIVPLL2_D2_HZ , MEM_HZ = CLK26M_HZ , DDRPHYCFG_HZ = CLK26M_HZ , MM_HZ = VENCPLL_D2_HZ , PWM_HZ = CLK26M_HZ , VDEC_HZ = VCODECPLL_CK_HZ , VENC_HZ = VCODECPLL_CK_HZ , MFG_HZ = MMPLL_CK_HZ , CAMTG_HZ = CLK26M_HZ , UART_HZ = CLK26M_HZ , SPI_HZ = SYSPLL3_D2_HZ , USB20_HZ = UNIVPLL1_D8_HZ , MSDC30_2_HZ = MSDCPLL_D4_HZ , MSDC30_3_HZ = MSDCPLL_D4_HZ , AUDIO_HZ = CLK26M_HZ , AUD_INTBUS_HZ = SYSPLL1_D4_HZ , PMICSPI_HZ = CLK26M_HZ , SCP_HZ = SYSPLL1_D2_HZ , ATB_HZ = CLK26M_HZ , VENC_LT_HZ = UNIVPLL1_D2_HZ , DPI0_HZ = TVDPLL_D2_HZ , IRDA_HZ = UNIVPLL2_D4_HZ , CCI400_HZ = SYSPLL_D2_HZ , AUD_1_HZ = APLL1_CK_HZ , AUD_2_HZ = APLL2_CK_HZ , MEM_MFG_IN_HZ = MMPLL_CK_HZ , AXI_MFG_IN_HZ = AXI_HZ , SCAM_HZ = SYSPLL3_D2_HZ , SPINFI_IFR_HZ = CLK26M_HZ , HDMI_HZ = AD_HDMITX_CLK_HZ , DPILVDS_HZ = AD_LVDSPLL_CK_HZ , MSDC50_2_H_HZ = SYSPLL2_D2_HZ , HDCP_HZ = SYSPLL3_D4_HZ , HDCP_24M_HZ = UNIVPLL_D52_HZ , RTC_HZ = CLKRTC_EXT_HZ , USB30_HZ = UNIVPLL3_D2_HZ , MSDC50_0_H_HZ = SYSPLL2_D2_HZ , MSDC50_0_HZ = MSDCPLL_D4_HZ , MSDC30_1_HZ = MSDCPLL_D4_HZ } |

Functions | |

| check_member (mtk_topckgen_regs, clk_cfg_0, 0x40) | |

| check_member (mtk_topckgen_regs, clk_cfg_8, 0x100) | |

| check_member (mtk_topckgen_regs, clk_scp_cfg_0, 0x200) | |

| check_member (mtk_topckgen_regs, mbist_cfg_3, 0x314) | |

| check_member (mtk_apmixed_regs, ap_pll_con2, 0x8) | |

| check_member (mtk_apmixed_regs, armca15pll_con0, 0x200) | |

| check_member (mtk_apmixed_regs, msdcpll2_pwr_con0, 0x2fc) | |

| void | mt_pll_post_init (void) |

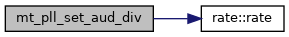

| void | mt_pll_set_aud_div (u32 rate) |

| void | mt_pll_enable_ssusb_clk (void) |

| void | mt_mem_pll_set_clk_cfg (void) |

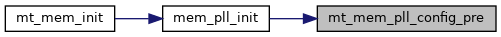

| void | mt_mem_pll_config_pre (const struct mt8173_sdram_params *sdram_params) |

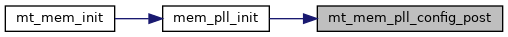

| void | mt_mem_pll_config_post (void) |

| void | mt_mem_pll_mux (void) |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| anonymous enum |

| check_member | ( | mtk_apmixed_regs | , |

| ap_pll_con2 | , | ||

| 0x8 | |||

| ) |

| check_member | ( | mtk_apmixed_regs | , |

| armca15pll_con0 | , | ||

| 0x200 | |||

| ) |

| check_member | ( | mtk_apmixed_regs | , |

| msdcpll2_pwr_con0 | , | ||

| 0x2fc | |||

| ) |

| check_member | ( | mtk_topckgen_regs | , |

| clk_cfg_0 | , | ||

| 0x40 | |||

| ) |

| check_member | ( | mtk_topckgen_regs | , |

| clk_cfg_8 | , | ||

| 0x100 | |||

| ) |

| check_member | ( | mtk_topckgen_regs | , |

| clk_scp_cfg_0 | , | ||

| 0x200 | |||

| ) |

| check_member | ( | mtk_topckgen_regs | , |

| mbist_cfg_3 | , | ||

| 0x314 | |||

| ) |

Definition at line 439 of file pll.c.

References BIT, mtk_apmixed, and setbits32.

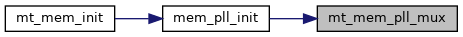

Referenced by mem_pll_init().

| void mt_mem_pll_config_pre | ( | const struct mt8173_sdram_params * | sdram_params | ) |

Definition at line 425 of file pll.c.

References BIT, clrbits32, clrsetbits32, mtk_apmixed, and setbits32.

Referenced by mem_pll_init().

Definition at line 445 of file pll.c.

Referenced by mem_pll_init().

Definition at line 361 of file pll.c.

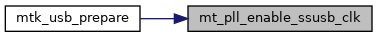

References mtk_apmixed, setbits32, and udelay().

Referenced by mtk_usb_prepare().

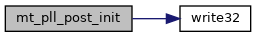

Definition at line 377 of file pll.c.

References clrbits32, mt8173_infracfg, mt8173_infracfg_regs::top_ckdiv1, mt8173_infracfg_regs::top_ckmuxsel, and write32().

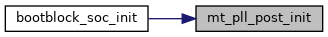

Referenced by bootblock_soc_init().

Definition at line 386 of file pll.c.

References APLL1_CK_HZ, APLL2_CK_HZ, assert, clrbits32, clrsetbits32, mtk_topckgen, rate::rate, and setbits32.

Referenced by configure_audio().