|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

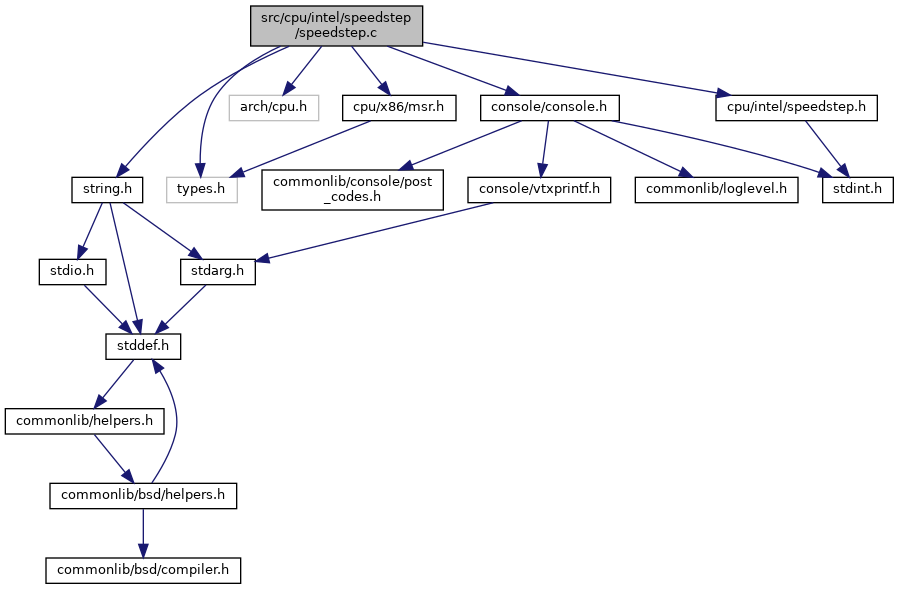

#include <types.h>#include <string.h>#include <arch/cpu.h>#include <cpu/x86/msr.h>#include <console/console.h>#include <cpu/intel/speedstep.h>

Go to the source code of this file.

Functions | |

| static void | speedstep_get_limits (sst_params_t *const params) |

| Gather speedstep limits for current processor. More... | |

| void | speedstep_gen_pstates (sst_table_t *const table) |

| Generate full p-states table from processor parameters. More... | |

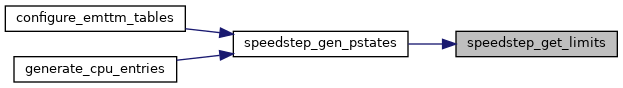

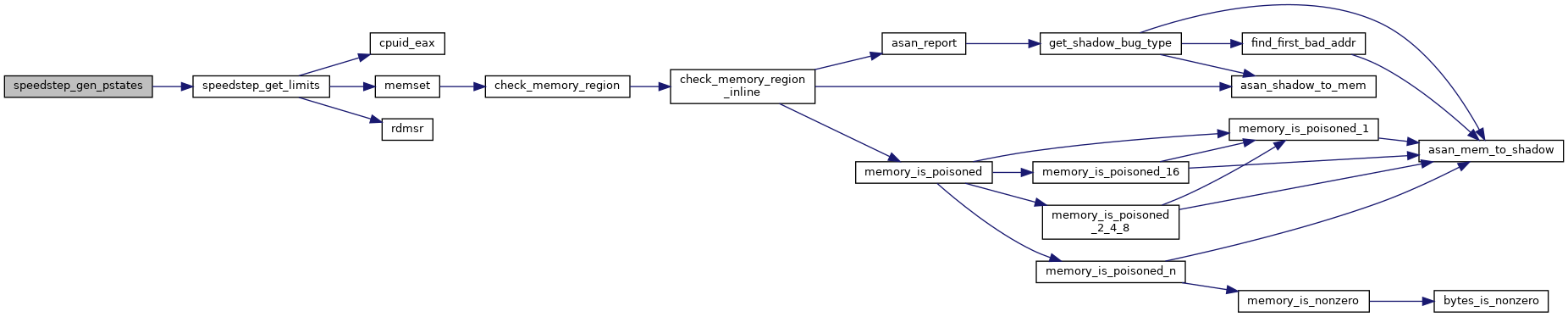

| void speedstep_gen_pstates | ( | sst_table_t *const | table | ) |

Generate full p-states table from processor parameters.

This is generic code and should work at least for Merom and Penryn processors. It is used to generate ACPI tables and configure EMTTM.

Definition at line 101 of file speedstep.c.

References BIOS_INFO, sst_table_t::num_states, params, power, printk, SPEEDSTEP_DOUBLE_RATIO, speedstep_get_limits(), SPEEDSTEP_MAX_NORMAL_STATES, sst_table_t::states, vid, and sst_state_t::vid.

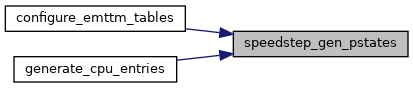

Referenced by configure_emttm_tables(), and generate_cpu_entries().

|

static |

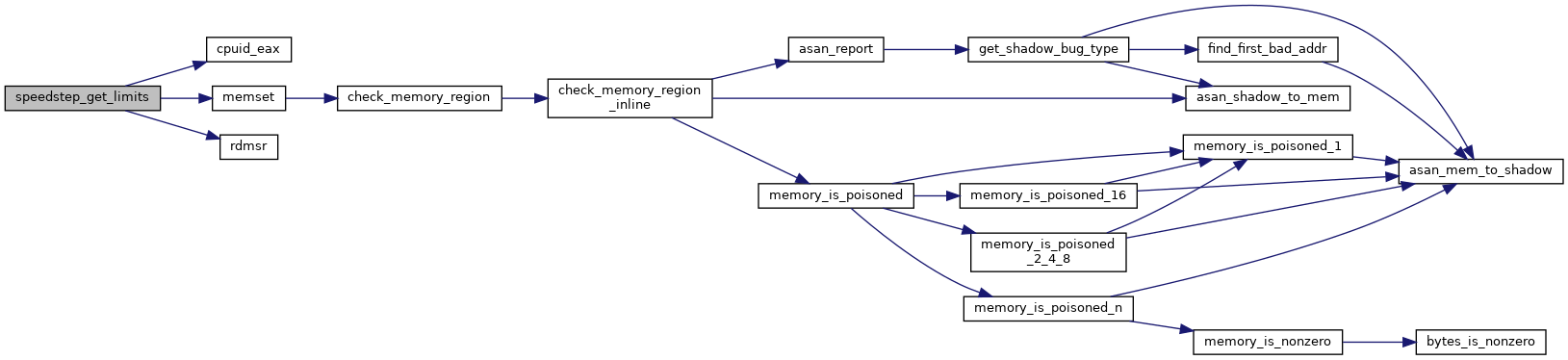

Gather speedstep limits for current processor.

At least power limits are processor type specific. Penryn introduced half steps in bus ratios. Don't know about Atom processors.

Definition at line 16 of file speedstep.c.

References cpu_id, cpuid_eax(), msr_struct::hi, IA32_MISC_ENABLE, IA32_PERF_STATUS, IA32_PLATFORM_ID, msr_struct::lo, memset(), MSR_EXTENDED_CONFIG, MSR_FSB_CLOCK_VCC, MSR_THERM2_CTL, params, rdmsr(), SPEEDSTEP_MAX_POWER_MEROM, SPEEDSTEP_MAX_POWER_PENRYN, SPEEDSTEP_MAX_POWER_YONAH, SPEEDSTEP_MIN_POWER_MEROM, SPEEDSTEP_MIN_POWER_PENRYN, SPEEDSTEP_MIN_POWER_YONAH, SPEEDSTEP_RATIO_NONINT, SPEEDSTEP_RATIO_SHIFT, SPEEDSTEP_RATIO_VALUE_MASK, SPEEDSTEP_SLFM_POWER_MEROM, SPEEDSTEP_SLFM_POWER_PENRYN, SPEEDSTEP_STATE_FROM_MSR, and SPEEDSTEP_VID_MASK.

Referenced by speedstep_gen_pstates().