|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

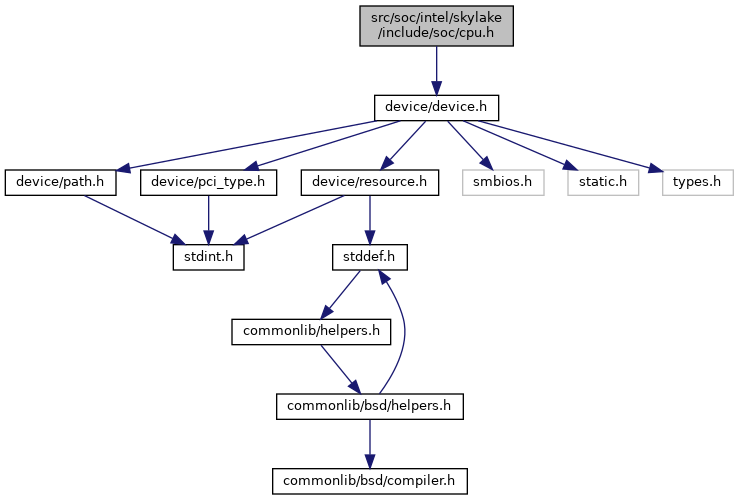

#include <device/device.h>

Go to the source code of this file.

Macros | |

| #define | C_STATE_LATENCY_CONTROL_0_LIMIT 0x4e |

| #define | C_STATE_LATENCY_CONTROL_1_LIMIT 0x76 |

| #define | C_STATE_LATENCY_CONTROL_2_LIMIT 0x94 |

| #define | C_STATE_LATENCY_CONTROL_3_LIMIT 0xfa |

| #define | C_STATE_LATENCY_CONTROL_4_LIMIT 0x14c |

| #define | C_STATE_LATENCY_CONTROL_5_LIMIT 0x3f2 |

| #define | C1_POWER 0x3e8 |

| #define | C3_POWER 0x1f4 |

| #define | C6_POWER 0x15e |

| #define | C7_POWER 0xc8 |

| #define | C8_POWER 0xc8 |

| #define | C9_POWER 0xc8 |

| #define | C10_POWER 0xc8 |

| #define | C_STATE_LATENCY_MICRO_SECONDS(limit, base) (((1 << ((base)*5)) * (limit)) / 1000) |

| #define | C_STATE_LATENCY_FROM_LAT_REG(reg) |

Functions | |

| u32 | cpu_family_model (void) |

| u32 | cpu_stepping (void) |

| int | cpu_is_ult (void) |

| #define C_STATE_LATENCY_FROM_LAT_REG | ( | reg | ) |

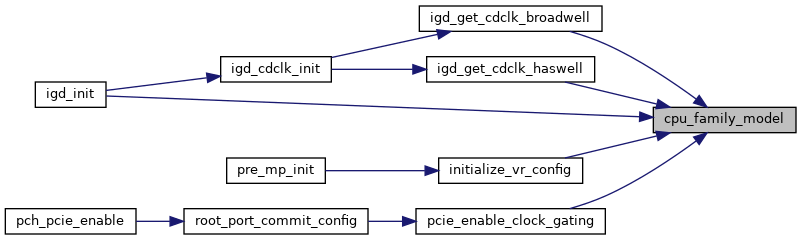

Referenced by igd_get_cdclk_broadwell(), igd_get_cdclk_haswell(), igd_init(), initialize_vr_config(), and pcie_enable_clock_gating().

| int cpu_is_ult | ( | void | ) |

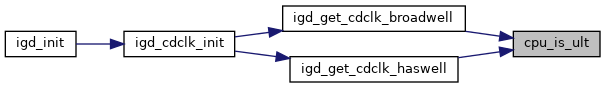

Referenced by igd_get_cdclk_broadwell(), and igd_get_cdclk_haswell().

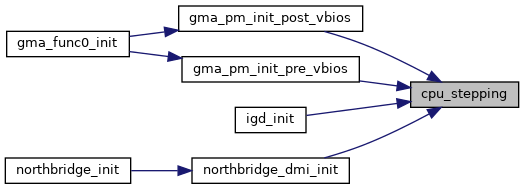

Referenced by gma_pm_init_post_vbios(), gma_pm_init_pre_vbios(), igd_init(), and northbridge_dmi_init().