|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

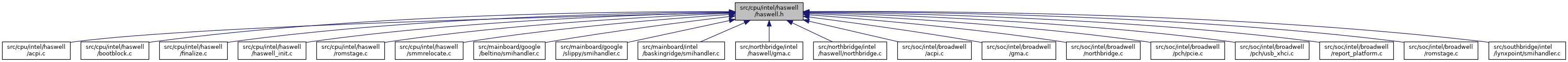

Go to the source code of this file.

Enumerations | |

| enum | { C_STATE_C0 = 0 , C_STATE_C1 = 1 , C_STATE_C1E = 2 , C_STATE_C3 = 3 , C_STATE_C6_SHORT_LAT = 4 , C_STATE_C6_LONG_LAT = 5 , C_STATE_C7_SHORT_LAT = 6 , C_STATE_C7_LONG_LAT = 7 , C_STATE_C7S_SHORT_LAT = 8 , C_STATE_C7S_LONG_LAT = 9 , C_STATE_C8 = 10 , C_STATE_C9 = 11 , C_STATE_C10 = 12 , NUM_C_STATES } |

Functions | |

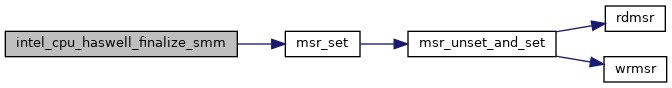

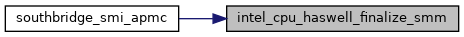

| void | intel_cpu_haswell_finalize_smm (void) |

| void | set_power_limits (u8 power_limit_1_time) |

| int | cpu_config_tdp_levels (void) |

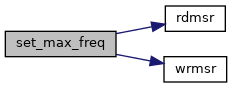

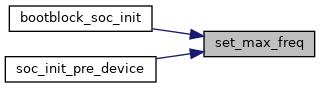

| void | set_max_freq (void) |

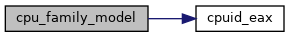

| static u32 | cpu_family_model (void) |

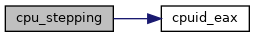

| static u32 | cpu_stepping (void) |

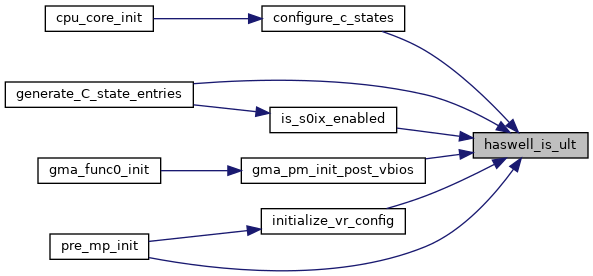

| static int | haswell_is_ult (void) |

| #define C_STATE_LATENCY_FROM_LAT_REG | ( | reg | ) |

| #define SMM_CPU_SVRSTR_MASK (1 << (SMM_CPU_SVRSTR_BIT - 32)) |

| anonymous enum |

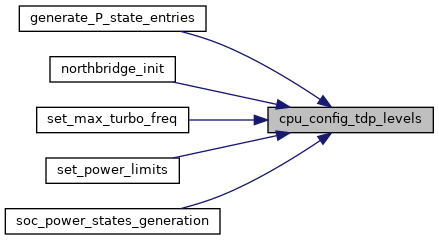

| int cpu_config_tdp_levels | ( | void | ) |

Definition at line 300 of file haswell_init.c.

References msr_struct::hi, MSR_PLATFORM_INFO, and rdmsr().

Referenced by generate_P_state_entries(), northbridge_init(), set_max_turbo_freq(), set_power_limits(), and soc_power_states_generation().

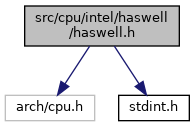

Definition at line 174 of file haswell.h.

References cpuid_eax().

Definition at line 179 of file haswell.h.

References cpuid_eax().

|

inlinestatic |

Definition at line 184 of file haswell.h.

References CONFIG.

Referenced by configure_c_states(), generate_C_state_entries(), gma_pm_init_post_vbios(), initialize_vr_config(), is_s0ix_enabled(), and pre_mp_init().

Definition at line 8 of file finalize.c.

References BIT, MSR_LT_LOCK_MEMORY, and msr_set().

Referenced by southbridge_smi_apmc().

Definition at line 7 of file romstage.c.

References BIOS_DEBUG, CPU_BCLK, msr_struct::hi, IA32_PERF_CTL, msr_struct::lo, MSR_CONFIG_TDP_NOMINAL, MSR_PLATFORM_INFO, printk, rdmsr(), and wrmsr().

Referenced by bootblock_soc_init(), and soc_init_pre_device().

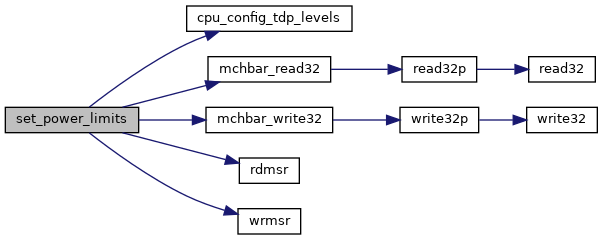

Definition at line 313 of file haswell_init.c.

References ARRAY_SIZE, BIOS_DEBUG, cpu_config_tdp_levels(), msr_struct::hi, msr_struct::lo, MCH_DDR_POWER_LIMIT_HI, MCH_DDR_POWER_LIMIT_LO, MCH_PKG_POWER_LIMIT_HI, MCH_PKG_POWER_LIMIT_LO, mchbar_read32(), mchbar_write32(), MSR_CONFIG_TDP_NOMINAL, MSR_DDR_RAPL_LIMIT, MSR_PKG_POWER_LIMIT, MSR_PKG_POWER_SKU, MSR_PKG_POWER_SKU_UNIT, MSR_PLATFORM_INFO, MSR_TURBO_ACTIVATION_RATIO, PKG_POWER_LIMIT_EN, PKG_POWER_LIMIT_MASK, PKG_POWER_LIMIT_TIME_MASK, PKG_POWER_LIMIT_TIME_SHIFT, PLATFORM_INFO_SET_TDP, power_limit_time_msr_to_sec, power_limit_time_sec_to_msr, printk, rdmsr(), and wrmsr().

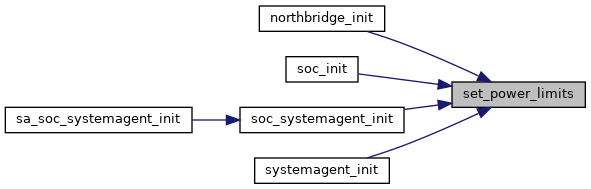

Referenced by northbridge_init(), soc_init(), soc_systemagent_init(), and systemagent_init().