|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

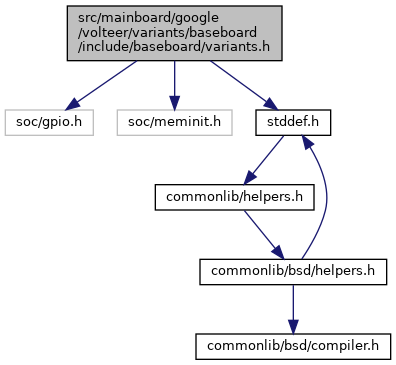

Go to the source code of this file.

Functions | |

| const struct pad_config * | variant_base_gpio_table (size_t *num) |

| const struct pad_config * | variant_early_gpio_table (size_t *num) |

| const struct pad_config * | variant_sleep_gpio_table (u8 slp_typ, size_t *num) |

| const struct pad_config * | variant_override_gpio_table (size_t *num) |

| const struct mb_cfg * | variant_memory_params (void) |

| int | variant_memory_sku (void) |

| void | memcfg_variant_init (FSPM_UPD *mupd) |

| void | variant_devtree_update (void) |

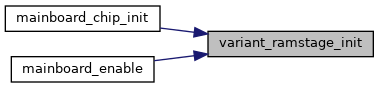

| void | variant_ramstage_init (void) |

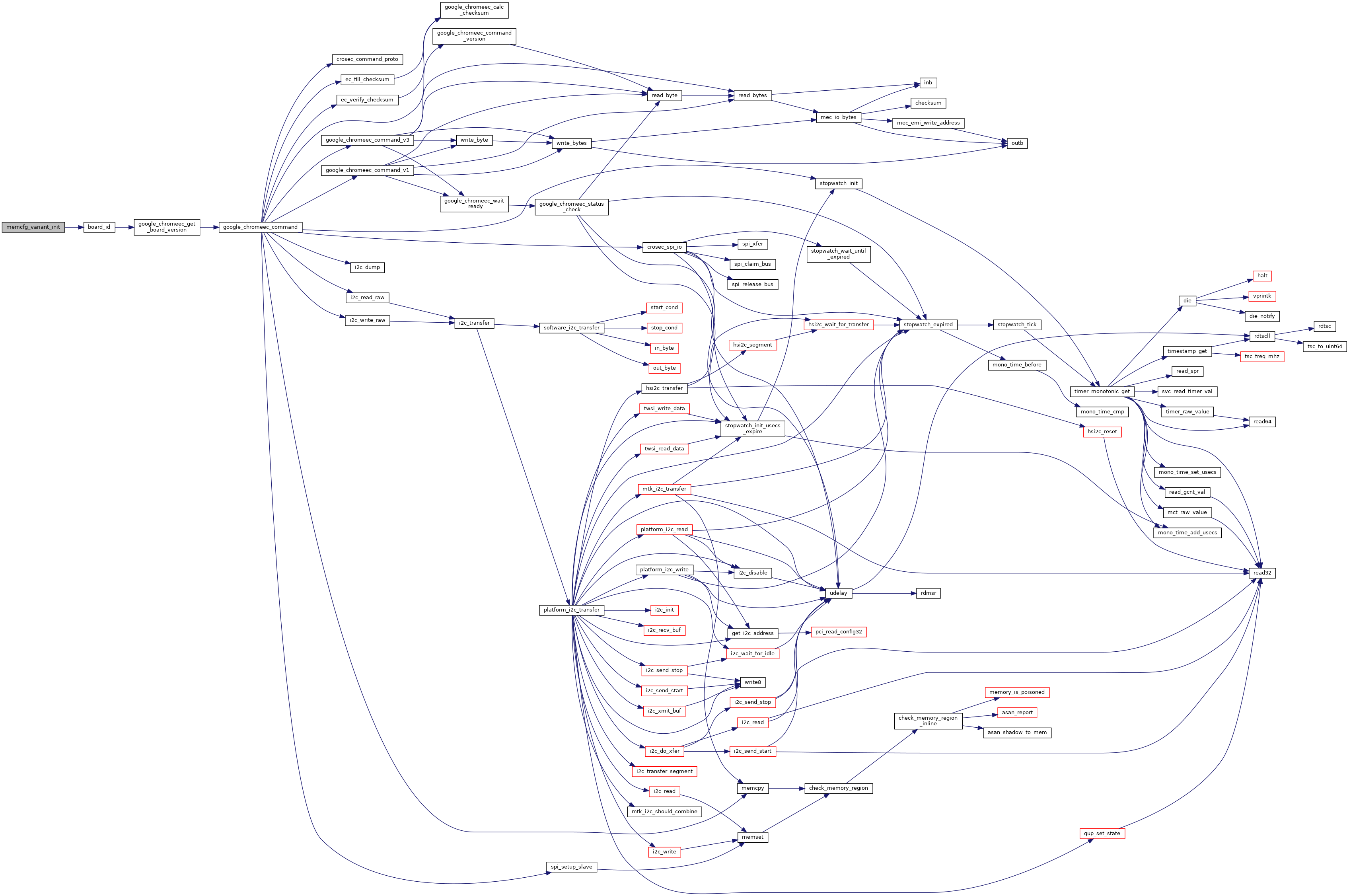

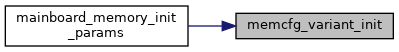

| void memcfg_variant_init | ( | FSPM_UPD * | mupd | ) |

Definition at line 27 of file romstage.c.

References board_id(), and FSP_M_CONFIG.

Referenced by mainboard_memory_init_params().

| const struct pad_config* variant_base_gpio_table | ( | size_t * | num | ) |

Definition at line 86 of file mainboard.c.

| const struct pad_config* variant_early_gpio_table | ( | size_t * | num | ) |

| const struct pad_config* variant_override_gpio_table | ( | size_t * | num | ) |

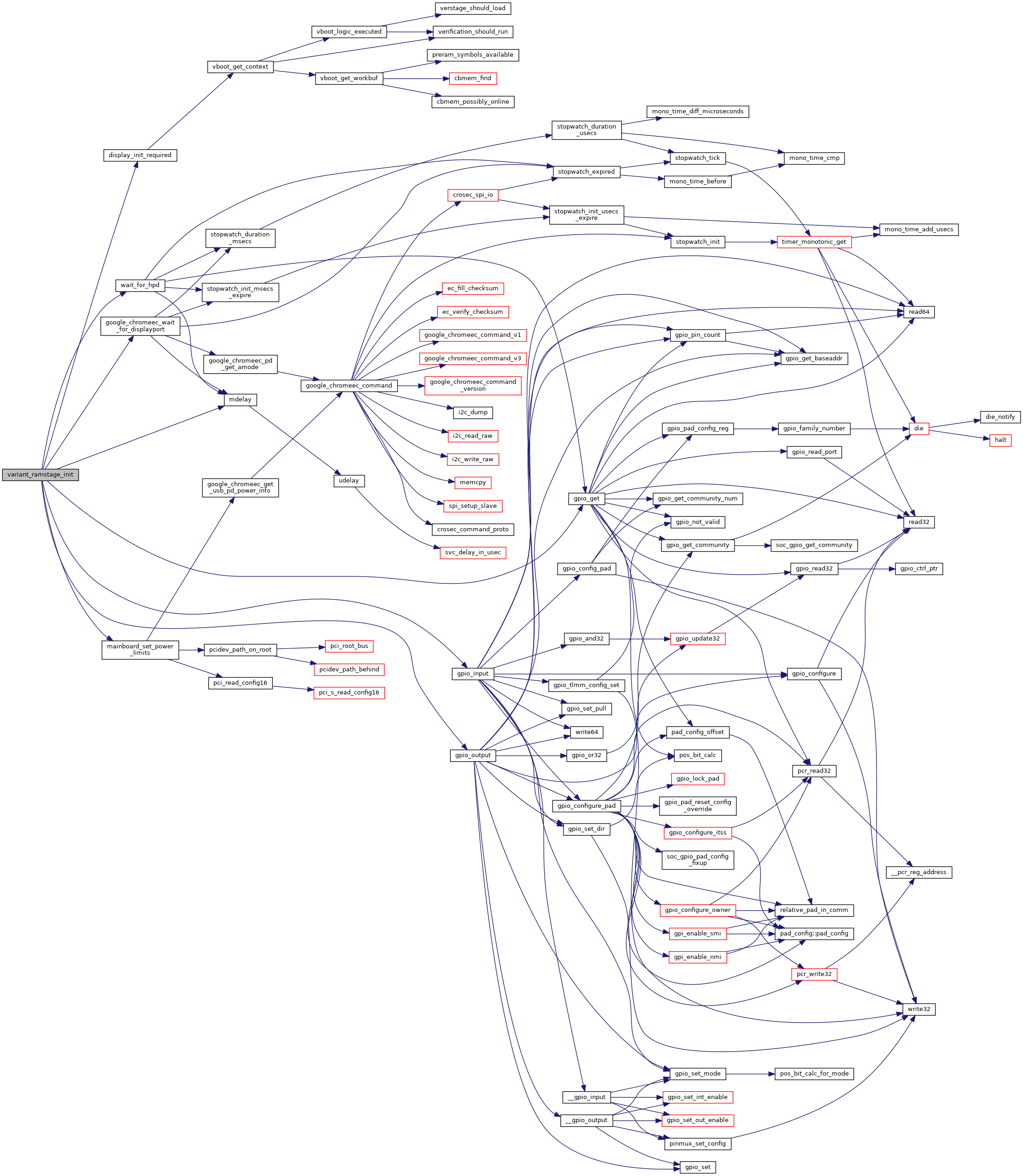

Definition at line 19 of file ramstage.c.

References config_of_soc, display_init_required(), google_chromeec_wait_for_displayport(), GPIO_DP_HPD, gpio_get(), GPIO_HDMI_HPD, gpio_input(), gpio_output(), GPP_A12, GPP_A21, GPP_C11, GPP_C23, mainboard_set_power_limits(), mdelay(), and wait_for_hpd().

Referenced by mainboard_chip_init(), and mainboard_enable().

| const struct pad_config* variant_sleep_gpio_table | ( | u8 | slp_typ, |

| size_t * | num | ||

| ) |

Definition at line 405 of file gpio.c.

References ACPI_S5, ARRAY_SIZE, default_sleep_gpio_table, NULL, and s5_sleep_gpio_table.