|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

|

coreboot

coreboot is an Open Source project aimed at replacing the proprietary BIOS found in most computers.

|

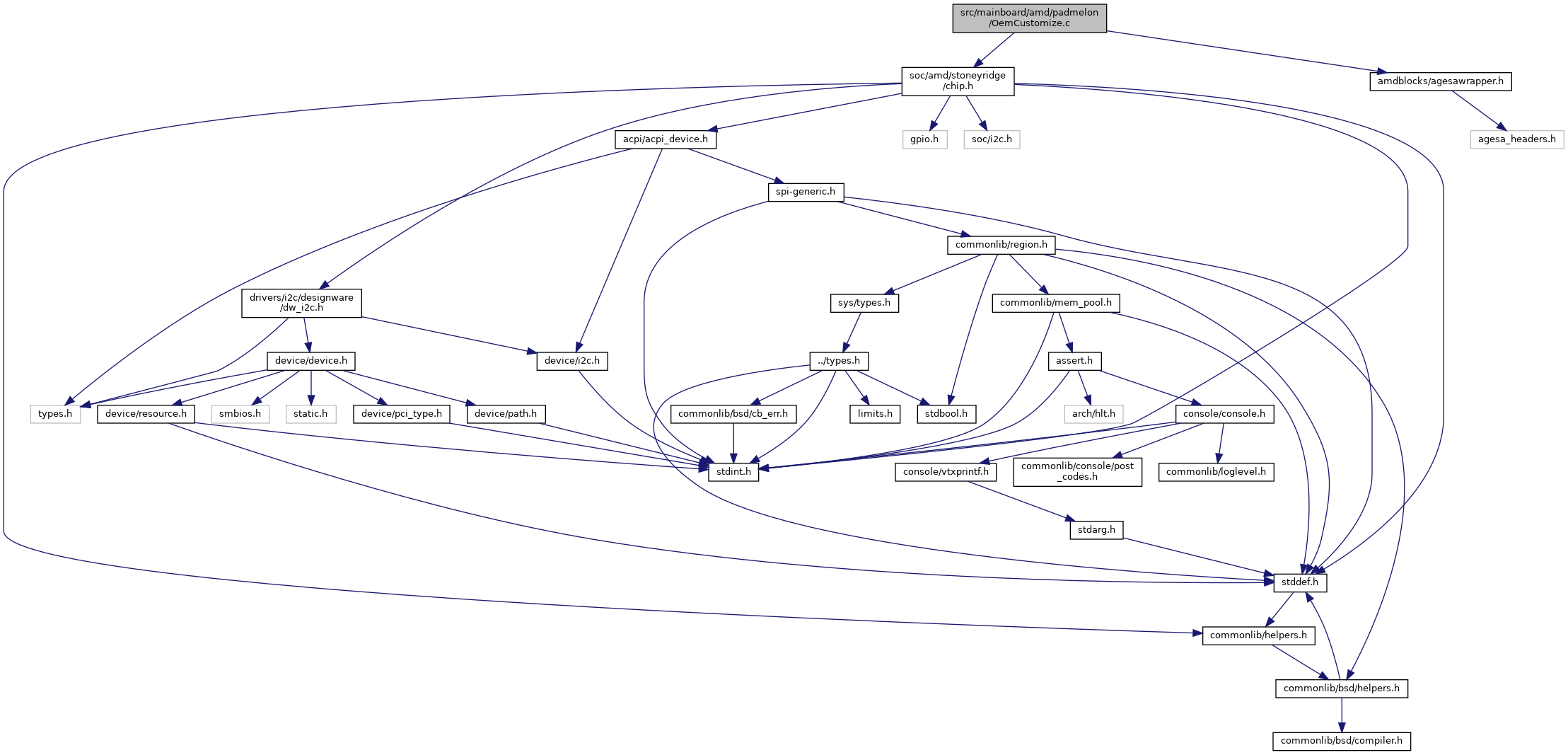

Go to the source code of this file.

Macros | |

| #define | DIMMS_PER_CHANNEL 1 |

Functions | |

| void | OemPostParams (AMD_POST_PARAMS *PostParams) |

Variables | |

| static const PSO_ENTRY | DDR4PlatformMemoryConfiguration [] |

| #define DIMMS_PER_CHANNEL 1 |

Definition at line 6 of file OemCustomize.c.

| void OemPostParams | ( | AMD_POST_PARAMS * | PostParams | ) |

Definition at line 32 of file OemCustomize.c.

References DDR4PlatformMemoryConfiguration.

|

static |

Definition at line 11 of file OemCustomize.c.

Referenced by OemPostParams().